daqrio_top.daqrio_top_arc Architecture Reference

Structural description of RocketIO readout. More...

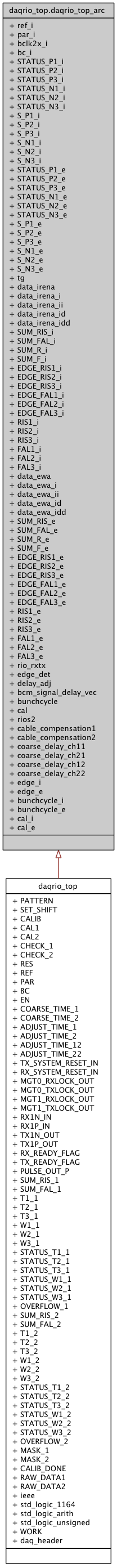

Inheritance diagram for daqrio_top.daqrio_top_arc:

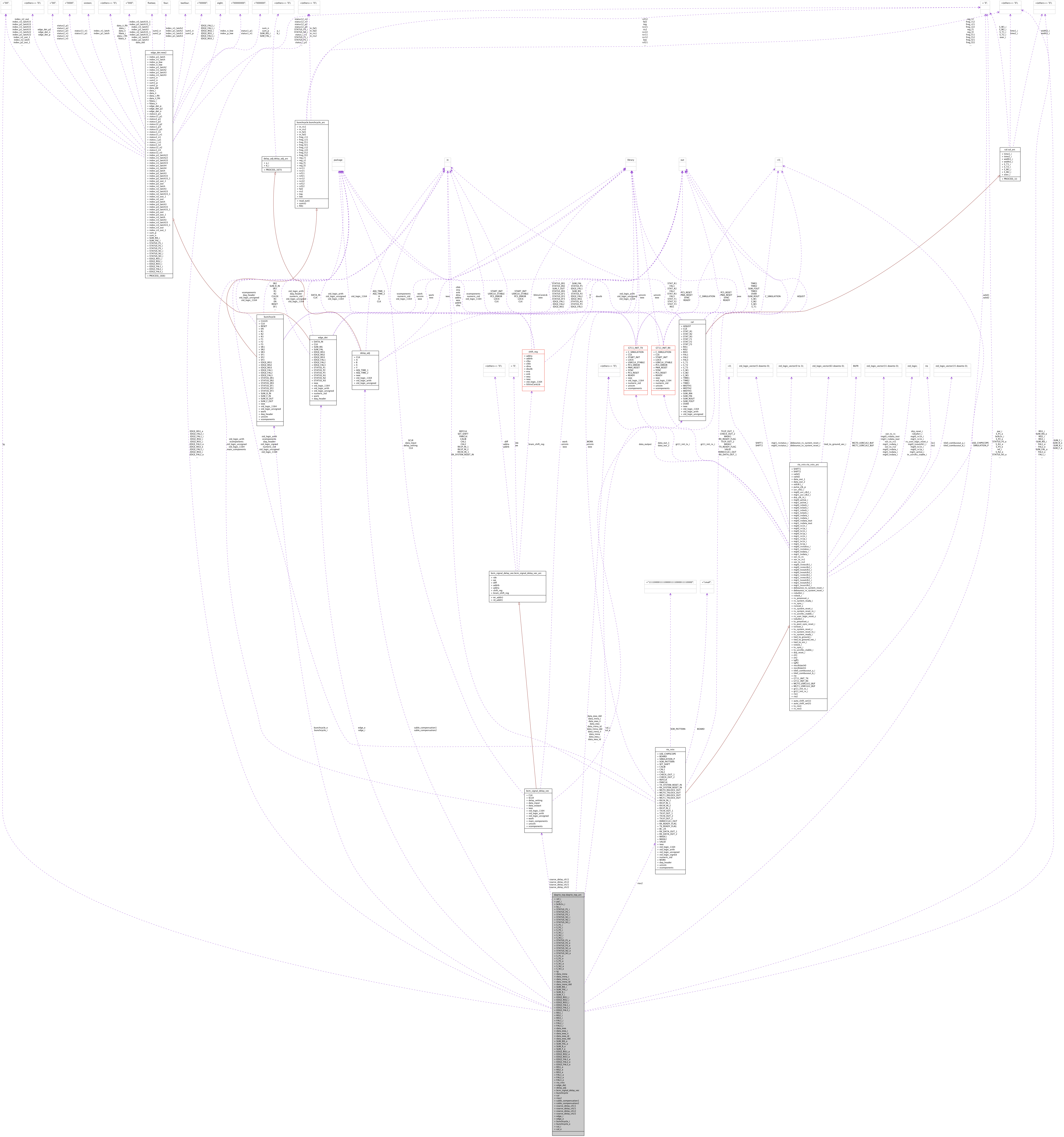

Collaboration diagram for daqrio_top.daqrio_top_arc:

Components | |

| rio_rxtx | <Entity rio_rxtx> |

| RocketIO wrapper. | |

| edge_det | <Entity edge_det> |

| edge detection | |

| delay_adj | <Entity delay_adj> |

| fine delay | |

| bcm_signal_delay_vec | <Entity bcm_signal_delay_vec> |

| coarse delay | |

| bunchcycle | <Entity bunchcycle> |

| bunch structure organizer | |

| cal | <Entity cal> |

| width calculation | |

Signals | |

| ref_i | std_logic := ' 0 ' |

| par_i | std_logic := ' 0 ' |

| bclk2x_i | std_logic := ' 0 ' |

| bc_i | std_logic := ' 0 ' |

| STATUS_P1_i | std_logic := ' 0 ' |

| STATUS_P2_i | std_logic := ' 0 ' |

| STATUS_P3_i | std_logic := ' 0 ' |

| STATUS_N1_i | std_logic := ' 0 ' |

| STATUS_N2_i | std_logic := ' 0 ' |

| STATUS_N3_i | std_logic := ' 0 ' |

| S_P1_i | std_logic := ' 0 ' |

| S_P2_i | std_logic := ' 0 ' |

| S_P3_i | std_logic := ' 0 ' |

| S_N1_i | std_logic := ' 0 ' |

| S_N2_i | std_logic := ' 0 ' |

| S_N3_i | std_logic := ' 0 ' |

| STATUS_P1_e | std_logic := ' 0 ' |

| STATUS_P2_e | std_logic := ' 0 ' |

| STATUS_P3_e | std_logic := ' 0 ' |

| STATUS_N1_e | std_logic := ' 0 ' |

| STATUS_N2_e | std_logic := ' 0 ' |

| STATUS_N3_e | std_logic := ' 0 ' |

| S_P1_e | std_logic := ' 0 ' |

| S_P2_e | std_logic := ' 0 ' |

| S_P3_e | std_logic := ' 0 ' |

| S_N1_e | std_logic := ' 0 ' |

| S_N2_e | std_logic := ' 0 ' |

| S_N3_e | std_logic := ' 0 ' |

| tg | std_logic_vector ( 1 downto 0 ) := " 00 " |

| data_irena | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| data_irena_i | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| data_irena_ii | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| data_irena_id | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| data_irena_idd | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| SUM_RIS_i | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| SUM_FAL_i | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| SUM_R_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| SUM_F_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| EDGE_RIS1_i | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| EDGE_RIS2_i | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| EDGE_RIS3_i | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| EDGE_FAL1_i | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| EDGE_FAL2_i | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| EDGE_FAL3_i | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| RIS1_i | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| RIS2_i | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| RIS3_i | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| FAL1_i | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| FAL2_i | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| FAL3_i | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| data_ewa | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| data_ewa_i | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| data_ewa_ii | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| data_ewa_id | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| data_ewa_idd | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| SUM_RIS_e | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| SUM_FAL_e | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| SUM_R_e | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| SUM_F_e | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| EDGE_RIS1_e | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| EDGE_RIS2_e | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| EDGE_RIS3_e | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| EDGE_FAL1_e | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| EDGE_FAL2_e | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| EDGE_FAL3_e | std_logic_vector ( 4 downto 0 ) := ( others = > ' 0 ' ) |

| RIS1_e | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| RIS2_e | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| RIS3_e | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| FAL1_e | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| FAL2_e | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| FAL3_e | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

Component Instantiations | |

| rios2 | rio_rxtx <Entity rio_rxtx> |

| RocketIO wrapper. | |

| cable_compensation1 | delay_adj <Entity delay_adj> |

| fine delay | |

| cable_compensation2 | delay_adj <Entity delay_adj> |

| fine delay | |

| coarse_delay_ch11 | bcm_signal_delay_vec <Entity bcm_signal_delay_vec> |

| coarse delay | |

| coarse_delay_ch21 | bcm_signal_delay_vec <Entity bcm_signal_delay_vec> |

| coarse delay | |

| coarse_delay_ch12 | bcm_signal_delay_vec <Entity bcm_signal_delay_vec> |

| coarse delay | |

| coarse_delay_ch22 | bcm_signal_delay_vec <Entity bcm_signal_delay_vec> |

| coarse delay | |

| edge_i | edge_det <Entity edge_det> |

| edge detection | |

| edge_e | edge_det <Entity edge_det> |

| edge detection | |

| bunchcycle_i | bunchcycle <Entity bunchcycle> |

| bunch structure organizer | |

| bunchcycle_e | bunchcycle <Entity bunchcycle> |

| bunch structure organizer | |

| cal_i | cal <Entity cal> |

| pulse width calculation | |

| cal_e | cal <Entity cal> |

| pulse width calculation | |

Detailed Description

Structural description of RocketIO readout.Definition at line 115 of file daqrio_top.vhd.

Member Data Documentation

bcm_signal_delay_vec [Component] |

bunchcycle [Component] |

bunchcycle_e bunchcycle [Component Instantiation] |

bunchcycle_i bunchcycle [Component Instantiation] |

cable_compensation1 delay_adj [Component Instantiation] |

cable_compensation2 delay_adj [Component Instantiation] |

cal [Component] |

coarse_delay_ch11 bcm_signal_delay_vec [Component Instantiation] |

coarse_delay_ch12 bcm_signal_delay_vec [Component Instantiation] |

coarse_delay_ch21 bcm_signal_delay_vec [Component Instantiation] |

coarse_delay_ch22 bcm_signal_delay_vec [Component Instantiation] |

delay_adj [Component] |

edge_det [Component] |

rio_rxtx [Component] |

The documentation for this class was generated from the following file: