ATLAS BCM AAA FPGA

3.0

Introduction

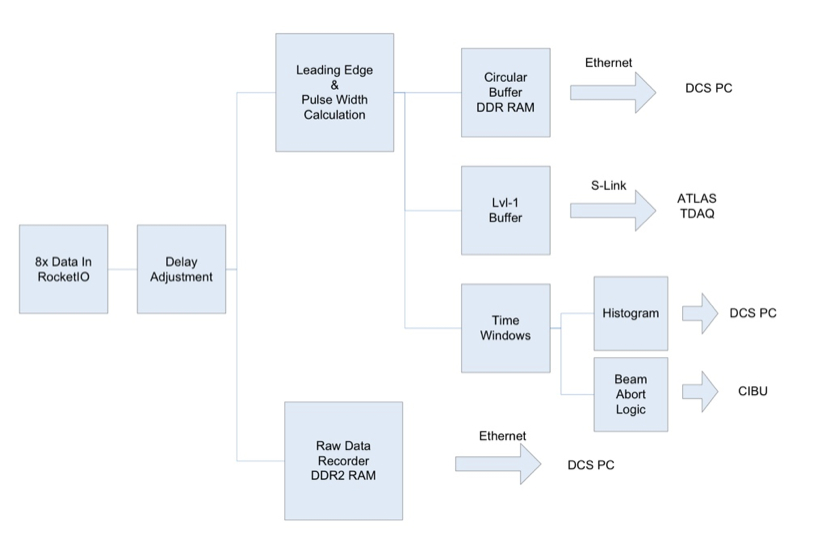

The BCM AAA FPGA is responsible for acquiring the data from the diamond detector modules of the BCM as accurately as possible and determine from those signals the current status of the two LHC beams within the ATLAS experiment. For more information on the BCM as a whole please visit our twiki page: BCM wikiThe data is sampled at 2.56 Gbps with high-speed serial IOs called RocketIOs. A decision over the status of the beam is formed online at all times. For offline analysis the data of about 1k LHC turns is stored in external DDR & DDR2 RAMs. This data is dumped to a PC in case of a beam abort via an Ethernet connection using the UDP protocol. Via Ethernet also status messages are sent to the ATLAS DCS with a frequency of 1 Hz. Furthermore the FPGA is a ROD in the context of the ATLAS TDAQ, meaning it provides data after each Level-1 Accept (L1A) issued by the CTP. For this an interface to HOLA, the ATLAS implementation of the S-Link protocol, exists.

The project is developed on a Xilinx Virtex-4 FX60 ff1152-11 FPGA on the ML410 development board, also by Xilinx.

Below a basic blockdiagram of the full FPGA code is shown:

The datapath is described in a bit more detail in this document

The full code can be browsed through the web interface to the project CVS repository, available here.

Structure

bcm_aaa.vhd the top module of the whole design, contains the main FSMrio2mem.vhd contains all major sub-modules and their interface logic

rios_all.vhd top module of DAQ RocketIOs

ram_user_backend.vhd top module of DDR Ram controller

ddr2_usr_be.vhd top module of DDR2 Ram controller

ethernet_top.vhd top module of Ethernet MAC controller

bcm_rod.vhd top module of ROD formatter & S-Link interface

sata.vhd top module of SATA RocketIOs

The hierarchial structure of the main modules is drawn here as well as for every entity on their respective pages through inheritance diagrams.

Developers

Name Contact Affiliation

D. Dobos NOSPAM_daniel.dobos@cern.ch CERN H. Frais-Koelbl NOSPAM_frais@fhwn.ac.at FHWN B. Macek NOSPAM_bostjan.macek@ijs.si IJS M. Niegl NOSPAM_michael.niegl@cern.ch FHWN, CERN R. Trausmuth NOSPAM_trausmuth@fhwn.ac.at FHWN

Other people providing help through various ways: S. Smith (OSU), A. Kluge (CERN), J. Joseph (LBNL), A. Oltean Karlsson (CES), J. Leinweber (FHWN)A lot of credit also goes to several people at Xilinx for continous support, a few parts of the code that were autogenerated with wizards and for providing us with an excellent chip to work on.

Tools

The following tools were used in the development of this project:- Xilinx ISE Foundation 9.2

- Xilinx Chipscope Pro 9.2

- Xilinx Impact 10.1

- Xilinx Core Generator 9.2

- Mentor Graphics ModelSim SE 6.1h

- XEmacs 21.4.21

- GNU Emacs 22.2.50

- CVS 1.12.13

- Wireshark 0.99.6

License

The code is released under the GNU General Public License (GPL). The license text is available here or can be obtained via the Free Software Foundation (FSF) atFree Software Foundation, Inc.

51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA