rio_rxtx Entity Reference

DAQ-RocketIO wrapper and support logic. More...

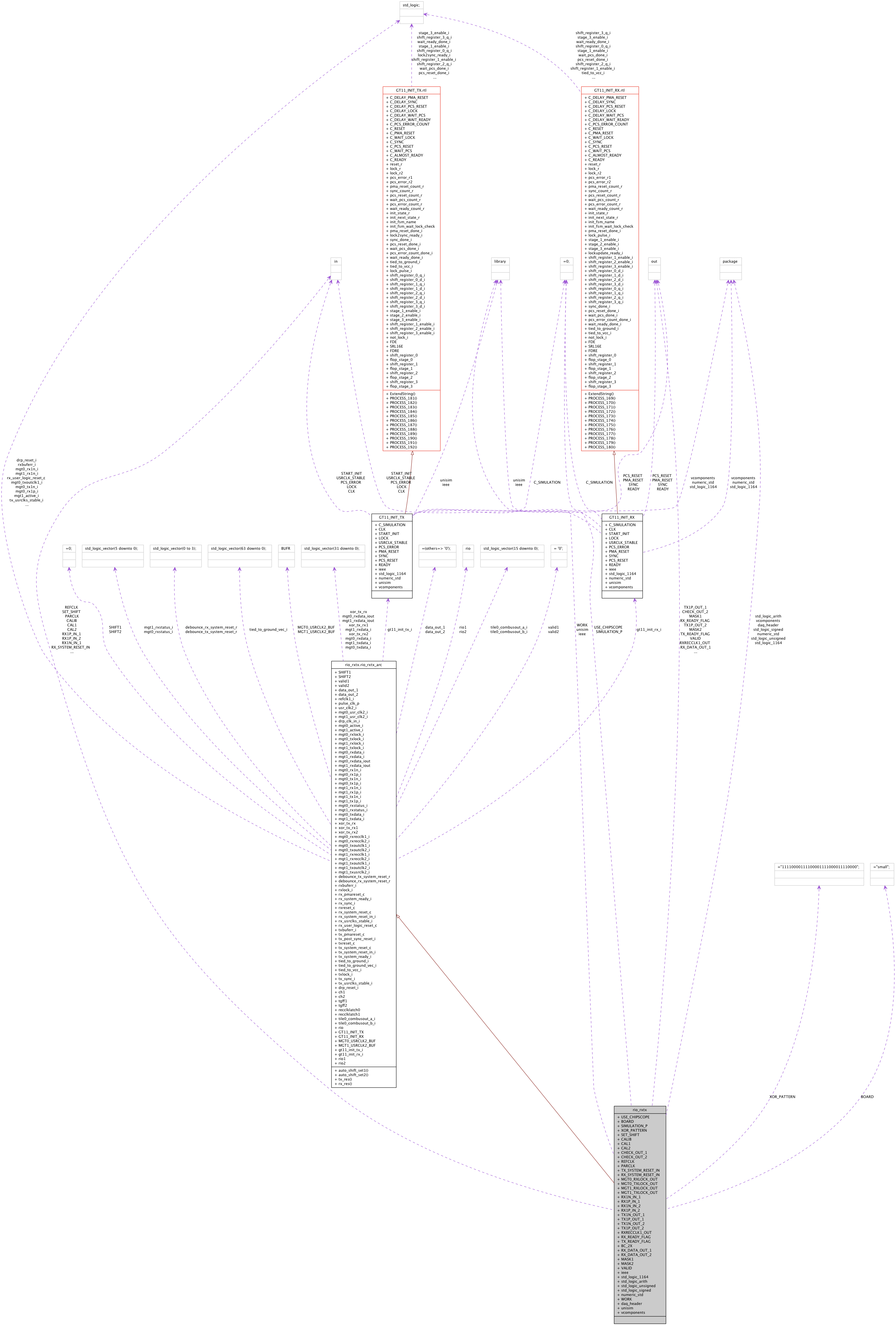

Inheritance diagram for rio_rxtx:

Collaboration diagram for rio_rxtx:

Architectures | |

| rio_rxtx_arc | Architecture |

| DAQ-RocketIO wrapper and support logic. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| WORK | |

| unisim | |

| Library with Xilinx primitives. | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

| std_logic_signed | |

| numeric_std | |

| arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file | |

| daq_header | Package <daq_header> |

| vcomponents | |

| Header with Xilinx primitives. | |

Generics | |

| USE_CHIPSCOPE | integer := 0 |

| Set to 1 to use Chipscope to drive resets. | |

| BOARD | string := " small " |

| Select ML410 or ML405 board. | |

| SIMULATION_P | integer := 0 |

| XOR_PATTERN | std_logic_vector ( 31 downto 0 ) := " 11110000111100001111000011110000 " |

| Pattern for external XOR. | |

Ports | |

| SET_SHIFT | in std_logic_vector ( 7 downto 0 ) |

| manual force of data reco | |

| CALIB | in std_logic |

| start auto-data reco | |

| CAL1 | in std_logic |

| automatic reco after trip | |

| CAL2 | in std_logic |

| automatic reco after trip | |

| CHECK_OUT_1 | out std_logic |

| check reco with OR over all 32 bits | |

| CHECK_OUT_2 | out std_logic |

| check reco with OR over all 32 bits | |

| REFCLK | in std_logic |

| RocketIO reference clock, 4xBC. | |

| PARCLK | in std_logic |

| RocketIO parallel clock, 2xBC. | |

| TX_SYSTEM_RESET_IN | in std_logic |

| tx reset | |

| RX_SYSTEM_RESET_IN | in std_logic |

| rx reset | |

| MGT0_RXLOCK_OUT | out std_logic |

| PLL lock flag. | |

| MGT0_TXLOCK_OUT | out std_logic |

| PLL lock flag. | |

| MGT1_RXLOCK_OUT | out std_logic |

| PLL lock flag. | |

| MGT1_TXLOCK_OUT | out std_logic |

| PLL lock flag. | |

| RX1N_IN_1 | in std_logic |

| serial rx data in | |

| RX1P_IN_1 | in std_logic |

| serial rx data in | |

| RX1N_IN_2 | in std_logic |

| serial rx data in | |

| RX1P_IN_2 | in std_logic |

| serial rx data in | |

| TX1N_OUT_1 | out std_logic |

| serial tx data out | |

| TX1P_OUT_1 | out std_logic |

| serial tx data out | |

| TX1N_OUT_2 | out std_logic |

| serial tx data out | |

| TX1P_OUT_2 | out std_logic |

| serial tx data out | |

| RXRECCLK1_OUT | out std_logic |

| recovered clk out | |

| RX_READY_FLAG | out std_logic |

| flag rx reset procedure finished | |

| TX_READY_FLAG | out std_logic |

| flag tx reset procedure finished | |

| BC_2X | out std_logic |

| parallel clock feed-through | |

| RX_DATA_OUT_1 | out std_logic_vector ( 31 downto 0 ) |

| parallel data out to fabric | |

| RX_DATA_OUT_2 | out std_logic_vector ( 31 downto 0 ) |

| parallel data out to fabric | |

| MASK1 | out std_logic |

| Mask detector data RocketIO-1. | |

| MASK2 | out std_logic |

| Mask detector data RocketIO-1. | |

| VALID | out std_logic |

| Calibration done flag. | |

Detailed Description

DAQ-RocketIO wrapper and support logic.This entity instantiates one RocketIO pair used for data acquisition. Also the support logic (RIO initialzation, data reconstruction) is contained here.

Definition at line 45 of file rio_rxtx.vhd.

Member Data Documentation

BC_2X out std_logic [Port] |

BOARD string := " small " [Generic] |

CAL1 in std_logic [Port] |

CAL2 in std_logic [Port] |

CALIB in std_logic [Port] |

CHECK_OUT_1 out std_logic [Port] |

CHECK_OUT_2 out std_logic [Port] |

ieee library [Library] |

MASK1 out std_logic [Port] |

MASK2 out std_logic [Port] |

MGT0_RXLOCK_OUT out std_logic [Port] |

MGT0_TXLOCK_OUT out std_logic [Port] |

MGT1_RXLOCK_OUT out std_logic [Port] |

MGT1_TXLOCK_OUT out std_logic [Port] |

numeric_std package [Package] |

arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file

Definition at line 33 of file rio_rxtx.vhd.

PARCLK in std_logic [Port] |

REFCLK in std_logic [Port] |

RX1N_IN_1 in std_logic [Port] |

RX1N_IN_2 in std_logic [Port] |

RX1P_IN_1 in std_logic [Port] |

RX1P_IN_2 in std_logic [Port] |

RX_DATA_OUT_1 out std_logic_vector ( 31 downto 0 ) [Port] |

RX_DATA_OUT_2 out std_logic_vector ( 31 downto 0 ) [Port] |

RX_READY_FLAG out std_logic [Port] |

RX_SYSTEM_RESET_IN in std_logic [Port] |

RXRECCLK1_OUT out std_logic [Port] |

SET_SHIFT in std_logic_vector ( 7 downto 0 ) [Port] |

std_logic_1164 package [Package] |

std_logic_arith package [Package] |

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 30 of file rio_rxtx.vhd.

TX1N_OUT_1 out std_logic [Port] |

TX1N_OUT_2 out std_logic [Port] |

TX1P_OUT_1 out std_logic [Port] |

TX1P_OUT_2 out std_logic [Port] |

TX_READY_FLAG out std_logic [Port] |

TX_SYSTEM_RESET_IN in std_logic [Port] |

unisim library [Library] |

USE_CHIPSCOPE integer := 0 [Generic] |

VALID out std_logic [Port] |

vcomponents package [Package] |

XOR_PATTERN std_logic_vector ( 31 downto 0 ) := " 11110000111100001111000011110000 " [Generic] |

The documentation for this class was generated from the following file: