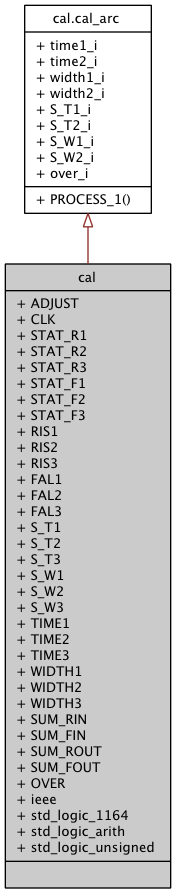

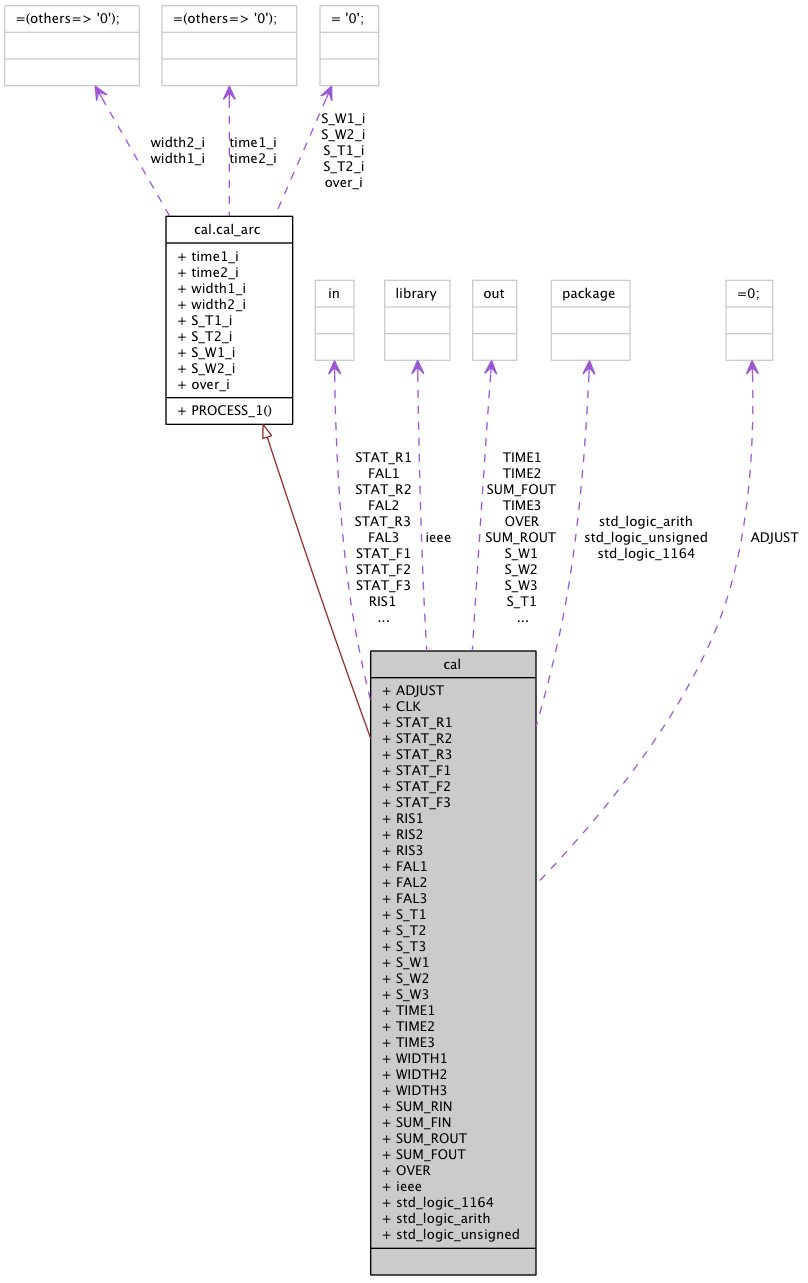

cal Entity Reference

Calculate pulse widths.

More...

List of all members.

|

Architectures |

| cal_arc | Architecture |

| | Calculate pulse widths. More...

|

Libraries |

| ieee | |

| | standard IEEE library

|

Packages |

| std_logic_1164 | |

| | std_logic definitions, see file

|

| std_logic_arith | |

| | arithmetic operations on std_logic datatypes, see file

|

| std_logic_unsigned | |

| | unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

|

Generics |

| ADJUST | := 0 |

| | delay adjust, deprecated

|

Ports |

| CLK | in |

| | Clock.

|

| STAT_R1 | in |

| | Status rising edge1.

|

| STAT_R2 | in |

| | Status rising edge2.

|

| STAT_R3 | in |

| | Status rising edge3.

|

| STAT_F1 | in |

| | Status falling edge1.

|

| STAT_F2 | in |

| | Status falling edge2.

|

| STAT_F3 | in |

| | Status falling edge3.

|

| RIS1 | in ( 5 downto 0 ) |

| | rising edge1

|

| RIS2 | in ( 5 downto 0 ) |

| | rising edge2

|

| RIS3 | in ( 5 downto 0 ) |

| | rising edge3

|

| FAL1 | in ( 5 downto 0 ) |

| | falling edge1

|

| FAL2 | in ( 5 downto 0 ) |

| | falling edge2

|

| FAL3 | in ( 5 downto 0 ) |

| | falling edge3

|

| S_T1 | out |

| | Status time1.

|

| S_T2 | out |

| | Status time2.

|

| S_T3 | out |

| | Status time3.

|

| S_W1 | out |

| | Status width1.

|

| S_W2 | out |

| | Status width1.

|

| S_W3 | out |

| | Status width1.

|

| TIME1 | out ( 7 downto 0 ) |

| | Time1.

|

| TIME2 | out ( 7 downto 0 ) |

| | Time2.

|

| TIME3 | out ( 7 downto 0 ) |

| | Time3.

|

| WIDTH1 | out ( 7 downto 0 ) |

| | Width1.

|

| WIDTH2 | out ( 7 downto 0 ) |

| | Width2.

|

| WIDTH3 | out ( 7 downto 0 ) |

| | Width3.

|

| SUM_RIN | in ( 7 downto 0 ) |

| | Multiplicity rising edge.

|

| SUM_FIN | in ( 7 downto 0 ) |

| | Multiplicity falling edge.

|

| SUM_ROUT | out ( 7 downto 0 ) |

| | Multiplicity rising edge latched.

|

| SUM_FOUT | out ( 7 downto 0 ) |

| | Multiplicity falling edge latched.

|

| OVER | out |

| | Pulse overflowing into next BC flag.

|

Detailed Description

Calculate pulse widths.

Definition at line 33 of file cal.vhd.

Member Data Documentation

Clock.

Definition at line 39 of file cal.vhd.

FAL1 in ( 5 downto 0 ) [Port] |

falling edge1

Definition at line 49 of file cal.vhd.

FAL2 in ( 5 downto 0 ) [Port] |

falling edge2

Definition at line 50 of file cal.vhd.

FAL3 in ( 5 downto 0 ) [Port] |

falling edge3

Definition at line 51 of file cal.vhd.

standard IEEE library

Definition at line 24 of file cal.vhd.

Pulse overflowing into next BC flag.

Definition at line 68 of file cal.vhd.

RIS1 in ( 5 downto 0 ) [Port] |

rising edge1

Definition at line 46 of file cal.vhd.

RIS2 in ( 5 downto 0 ) [Port] |

rising edge2

Definition at line 47 of file cal.vhd.

RIS3 in ( 5 downto 0 ) [Port] |

rising edge3

Definition at line 48 of file cal.vhd.

Status time1.

Definition at line 52 of file cal.vhd.

Status time2.

Definition at line 53 of file cal.vhd.

Status time3.

Definition at line 54 of file cal.vhd.

Status width1.

Definition at line 55 of file cal.vhd.

Status width1.

Definition at line 56 of file cal.vhd.

Status width1.

Definition at line 57 of file cal.vhd.

Status falling edge1.

Definition at line 43 of file cal.vhd.

Status falling edge2.

Definition at line 44 of file cal.vhd.

Status falling edge3.

Definition at line 45 of file cal.vhd.

Status rising edge1.

Definition at line 40 of file cal.vhd.

Status rising edge2.

Definition at line 41 of file cal.vhd.

Status rising edge3.

Definition at line 42 of file cal.vhd.

std_logic definitions, see file

Definition at line 26 of file cal.vhd.

arithmetic operations on std_logic datatypes, see file

Definition at line 28 of file cal.vhd.

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 30 of file cal.vhd.

Multiplicity falling edge.

Definition at line 65 of file cal.vhd.

Multiplicity falling edge latched.

Definition at line 67 of file cal.vhd.

Multiplicity rising edge latched.

Definition at line 66 of file cal.vhd.

TIME1 out ( 7 downto 0 ) [Port] |

Time1.

Definition at line 58 of file cal.vhd.

TIME2 out ( 7 downto 0 ) [Port] |

Time2.

Definition at line 59 of file cal.vhd.

TIME3 out ( 7 downto 0 ) [Port] |

Time3.

Definition at line 60 of file cal.vhd.

WIDTH1 out ( 7 downto 0 ) [Port] |

Width1.

Definition at line 61 of file cal.vhd.

WIDTH2 out ( 7 downto 0 ) [Port] |

Width2.

Definition at line 62 of file cal.vhd.

WIDTH3 out ( 7 downto 0 ) [Port] |

Width3.

Definition at line 63 of file cal.vhd.

The documentation for this class was generated from the following file: