bunchcycle Entity Reference

Collects pulse information and groups it per bunch crossing. More...

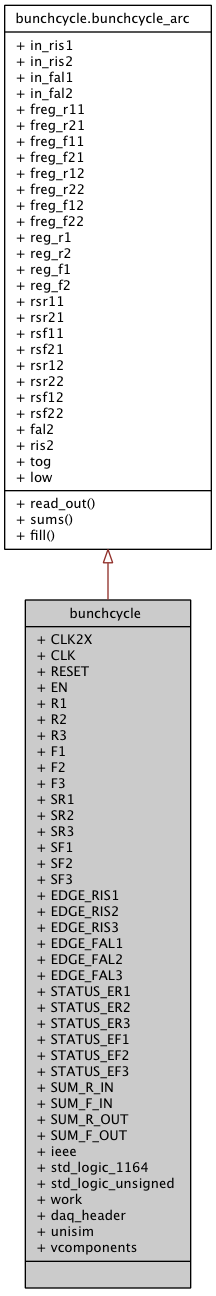

Inheritance diagram for bunchcycle:

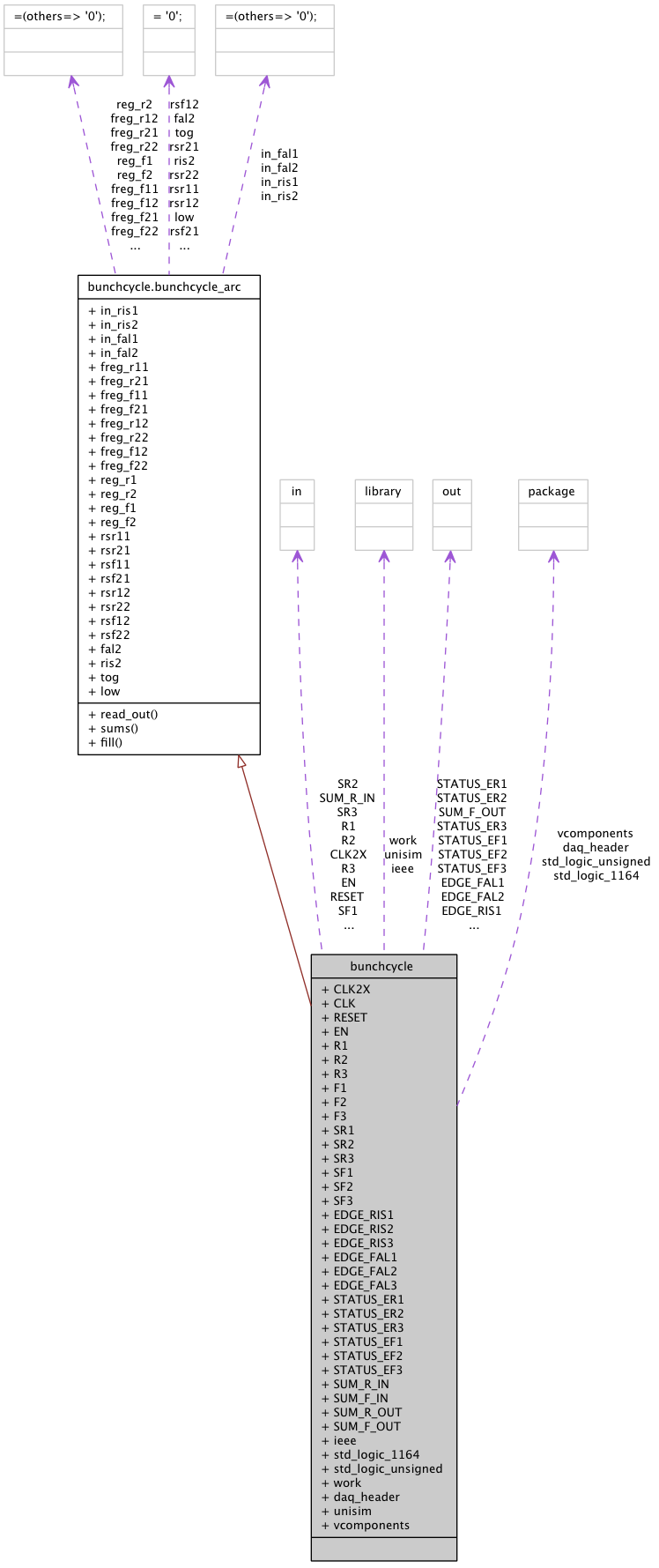

Collaboration diagram for bunchcycle:

Architectures | |

| bunchcycle_arc | Architecture |

| Collects pulse information and groups it per bunch crossing. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| work | |

| unisim | |

| Library with Xilinx primitives. | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

| daq_header | Package <daq_header> |

| vcomponents | |

| Header with Xilinx primitives. | |

Ports | |

| CLK2X | in std_logic |

| 2x bunch clock | |

| CLK | in std_logic |

| bunch clock | |

| RESET | in std_logic |

| reset | |

| EN | in std_logic |

| enable | |

| R1 | in std_logic_vector ( 4 downto 0 ) |

| ris edge 1 | |

| R2 | in std_logic_vector ( 4 downto 0 ) |

| ris edge 2 | |

| R3 | in std_logic_vector ( 4 downto 0 ) |

| ris edge 3 | |

| F1 | in std_logic_vector ( 4 downto 0 ) |

| fal edge 1 | |

| F2 | in std_logic_vector ( 4 downto 0 ) |

| fal edge 2 | |

| F3 | in std_logic_vector ( 4 downto 0 ) |

| fal edge 3 | |

| SR1 | in std_logic |

| valid | |

| SR2 | in std_logic |

| valid | |

| SR3 | in std_logic |

| valid | |

| SF1 | in std_logic |

| valid | |

| SF2 | in std_logic |

| valid | |

| SF3 | in std_logic |

| valid | |

| EDGE_RIS1 | out std_logic_vector ( 5 downto 0 ) |

| ris edge 1 | |

| EDGE_RIS2 | out std_logic_vector ( 5 downto 0 ) |

| ris edge 2 | |

| EDGE_RIS3 | out std_logic_vector ( 5 downto 0 ) |

| ris edge 3 | |

| EDGE_FAL1 | out std_logic_vector ( 5 downto 0 ) |

| fal edge 1 | |

| EDGE_FAL2 | out std_logic_vector ( 5 downto 0 ) |

| fal edge 2 | |

| EDGE_FAL3 | out std_logic_vector ( 5 downto 0 ) |

| fal edge 3 | |

| STATUS_ER1 | out std_logic |

| valid | |

| STATUS_ER2 | out std_logic |

| valid | |

| STATUS_ER3 | out std_logic |

| valid | |

| STATUS_EF1 | out std_logic |

| valid | |

| STATUS_EF2 | out std_logic |

| valid | |

| STATUS_EF3 | out std_logic |

| valid | |

| SUM_R_IN | in std_logic_vector ( 5 downto 0 ) |

| multiplicity ris in | |

| SUM_F_IN | in std_logic_vector ( 5 downto 0 ) |

| multiplicity fal in | |

| SUM_R_OUT | out std_logic_vector ( 7 downto 0 ) |

| multiplicity ris out | |

| SUM_F_OUT | out std_logic_vector ( 7 downto 0 ) |

| multiplicity fal out | |

Detailed Description

Collects pulse information and groups it per bunch crossing.Definition at line 37 of file bunchcycle.vhd.

Member Data Documentation

CLK in std_logic [Port] |

CLK2X in std_logic [Port] |

EDGE_FAL1 out std_logic_vector ( 5 downto 0 ) [Port] |

EDGE_FAL2 out std_logic_vector ( 5 downto 0 ) [Port] |

EDGE_FAL3 out std_logic_vector ( 5 downto 0 ) [Port] |

EDGE_RIS1 out std_logic_vector ( 5 downto 0 ) [Port] |

EDGE_RIS2 out std_logic_vector ( 5 downto 0 ) [Port] |

EDGE_RIS3 out std_logic_vector ( 5 downto 0 ) [Port] |

EN in std_logic [Port] |

F1 in std_logic_vector ( 4 downto 0 ) [Port] |

F2 in std_logic_vector ( 4 downto 0 ) [Port] |

F3 in std_logic_vector ( 4 downto 0 ) [Port] |

ieee library [Library] |

R1 in std_logic_vector ( 4 downto 0 ) [Port] |

R2 in std_logic_vector ( 4 downto 0 ) [Port] |

R3 in std_logic_vector ( 4 downto 0 ) [Port] |

RESET in std_logic [Port] |

SF1 in std_logic [Port] |

SF2 in std_logic [Port] |

SF3 in std_logic [Port] |

SR1 in std_logic [Port] |

SR2 in std_logic [Port] |

SR3 in std_logic [Port] |

STATUS_EF1 out std_logic [Port] |

STATUS_EF2 out std_logic [Port] |

STATUS_EF3 out std_logic [Port] |

STATUS_ER1 out std_logic [Port] |

STATUS_ER2 out std_logic [Port] |

STATUS_ER3 out std_logic [Port] |

std_logic_1164 package [Package] |

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 28 of file bunchcycle.vhd.

SUM_F_IN in std_logic_vector ( 5 downto 0 ) [Port] |

SUM_F_OUT out std_logic_vector ( 7 downto 0 ) [Port] |

SUM_R_IN in std_logic_vector ( 5 downto 0 ) [Port] |

SUM_R_OUT out std_logic_vector ( 7 downto 0 ) [Port] |

unisim library [Library] |

vcomponents package [Package] |

The documentation for this class was generated from the following file: