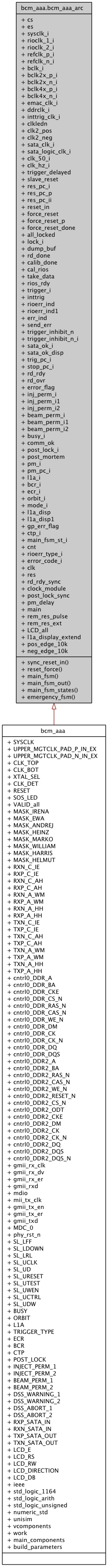

bcm_aaa.bcm_aaa_arc Architecture Reference

top module of BCM AAA design More...

Processes | |

| sync_reset_in | ( sysclk_i ) |

| global submodule reset, hold until main DCMs lock | |

| reset_force | ( clk_hz_i , slave_reset ) |

| force reset after boot for proper initialization | |

| main_fsm | ( clk ) |

| main control FSM | |

| main_fsm_out | ( clk ) |

| main FSM output decoder | |

| main_fsm_states | ( clk ) |

| Decoding main FSM states. | |

| emergency_fsm | ( sysclk_i , RESET ) |

| Emergency FSM running on 100 MHz. | |

Signals | |

| cs | global_states |

| es | err_states |

| sysclk_i | std_logic := ' 0 ' |

| rioclk_1_i | std_logic := ' 0 ' |

| rioclk_2_i | std_logic := ' 0 ' |

| refclk_p_i | std_logic := ' 0 ' |

| refclk_n_i | std_logic := ' 0 ' |

| bclk_i | std_logic := ' 0 ' |

| bclk2x_p_i | std_logic := ' 0 ' |

| bclk2x_n_i | std_logic := ' 0 ' |

| bclk4x_p_i | std_logic := ' 0 ' |

| bclk4x_n_i | std_logic := ' 0 ' |

| emac_clk_i | std_logic := ' 0 ' |

| ddrclk_i | std_logic := ' 0 ' |

| inttrig_clk_i | std_logic := ' 0 ' |

| clkledn | std_logic := ' 0 ' |

| clk2_pos | std_logic := ' 0 ' |

| clk2_neg | std_logic := ' 0 ' |

| sata_clk_i | std_logic := ' 0 ' |

| sata_logic_clk_i | std_logic := ' 0 ' |

| clk_50_i | std_logic := ' 0 ' |

| clk_hz_i | std_logic := ' 0 ' |

| trigger_delayed | std_logic := ' 0 ' |

| slave_reset | std_logic := ' 0 ' |

| res_pc_i | std_logic := ' 0 ' |

| res_pc_p | std_logic := ' 0 ' |

| res_pc_ii | std_logic := ' 0 ' |

| reset_in | std_logic := ' 0 ' |

| force_reset | std_logic := ' 0 ' |

| force_reset_p | std_logic := ' 0 ' |

| force_reset_done | std_logic := ' 0 ' |

| all_locked | std_logic := ' 0 ' |

| lock_i | std_logic := ' 0 ' |

| dump_buf | std_logic := ' 0 ' |

| rd_done | std_logic := ' 0 ' |

| calib_done | std_logic := ' 0 ' |

| cal_rios | std_logic := ' 0 ' |

| take_data | std_logic := ' 0 ' |

| rios_rdy | std_logic := ' 0 ' |

| trigger_i | std_logic := ' 0 ' |

| inttrig | std_logic := ' 0 ' |

| rioerr_ind | std_logic := ' 0 ' |

| rioerr_ind1 | std_logic := ' 0 ' |

| err_ind | std_logic := ' 0 ' |

| send_err | std_logic := ' 0 ' |

| trigger_inhibit_n | std_logic := ' 0 ' |

| trigger_inhibit_n_i | std_logic := ' 0 ' |

| sata_ok_i | std_logic := ' 0 ' |

| sata_ok_disp | std_logic := ' 0 ' |

| trig_pc_i | std_logic := ' 0 ' |

| stop_pc_i | std_logic := ' 0 ' |

| rd_rdy | std_logic := ' 0 ' |

| rd_ovr | std_logic := ' 0 ' |

| error_flag | std_logic := ' 0 ' |

| inj_perm_i | std_logic := ' 0 ' |

| inj_perm_i1 | std_logic := ' 0 ' |

| inj_perm_i2 | std_logic := ' 0 ' |

| beam_perm_i | std_logic := ' 0 ' |

| beam_perm_i1 | std_logic := ' 0 ' |

| beam_perm_i2 | std_logic := ' 0 ' |

| busy_i | std_logic := ' 0 ' |

| comm_ok | std_logic := ' 0 ' |

| post_lock_i | std_logic := ' 0 ' |

| post_mortem | std_logic := ' 0 ' |

| pm_i | std_logic := ' 0 ' |

| pm_pc_i | std_logic := ' 0 ' |

| l1a_i | std_logic := ' 0 ' |

| bcr_i | std_logic := ' 0 ' |

| ecr_i | std_logic := ' 0 ' |

| orbit_i | std_logic := ' 0 ' |

| mode_i | std_logic := ' 0 ' |

| l1a_disp | std_logic := ' 0 ' |

| l1a_disp1 | std_logic := ' 0 ' |

| gp_err_flag | std_logic := ' 0 ' |

| ctp_i | std_logic_vector ( 9 downto 1 ) := ( others = > ' 0 ' ) |

| main_fsm_st_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| cnt | std_logic_vector ( 9 downto 0 ) := ( others = > ' 0 ' ) |

| rioerr_type_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| error_code_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

Component Instantiations | |

| rd_rdy_sync | edge <Entity edge> |

| clock_module | clocks <Entity clocks> |

| post_lock_sync | edge <Entity edge> |

| pm_delay | pmdelay <Entity pmdelay> |

| hold of external post mortem for several orbits | |

| main | rio2mem <Entity rio2mem> |

| rem_res_pulse | edge <Entity edge> |

| rem_res_ext | extend_test <Entity extend_test> |

| LCD_all | LCD <Entity LCD> |

| LCD. | |

| l1a_display_extend | extend_test <Entity extend_test> |

| Status LEDs. | |

| pos_edge_10k | edge <Entity edge> |

| neg_edge_10k | edge <Entity edge> |

Aliases | |

| clk | refclk_p_i |

| res | slave_reset |

Detailed Description

top module of BCM AAA designThis architecture contains the main control FSM as well as an emergency FSM running on 100 MHz in case the external PLL fails. Also the clock-distribution module, the LCD controller & the rio2mem-module containing the major modules of the design are instantiated

Definition at line 264 of file bcm_aaa.vhd.

Member Function Documentation

| emergency_fsm | ( sysclk_i , | |

| RESET ) |

Emergency FSM running on 100 MHz.

purpose: emergency FSM that should run at all times, even if external PLL fails. depends on 100 MHz Oscillator on ML410, if this one goes missing we're fucked :-)

type : sequential

inputs : sysclk

outputs:

Definition at line 595 of file bcm_aaa.vhd.

00595 emergency_fsm : process (sysclk_i, RESET) 00596 begin -- process emergency_fsm 00597 if RESET = '1' then -- asynchronous reset (active high) 00598 es <= err_no; 00599 elsif sysclk_i'event and sysclk_i = '1' then -- rising clock edge 00600 case es is 00601 when err_no => 00602 if CLK_DET = '0' then 00603 es <= err_yes; 00604 else 00605 es <= err_no; 00606 end if; 00607 when err_yes => 00608 null; 00609 when others => 00610 es <= err_yes; 00611 end case; 00612 end if; 00613 end process emergency_fsm;

| main_fsm | ( clk ) |

main control FSM

Global control FSM. Defines the current state of operation of the whole FPGA. First there's a start-up phase, and then in error-free operation either data taking or buffer dump mode. Only operational with external PLL.

Definition at line 411 of file bcm_aaa.vhd.

00411 main_fsm : process(clk) 00412 begin 00413 if clk'event and clk = '1' then 00414 if res = '1' then 00415 cs <= g_reset; 00416 else 00417 case cs is 00418 00419 when g_reset => 00420 cs <= g_idle; 00421 00422 when g_idle => --* wait a bit after reset 00423 cnt <= cnt + 1; 00424 if cnt = "0000011111" then 00425 if kIgnoreRioCal = true then 00426 cs <= g_capture; 00427 else 00428 cs <= g_waitriostartup; 00429 end if; 00430 cnt <= (others => '0'); 00431 else 00432 cs <= g_idle; 00433 end if; 00434 00435 when g_waitriostartup => --* wait for RIOs to lock 00436 if rios_rdy = '1' then 00437 cs <= g_calib; 00438 else 00439 cs <= g_waitriostartup; 00440 end if; 00441 00442 when g_calib => --* wait for RIOs to get ready for valid data taking 00443 if calib_done = '1' then --and sata_ok_i = '1' then 00444 cs <= g_capture; 00445 else 00446 cs <= g_calib; 00447 end if; 00448 00449 when g_capture => 00450 if err_ind = '1' then 00451 cs <= g_error; 00452 elsif pm_i = '1' then 00453 cs <= g_freeze; 00454 elsif trig_pc_i = '1' then 00455 cs <= g_read; 00456 else 00457 cs <= g_capture; 00458 end if; 00459 00460 when g_freeze => 00461 if err_ind = '1' then 00462 cs <= g_error; 00463 elsif trig_pc_i = '1' then 00464 cs <= g_read; 00465 else 00466 cs <= g_freeze; 00467 end if; 00468 00469 when g_read => --* dump buffers to PC 00470 if err_ind = '1' then 00471 cs <= g_error; 00472 elsif rd_done = '1' or stop_pc_i = '1' then 00473 cs <= g_armed; 00474 else 00475 cs <= g_read; 00476 end if; 00477 00478 when g_armed => 00479 if err_ind = '1' then 00480 cs <= g_error; 00481 else 00482 cs <= g_capture; 00483 end if; 00484 00485 when g_error => 00486 cs <= g_error; 00487 00488 when others => 00489 cs <= g_error; 00490 00491 end case; 00492 end if; 00493 end if; 00494 end process main_fsm;

| main_fsm_out | ( clk ) |

main FSM output decoder

Sets signals for controlling all the submodules according to the current state of the main FSM.

Definition at line 505 of file bcm_aaa.vhd.

00505 main_fsm_out : process(clk) 00506 begin 00507 if clk'event and clk = '1' then 00508 if res = '1' then 00509 cal_rios <= '0'; 00510 take_data <= '0'; 00511 dump_buf <= '0'; 00512 rd_rdy <= '0'; 00513 rd_ovr <= '0'; 00514 send_err <= '0'; 00515 error_code_i <= (others => '0'); 00516 else 00517 cal_rios <= '0'; 00518 take_data <= '0'; 00519 dump_buf <= '0'; 00520 rd_rdy <= '0'; 00521 rd_ovr <= '0'; 00522 send_err <= '0'; 00523 00524 case cs is 00525 00526 when g_reset => 00527 null; 00528 when g_waitriostartup => 00529 null; 00530 when g_calib => 00531 cal_rios <= '1'; 00532 when g_idle => 00533 null; 00534 when g_capture => 00535 take_data <= '1'; 00536 when g_freeze => 00537 rd_rdy <= '1'; 00538 take_data <= '0'; 00539 dump_buf <= '0'; 00540 when g_read => 00541 dump_buf <= '1'; 00542 when g_armed => 00543 rd_ovr <= '1'; 00544 dump_buf <= '0'; 00545 when g_error => 00546 if kErr_Msg_En = true then --* mask sending of err msg 00547 send_err <= '1'; 00548 end if; 00549 --* decode different errors 00550 if rioerr_ind1 = '1' then 00551 error_code_i <= "00000001"; 00552 end if; 00553 when others => 00554 null; 00555 end case; 00556 end if; 00557 end if; 00558 end process main_fsm_out;

| main_fsm_states | ( clk ) |

Decoding main FSM states.

This process decodes the states of the main FSM for the DCS status messages using a 6-bit Gray code.

Definition at line 567 of file bcm_aaa.vhd.

00567 main_fsm_states : process (clk) 00568 begin -- process main_fsm_states 00569 if clk'event and clk = '1' then -- rising clock edge 00570 case cs is 00571 when g_waitriostartup => main_fsm_st_i <= "00000001"; 00572 when g_calib => main_fsm_st_i <= "00000011"; 00573 when g_idle => main_fsm_st_i <= "00000010"; 00574 when g_capture => main_fsm_st_i <= "00000110"; 00575 when g_reset => main_fsm_st_i <= "00000111"; 00576 when g_read => main_fsm_st_i <= "00000101"; 00577 when g_error => main_fsm_st_i <= "00000100"; 00578 when g_freeze => main_fsm_st_i <= "00001100"; 00579 when g_armed => main_fsm_st_i <= "00001101"; 00580 when others => main_fsm_st_i <= (others => '0'); 00581 end case; 00582 end if; 00583 end process main_fsm_states;

| reset_force | ( clk_hz_i , | |

| slave_reset ) |

force reset after boot for proper initialization

Definition at line 372 of file bcm_aaa.vhd.

00372 reset_force : process (clk_hz_i, slave_reset) 00373 variable cnt : integer range 0 to 7 := 0; 00374 begin -- process reset_force 00375 if slave_reset = '1' then -- asynchronous reset (active high) 00376 force_reset <= '0'; 00377 -- force_reset_done <= '0'; 00378 cnt := 0; 00379 elsif clk_hz_i'event and clk_hz_i = '1' then -- rising clock edge 00380 if force_reset_done = '0' then 00381 cnt := cnt + 1; 00382 if cnt = 1 then 00383 force_reset <= '1'; 00384 force_reset_done <= '1'; 00385 end if; 00386 else 00387 force_reset <= '0'; 00388 cnt := cnt; 00389 end if; 00390 end if; 00391 end process reset_force;

| sync_reset_in | ( sysclk_i ) |

global submodule reset, hold until main DCMs lock

Definition at line 360 of file bcm_aaa.vhd.

00360 sync_reset_in : process(sysclk_i) 00361 begin 00362 if sysclk_i'event and sysclk_i = '1' then 00363 if reset_in = '1' or all_locked = '0' then 00364 slave_reset <= '1'; 00365 else 00366 slave_reset <= '0'; 00367 end if; 00368 end if; 00369 end process sync_reset_in;

Member Data Documentation

clock_module clocks [Component Instantiation] |

main clock distribution module

Definition at line 618 of file bcm_aaa.vhd.

l1a_display_extend extend_test [Component Instantiation] |

main module containing all the major design parts

Definition at line 676 of file bcm_aaa.vhd.

post_lock_sync edge [Component Instantiation] |

sync of POST_LOCK

Definition at line 653 of file bcm_aaa.vhd.

rd_rdy_sync edge [Component Instantiation] |

pulse internal boot-up reset

Definition at line 394 of file bcm_aaa.vhd.

The documentation for this class was generated from the following file: