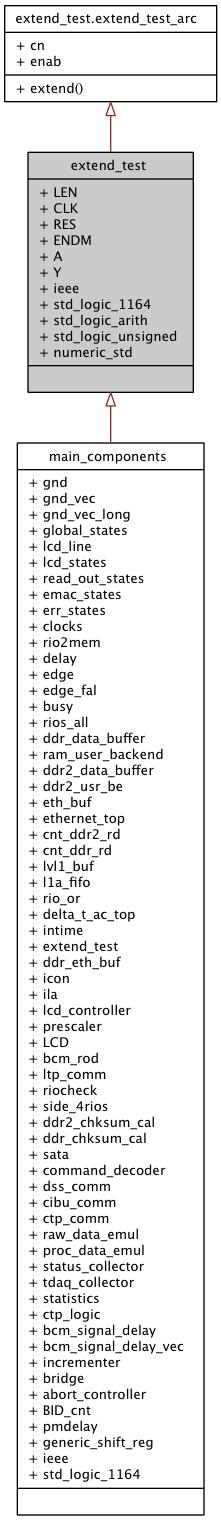

extend_test Entity Reference

Extending a pulse. More...

Architectures | |

| extend_test_arc | Architecture |

| Extending a pulse. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

| numeric_std | |

| arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file | |

Generics | |

| LEN | integer range 0 to 63 := 2 |

| Extension length in clock periods. | |

Ports | |

| CLK | in std_logic |

| Clock. | |

| RES | in std_logic |

| Reset. | |

| ENDM | out std_logic |

| Endmarker. | |

| A | in std_logic |

| Input pulse. | |

| Y | out std_logic |

| Extended output pulse. | |

Detailed Description

Extending a pulse.This Entity extends a pulse by up to 63 clock periods. It also provides an endmarker pulse at the end of the extended output pulse.

Definition at line 38 of file extend_test.vhd.

Member Data Documentation

A in std_logic [Port] |

CLK in std_logic [Port] |

ENDM out std_logic [Port] |

ieee library [Library] |

standard IEEE library

Reimplemented in main_components.

Definition at line 24 of file extend_test.vhd.

LEN integer range 0 to 63 := 2 [Generic] |

numeric_std package [Package] |

arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file

Definition at line 32 of file extend_test.vhd.

RES in std_logic [Port] |

std_logic_1164 package [Package] |

std_logic definitions, see file

Reimplemented in main_components.

Definition at line 26 of file extend_test.vhd.

std_logic_arith package [Package] |

arithmetic operations on std_logic datatypes, see file

Definition at line 28 of file extend_test.vhd.

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 30 of file extend_test.vhd.

Y out std_logic [Port] |

The documentation for this class was generated from the following file: