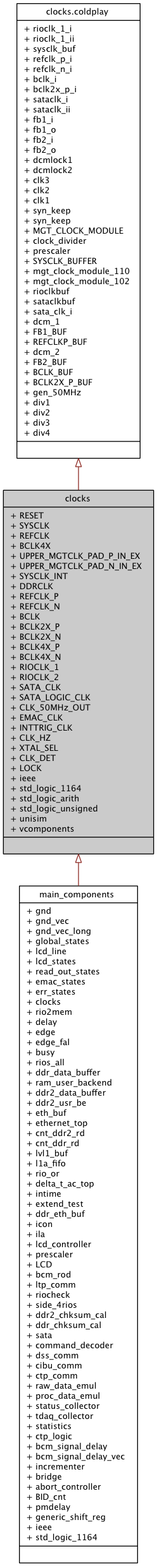

clocks Entity Reference

central clock module

More...

List of all members.

|

Architectures |

| coldplay | Architecture |

| | central clock module More...

|

Libraries |

| ieee | |

| | standard IEEE library

|

| unisim | |

| | Library with Xilinx primitives.

|

Packages |

| std_logic_1164 | |

| | std_logic definitions, see file

|

| std_logic_arith | |

| | arithmetic operations on std_logic datatypes, see file

|

| std_logic_unsigned | |

| | unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

|

| vcomponents | |

| | Header with Xilinx primitives.

|

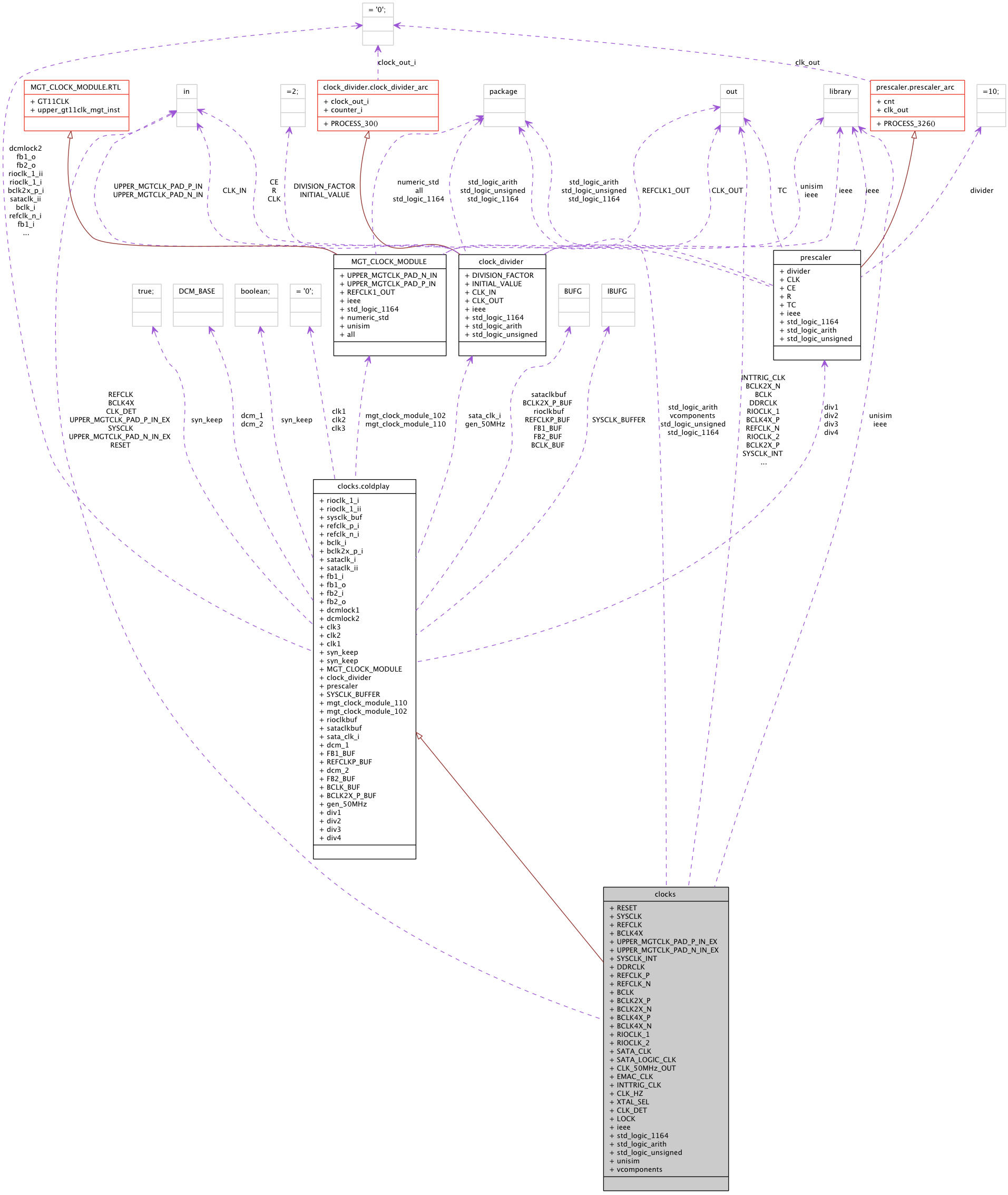

Ports |

| RESET | in |

| | global reset

|

| SYSCLK | in |

| | 100 MHz from ML410

|

| REFCLK | in |

| | 200 MHz in, deprecated

|

| BCLK4X | in |

| | 160 MHz from ext. PLL

|

| UPPER_MGTCLK_PAD_P_IN_EX | in ( 1 downto 0 ) |

| | RIO refclks, positive.

|

| UPPER_MGTCLK_PAD_N_IN_EX | in ( 1 downto 0 ) |

| | RIO refclks, negative.

|

| SYSCLK_INT | out |

| | 100 MHz out

|

| DDRCLK | out |

| | 160 MHz out

|

| REFCLK_P | out |

| | 200 MHz out

|

| REFCLK_N | out |

| | 200 MHz out shifted by

|

| BCLK | out |

| | 40 MHz out

|

| BCLK2X_P | out |

| | 80 MHz out

|

| BCLK2X_N | out |

| | 80 MHz out shifted by  , deprecated , deprecated

|

| BCLK4X_P | out |

| | 160 MHz out

|

| BCLK4X_N | out |

| | 160 MHz out shifted by  , deprecated , deprecated

|

| RIOCLK_1 | out |

| | 160 MHz for RIOs

|

| RIOCLK_2 | out |

| | 160 MHz for RIOs

|

| SATA_CLK | out |

| | 160 MHz for SATA

|

| SATA_LOGIC_CLK | out |

| | 80 MHz for SATA logic

|

| CLK_50MHz_OUT | out |

| | 50 MHz for SATA

|

| EMAC_CLK | out |

| | 100 MHz for EMAC

|

| INTTRIG_CLK | out |

| | slow clock for internal trigger generation

|

| CLK_HZ | out |

| | 1 Hz Clock

|

| XTAL_SEL | out |

| | Select source for external PLL, 0 = BC, 1 = int. Oscillator.

|

| CLK_DET | in |

| | Flag from ext. PLL, 0 = BC not available, 1 = BC present.

|

| LOCK | out |

| | lock flag of all DCMs

|

Detailed Description

central clock module

In this module all input clocks are buffered and put on global clock nets. All the various clocks that are needed for the main modules in the design are derived from the external input clocks

Definition at line 41 of file clocks.vhd.

Member Data Documentation

80 MHz out shifted by  , deprecated

, deprecated

Definition at line 54 of file clocks.vhd.

160 MHz from ext. PLL

Definition at line 45 of file clocks.vhd.

160 MHz out shifted by  , deprecated

, deprecated

Definition at line 56 of file clocks.vhd.

Flag from ext. PLL, 0 = BC not available, 1 = BC present.

Definition at line 66 of file clocks.vhd.

slow clock for internal trigger generation

Definition at line 63 of file clocks.vhd.

lock flag of all DCMs

Definition at line 67 of file clocks.vhd.

200 MHz in, deprecated

Definition at line 44 of file clocks.vhd.

200 MHz out shifted by

Definition at line 51 of file clocks.vhd.

80 MHz for SATA logic

Definition at line 60 of file clocks.vhd.

arithmetic operations on std_logic datatypes, see file

Definition at line 28 of file clocks.vhd.

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 30 of file clocks.vhd.

100 MHz from ML410

Definition at line 43 of file clocks.vhd.

Library with Xilinx primitives.

Definition at line 32 of file clocks.vhd.

Header with Xilinx primitives.

Definition at line 34 of file clocks.vhd.

Select source for external PLL, 0 = BC, 1 = int. Oscillator.

Definition at line 65 of file clocks.vhd.

The documentation for this class was generated from the following file:

, deprecated

, deprecated  , deprecated

, deprecated