ddr_chksum_cal.ddr_dsp_chksum_cal_arc Architecture Reference

Running UDP checksum calculation DDR. More...

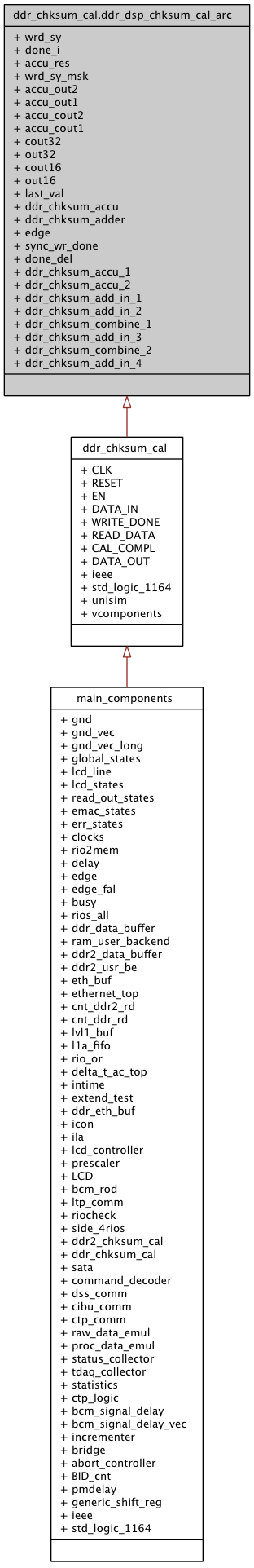

Inheritance diagram for ddr_chksum_cal.ddr_dsp_chksum_cal_arc:

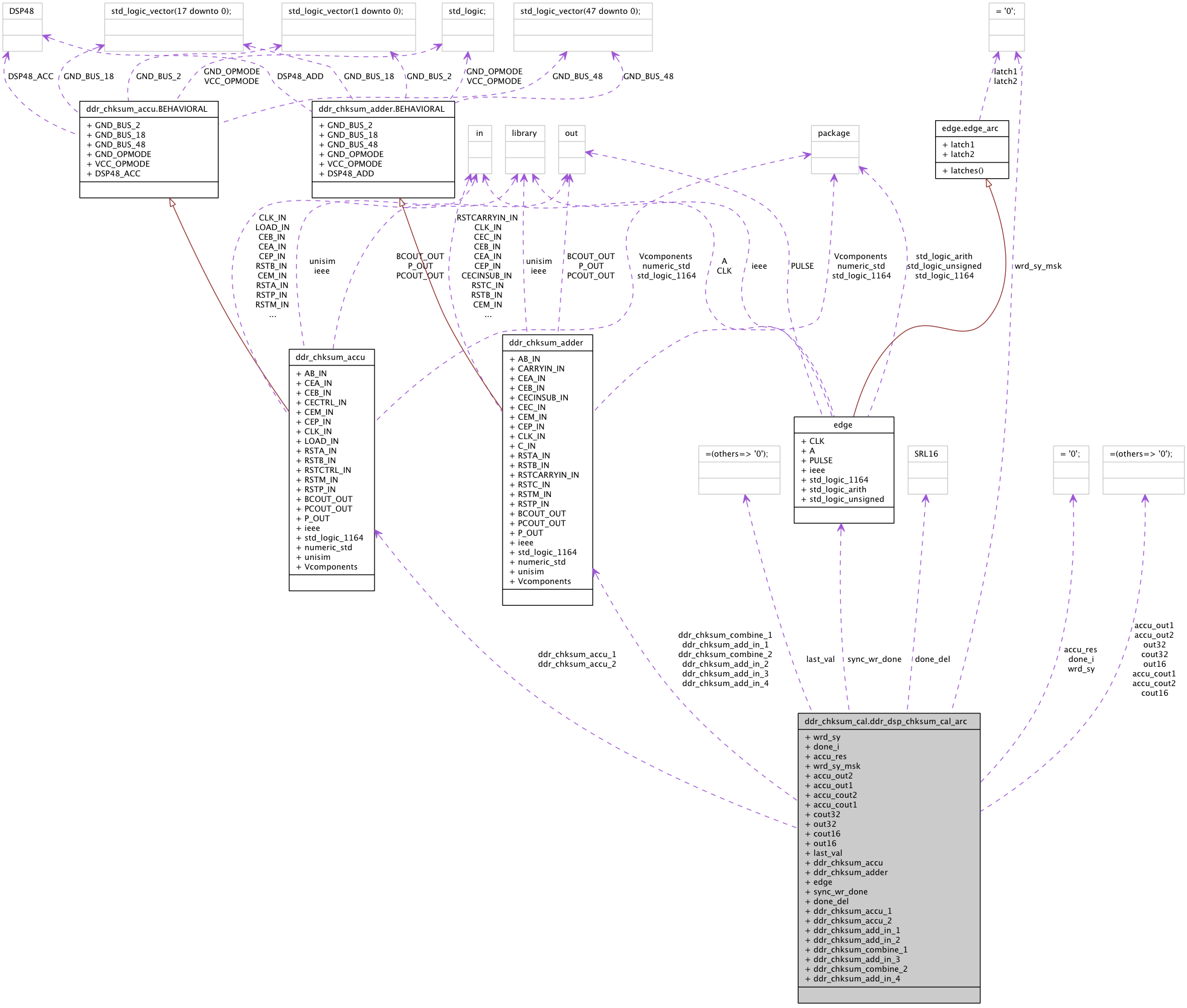

Collaboration diagram for ddr_chksum_cal.ddr_dsp_chksum_cal_arc:

Components | |

| ddr_chksum_accu | <Entity ddr_chksum_accu> |

| 32-bit accu | |

| ddr_chksum_adder | <Entity ddr_chksum_adder> |

| 16-bit adder | |

| edge | <Entity edge> |

| pulse sync | |

Signals | |

| wrd_sy | std_logic := ' 0 ' |

| done_i | std_logic := ' 0 ' |

| accu_res | std_logic := ' 0 ' |

| wrd_sy_msk | std_logic := ' 0 ' |

| accu_out2 | std_logic_vector ( 47 downto 0 ) := ( others = > ' 0 ' ) |

| accu_out1 | std_logic_vector ( 47 downto 0 ) := ( others = > ' 0 ' ) |

| accu_cout2 | std_logic_vector ( 47 downto 0 ) := ( others = > ' 0 ' ) |

| accu_cout1 | std_logic_vector ( 47 downto 0 ) := ( others = > ' 0 ' ) |

| cout32 | std_logic_vector ( 47 downto 0 ) := ( others = > ' 0 ' ) |

| out32 | std_logic_vector ( 47 downto 0 ) := ( others = > ' 0 ' ) |

| cout16 | std_logic_vector ( 47 downto 0 ) := ( others = > ' 0 ' ) |

| out16 | std_logic_vector ( 47 downto 0 ) := ( others = > ' 0 ' ) |

| last_val | std_logic_vector ( 15 downto 0 ) := ( others = > ' 0 ' ) |

Component Instantiations | |

| sync_wr_done | edge <Entity edge> |

| sync WRITE_DONE | |

| done_del | SRL16 |

| shift register to delay done signal | |

| ddr_chksum_accu_1 | ddr_chksum_accu <Entity ddr_chksum_accu> |

| 1st stage accu | |

| ddr_chksum_accu_2 | ddr_chksum_accu <Entity ddr_chksum_accu> |

| 1st stage accu | |

| ddr_chksum_add_in_1 | ddr_chksum_adder <Entity ddr_chksum_adder> |

| 2nd stage carry add-in | |

| ddr_chksum_add_in_2 | ddr_chksum_adder <Entity ddr_chksum_adder> |

| 2nd stage carry add-in | |

| ddr_chksum_combine_1 | ddr_chksum_adder <Entity ddr_chksum_adder> |

| 3rd stage combine adder | |

| ddr_chksum_add_in_3 | ddr_chksum_adder <Entity ddr_chksum_adder> |

| 4th stage carry add-in | |

| ddr_chksum_combine_2 | ddr_chksum_adder <Entity ddr_chksum_adder> |

| 5th stage combine adder | |

| ddr_chksum_add_in_4 | ddr_chksum_adder <Entity ddr_chksum_adder> |

| 6th stage carry add-in | |

Detailed Description

Running UDP checksum calculation DDR.This entity does a running checksum calculation according to the UDP protocol specification, using DSP48 primitives.

Definition at line 54 of file ddr_chksum_cal.vhd.

Member Data Documentation

ddr_chksum_accu [Component] |

ddr_chksum_accu_1 ddr_chksum_accu [Component Instantiation] |

ddr_chksum_accu_2 ddr_chksum_accu [Component Instantiation] |

ddr_chksum_add_in_1 ddr_chksum_adder [Component Instantiation] |

ddr_chksum_add_in_2 ddr_chksum_adder [Component Instantiation] |

ddr_chksum_add_in_3 ddr_chksum_adder [Component Instantiation] |

ddr_chksum_add_in_4 ddr_chksum_adder [Component Instantiation] |

ddr_chksum_adder [Component] |

ddr_chksum_combine_1 ddr_chksum_adder [Component Instantiation] |

ddr_chksum_combine_2 ddr_chksum_adder [Component Instantiation] |

done_del SRL16 [Component Instantiation] |

edge [Component] |

sync_wr_done edge [Component Instantiation] |

The documentation for this class was generated from the following file: