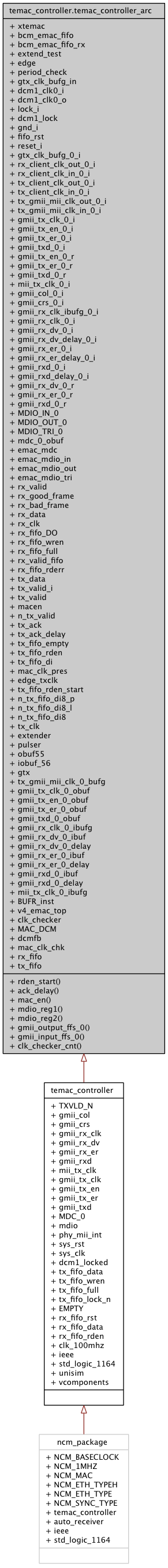

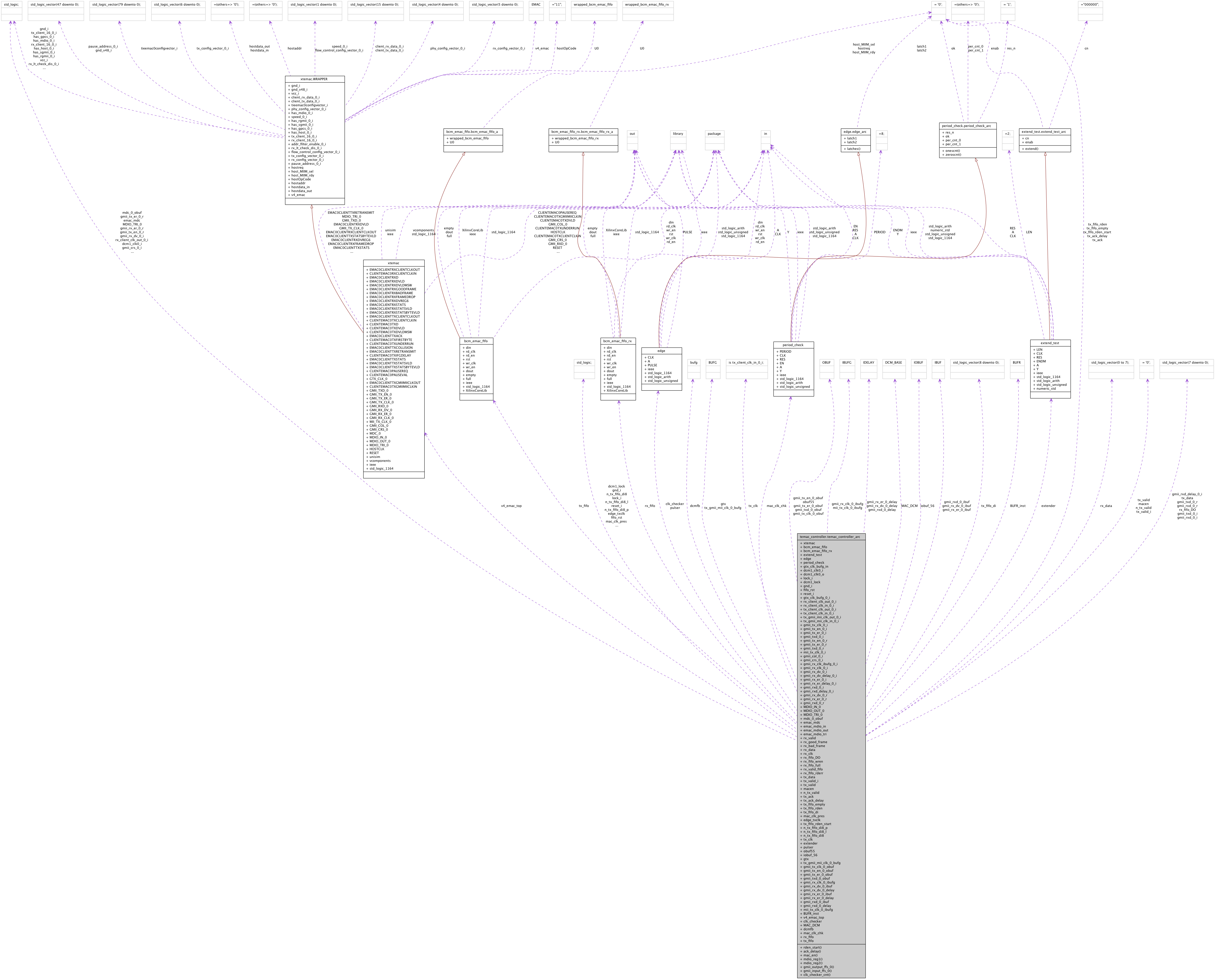

temac_controller.temac_controller_arc Architecture Reference

support logic for TEMAC More...

Processes | |

| rden_start | ( tx_clk , sys_rst ) |

| trigger read from TX FIFO | |

| ack_delay | ( tx_clk , sys_rst ) |

| wait for ack from xtemac | |

| mac_en | ( tx_clk , sys_rst ) |

| enable for xtemac | |

| mdio_reg1 | ( sys_clk ) |

| MDIO registers. | |

| mdio_reg2 | ( mdc_0_obuf ) |

| gmii_output_ffs_0 | ( tx_gmii_mii_clk_in_0_i , reset_i ) |

| gmii_input_ffs_0 | ( gmii_rx_clk_0_i , reset_i ) |

| Infer IOB Input flip-flops. | |

| clk_checker_cnt | ( clk_100mhz ) |

| clock check | |

Components | |

| xtemac | <Entity xtemac> |

| TEMAC wrapper. | |

| bcm_emac_fifo | <Entity bcm_emac_fifo> |

| TX data FIFO. | |

| bcm_emac_fifo_rx | <Entity bcm_emac_fifo_rx> |

| RX data FIFO. | |

| extend_test | <Entity extend_test> |

| pulse extender | |

| edge | <Entity edge> |

| edge detection | |

| period_check | <Entity period_check> |

| period check for clock signal | |

Signals | |

| gtx_clk_bufg_in | std_logic |

| dcm1_clk0_i | std_logic |

| dcm1_clk0_o | std_logic |

| lock_i | std_logic |

| dcm1_lock | std_logic |

| gnd_i | std_logic |

| fifo_rst | std_logic |

| reset_i | std_logic |

| gtx_clk_bufg_0_i | std_logic |

| rx_client_clk_out_0_i | std_logic |

| rx_client_clk_in_0_i | std_logic |

| tx_client_clk_out_0_i | std_logic |

| tx_client_clk_in_0_i | std_logic |

| tx_gmii_mii_clk_out_0_i | std_logic |

| tx_gmii_mii_clk_in_0_i | std_logic |

| gmii_tx_clk_0_i | std_logic |

| gmii_tx_en_0_i | std_logic |

| gmii_tx_er_0_i | std_logic |

| gmii_txd_0_i | std_logic_vector ( 7 downto 0 ) |

| gmii_tx_en_0_r | std_logic |

| gmii_tx_er_0_r | std_logic |

| gmii_txd_0_r | std_logic_vector ( 7 downto 0 ) |

| mii_tx_clk_0_i | std_logic |

| gmii_col_0_i | std_logic |

| gmii_crs_0_i | std_logic |

| gmii_rx_clk_ibufg_0_i | std_logic |

| gmii_rx_clk_0_i | std_logic |

| gmii_rx_dv_0_i | std_logic |

| gmii_rx_dv_delay_0_i | std_logic |

| gmii_rx_er_0_i | std_logic |

| gmii_rx_er_delay_0_i | std_logic |

| gmii_rxd_0_i | std_logic_vector ( 7 downto 0 ) |

| gmii_rxd_delay_0_i | std_logic_vector ( 7 downto 0 ) |

| gmii_rx_dv_0_r | std_logic |

| gmii_rx_er_0_r | std_logic |

| gmii_rxd_0_r | std_logic_vector ( 7 downto 0 ) |

| MDIO_IN_0 | std_logic |

| MDIO_OUT_0 | std_logic |

| MDIO_TRI_0 | std_logic |

| mdc_0_obuf | std_logic |

| emac_mdc | std_logic |

| emac_mdio_in | std_logic |

| emac_mdio_out | std_logic |

| emac_mdio_tri | std_logic |

| rx_valid | std_logic |

| rx_good_frame | std_logic |

| rx_bad_frame | std_logic |

| rx_data | std_logic_vector ( 0 to 7 ) |

| rx_clk | std_logic |

| rx_fifo_DO | std_logic_vector ( 7 downto 0 ) |

| rx_fifo_wren | std_logic |

| rx_fifo_full | std_logic |

| rx_valid_fifo | std_logic |

| rx_fifo_rderr | std_logic |

| tx_data | std_logic_vector ( 7 downto 0 ) |

| tx_valid_i | std_logic := ' 0 ' |

| tx_valid | std_logic := ' 0 ' |

| macen | std_logic := ' 0 ' |

| n_tx_valid | std_logic := ' 0 ' |

| tx_ack | std_logic := ' 0 ' |

| tx_ack_delay | std_logic := ' 0 ' |

| tx_fifo_empty | std_logic := ' 0 ' |

| tx_fifo_rden | std_logic := ' 0 ' |

| tx_fifo_di | std_logic_vector ( 8 downto 0 ) |

| mac_clk_pres | std_logic |

| edge_txclk | std_logic |

| tx_fifo_rden_start | std_logic := ' 0 ' |

| n_tx_fifo_di8_p | std_logic |

| n_tx_fifo_di8_l | std_logic |

| n_tx_fifo_di8 | std_logic |

Component Instantiations | |

| extender | extend_test <Entity extend_test> |

| extend sys_rst | |

| pulser | edge <Entity edge> |

| sync extended reset | |

| obuf55 | OBUF |

| iobuf_56 | IOBUF |

| gtx | BUFG |

| GTX_CLK Clock Management - 125 MHz clock frequency supplied by the user. | |

| tx_gmii_mii_clk_0_bufg | BUFG |

| gmii_tx_clk_0_obuf | OBUF |

| GMII Transmitter Clock Management. | |

| gmii_tx_en_0_obuf | OBUF |

| Drive GMII TX signals through Output Buffers and onto PADS. | |

| gmii_tx_er_0_obuf | OBUF |

| Drive GMII TX signals through Output Buffers and onto PADS. | |

| gmii_txd_0_obuf | OBUF |

| Drive GMII TX signals through Output Buffers and onto PADS. | |

| gmii_rx_clk_0_ibufg | IBUFG |

| GMII Receiver Clock Management. | |

| gmii_rx_dv_0_ibuf | IBUF |

| gmii_rx_dv_0_delay | IDELAY |

| idelay primitive | |

| gmii_rx_er_0_ibuf | IBUF |

| gmii_rx_er_0_delay | IDELAY |

| idelay primitive | |

| gmii_rxd_0_ibuf | IBUF |

| gmii_rxd_0_delay | IDELAY |

| idelay primitive | |

| mii_tx_clk_0_ibufg | IBUFG |

| MII_TX_CLK. | |

| BUFR_inst | BUFR |

| v4_emac_top | xtemac <Entity xtemac> |

| Instantiate V4 EMAC. | |

| clk_checker | edge <Entity edge> |

| clock check | |

| MAC_DCM | DCM_BASE |

| DCM providing 125MHz gtx_clk for temac. | |

| dcmfb | bufg |

| DCM feedback loop. | |

| mac_clk_chk | period_check <Entity period_check> |

| period check of clock from xtemac | |

| rx_fifo | bcm_emac_fifo_rx <Entity bcm_emac_fifo_rx> |

| RX data FIFO. | |

| tx_fifo | bcm_emac_fifo <Entity bcm_emac_fifo> |

| TX data FIFO. | |

Aliases | |

| tx_clk | tx_client_clk_in_0_i |

Detailed Description

support logic for TEMACDefinition at line 90 of file temac_controller.vhd.

Member Function Documentation

| ack_delay | ( tx_clk , | |

| sys_rst ) |

wait for ack from xtemac

Definition at line 327 of file temac_controller.vhd.

00327 ack_delay : process (tx_clk, sys_rst) 00328 begin 00329 if sys_rst = '1' then 00330 tx_ack_delay <= '0'; 00331 elsif tx_clk'event and tx_clk = '1' then 00332 if tx_valid = '0' then 00333 tx_ack_delay <= '0'; 00334 elsif tx_ack = '1' then 00335 tx_ack_delay <= '1'; 00336 end if; 00337 end if; 00338 end process ack_delay;

| clk_checker_cnt | ( clk_100mhz ) |

clock check

Definition at line 644 of file temac_controller.vhd.

00644 clk_checker_cnt : process(clk_100mhz) 00645 variable cnt : integer range 0 to 10 := 0; 00646 begin 00647 if clk_100mhz'event and clk_100mhz = '1' then 00648 if sys_rst = '1' then 00649 cnt := 0; 00650 mac_clk_pres <= '0'; 00651 else 00652 if edge_txclk = '1' then 00653 if mac_clk_pres = '0' then 00654 cnt := cnt + 1; 00655 if cnt = 4 then 00656 mac_clk_pres <= '1'; 00657 end if; 00658 else 00659 cnt := cnt; 00660 end if; 00661 end if; 00662 end if; 00663 end if; 00664 end process clk_checker_cnt;

| gmii_input_ffs_0 | ( gmii_rx_clk_0_i , | |

| reset_i ) |

Infer IOB Input flip-flops.

Definition at line 529 of file temac_controller.vhd.

00529 gmii_input_ffs_0 : process (gmii_rx_clk_0_i, reset_i) 00530 begin 00531 if reset_i = '1' then 00532 gmii_rx_dv_0_r <= '0'; 00533 gmii_rx_er_0_r <= '0'; 00534 gmii_rxd_0_r <= (others => '0'); 00535 elsif gmii_rx_clk_0_i'event and gmii_rx_clk_0_i = '1' then 00536 gmii_rx_dv_0_r <= gmii_rx_dv_delay_0_i; 00537 gmii_rx_er_0_r <= gmii_rx_er_delay_0_i; 00538 gmii_rxd_0_r <= gmii_rxd_delay_0_i; 00539 end if; 00540 end process gmii_input_ffs_0;

| gmii_output_ffs_0 | ( tx_gmii_mii_clk_in_0_i , | |

| reset_i ) |

GMII Transmitter Logic : Drive TX signals through IOBs onto GMII interface Infer IOB Output flip-flops.

Definition at line 442 of file temac_controller.vhd.

00442 gmii_output_ffs_0 : process (tx_gmii_mii_clk_in_0_i, reset_i) 00443 begin 00444 if reset_i = '1' then 00445 gmii_tx_en_0_r <= '0'; 00446 gmii_tx_er_0_r <= '0'; 00447 gmii_txd_0_r <= (others => '0'); 00448 elsif tx_gmii_mii_clk_in_0_i'event and tx_gmii_mii_clk_in_0_i = '1' then 00449 gmii_tx_en_0_r <= gmii_tx_en_0_i; 00450 gmii_tx_er_0_r <= gmii_tx_er_0_i; 00451 gmii_txd_0_r <= gmii_txd_0_i; 00452 end if; 00453 end process gmii_output_ffs_0;

| mac_en | ( tx_clk , | |

| sys_rst ) |

enable for xtemac

Definition at line 341 of file temac_controller.vhd.

00341 mac_en : process(tx_clk, sys_rst) 00342 begin 00343 if sys_rst = '1' then 00344 macen <= '0'; 00345 elsif tx_clk'event and tx_clk = '1' then 00346 if tx_fifo_rden_start = '1' then 00347 macen <= '1'; 00348 elsif tx_valid = '0' then 00349 macen <= '0'; 00350 else 00351 macen <= macen; 00352 end if; 00353 end if; 00354 end process mac_en;

| mdio_reg1 | ( sys_clk ) |

MDIO registers.

MDIO registers

Definition at line 398 of file temac_controller.vhd.

00398 mdio_reg1 : process (sys_clk) 00399 begin 00400 if sys_clk'event and sys_clk = '1' then 00401 mdc_0_obuf <= emac_mdc; 00402 MDIO_OUT_0 <= emac_mdio_out; 00403 MDIO_TRI_0 <= emac_mdio_tri; 00404 end if; 00405 00406 00407 end process mdio_reg1;

| rden_start | ( tx_clk , | |

| sys_rst ) |

trigger read from TX FIFO

Definition at line 317 of file temac_controller.vhd.

00317 rden_start : process (tx_clk, sys_rst) 00318 begin 00319 if sys_rst = '1' then 00320 tx_fifo_rden_start <= '0'; 00321 elsif tx_clk'event and tx_clk = '1' then 00322 tx_fifo_rden_start <= n_tx_fifo_di8_p; 00323 end if; 00324 end process rden_start;

Member Data Documentation

bcm_emac_fifo [Component] |

bcm_emac_fifo_rx [Component] |

clk_checker edge [Component Instantiation] |

dcmfb bufg [Component Instantiation] |

edge [Component] |

extend_test [Component] |

extender extend_test [Component Instantiation] |

gmii_rx_clk_0_ibufg IBUFG [Component Instantiation] |

gmii_rx_dv_0_delay IDELAY [Component Instantiation] |

gmii_rx_dv_0_ibuf IBUF [Component Instantiation] |

GMII Receiver Logic : Receive RX signals through IOBs from GMII interface Drive input GMII Rx signals from PADS through Input Buffers and then use IDELAYs to provide Zero-Hold Time Delay ?!?!? Should the C, CE, INC, and RST ports be connected to GND or left OPEN ?!

Definition at line 484 of file temac_controller.vhd.

gmii_rx_er_0_delay IDELAY [Component Instantiation] |

gmii_rxd_0_delay IDELAY [Component Instantiation] |

gmii_tx_clk_0_obuf OBUF [Component Instantiation] |

gmii_tx_en_0_obuf OBUF [Component Instantiation] |

Drive GMII TX signals through Output Buffers and onto PADS.

Definition at line 456 of file temac_controller.vhd.

gmii_tx_er_0_obuf OBUF [Component Instantiation] |

Drive GMII TX signals through Output Buffers and onto PADS.

Definition at line 458 of file temac_controller.vhd.

gmii_txd_0_obuf OBUF [Component Instantiation] |

Drive GMII TX signals through Output Buffers and onto PADS.

Definition at line 461 of file temac_controller.vhd.

gtx BUFG [Component Instantiation] |

GTX_CLK Clock Management - 125 MHz clock frequency supplied by the user.

Definition at line 418 of file temac_controller.vhd.

mac_clk_chk period_check [Component Instantiation] |

MAC_DCM DCM_BASE [Component Instantiation] |

mii_tx_clk_0_ibufg IBUFG [Component Instantiation] |

period_check [Component] |

rx_fifo bcm_emac_fifo_rx [Component Instantiation] |

tx_fifo bcm_emac_fifo [Component Instantiation] |

v4_emac_top xtemac [Component Instantiation] |

xtemac [Component] |

The documentation for this class was generated from the following file: