temac_controller Entity Reference

support logic for EMAC More...

Inheritance diagram for temac_controller:

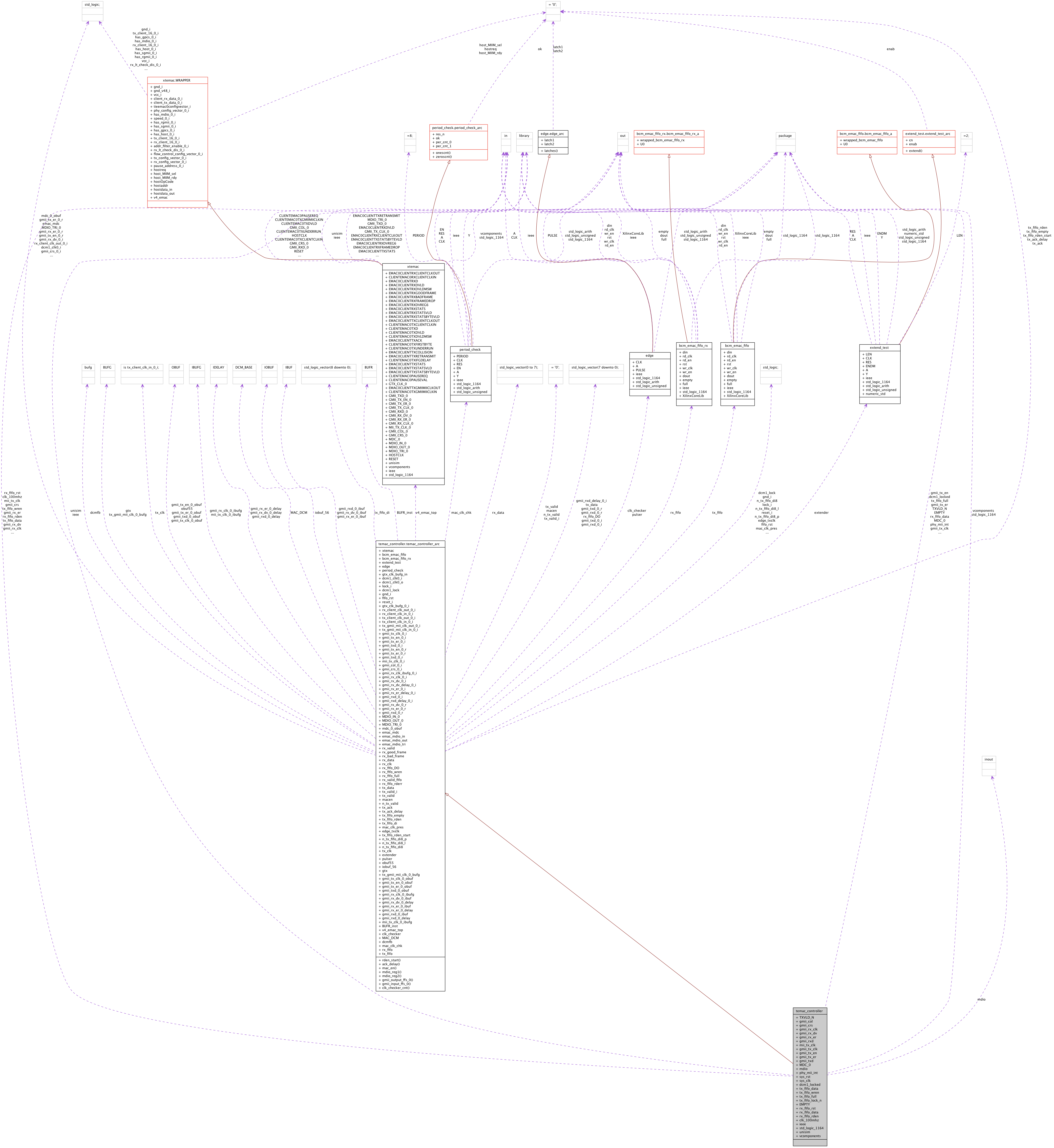

Collaboration diagram for temac_controller:

Architectures | |

| temac_controller_arc | Architecture |

| support logic for TEMAC More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| unisim | |

| Library with Xilinx primitives. | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| vcomponents | |

| Header with Xilinx primitives. | |

Ports | |

| TXVLD_N | out std_logic |

| debug | |

| gmii_col | in std_logic |

| PHY interface. | |

| gmii_crs | in std_logic |

| PHY interface. | |

| gmii_rx_clk | in std_logic |

| PHY interface. | |

| gmii_rx_dv | in std_logic |

| PHY interface. | |

| gmii_rx_er | in std_logic |

| PHY interface. | |

| gmii_rxd | in std_logic_vector ( 0 to 7 ) |

| PHY interface. | |

| mii_tx_clk | in std_logic |

| PHY interface. | |

| gmii_tx_clk | out std_logic |

| PHY interface. | |

| gmii_tx_en | out std_logic |

| PHY interface. | |

| gmii_tx_er | out std_logic |

| PHY interface. | |

| gmii_txd | out std_logic_vector ( 0 to 7 ) |

| PHY interface. | |

| MDC_0 | out std_logic |

| PHY interface. | |

| mdio | inout std_logic |

| PHY interface. | |

| phy_mii_int | out std_logic |

| PHY interface. | |

| sys_rst | in std_logic |

| reset | |

| sys_clk | in std_logic |

| 100 MHz clock | |

| dcm1_locked | out std_logic |

| DCM status flag. | |

| tx_fifo_data | in std_logic_vector ( 0 to 31 ) |

| data in 24 - 31, rest control characters | |

| tx_fifo_wren | in std_logic |

| write enable | |

| tx_fifo_full | out std_logic |

| FIFO full flag. | |

| tx_fifo_lock_n | in std_logic |

| FIFO status flag. | |

| EMPTY | out std_logic |

| TX FIFO empty flag. | |

| rx_fifo_rst | in std_logic |

| FIFO reset. | |

| rx_fifo_data | out std_logic_vector ( 0 to 31 ) |

| data out 24 - 31, rest control characters | |

| rx_fifo_rden | in std_logic |

| read enable | |

| clk_100mhz | in std_logic |

| 100 MHz clock | |

Detailed Description

support logic for EMACcontains datapath fifos including their support logic, data handling as well as logic for proper startup procedures and the clocking scheme needed for the EMAC.

Definition at line 57 of file temac_controller.vhd.

Member Data Documentation

clk_100mhz in std_logic [Port] |

dcm1_locked out std_logic [Port] |

EMPTY out std_logic [Port] |

gmii_col in std_logic [Port] |

gmii_crs in std_logic [Port] |

gmii_rx_clk in std_logic [Port] |

gmii_rx_dv in std_logic [Port] |

gmii_rx_er in std_logic [Port] |

gmii_rxd in std_logic_vector ( 0 to 7 ) [Port] |

gmii_tx_clk out std_logic [Port] |

gmii_tx_en out std_logic [Port] |

gmii_tx_er out std_logic [Port] |

gmii_txd out std_logic_vector ( 0 to 7 ) [Port] |

ieee library [Library] |

MDC_0 out std_logic [Port] |

mdio inout std_logic [Port] |

mii_tx_clk in std_logic [Port] |

phy_mii_int out std_logic [Port] |

rx_fifo_data out std_logic_vector ( 0 to 31 ) [Port] |

rx_fifo_rden in std_logic [Port] |

rx_fifo_rst in std_logic [Port] |

std_logic_1164 package [Package] |

sys_clk in std_logic [Port] |

sys_rst in std_logic [Port] |

tx_fifo_data in std_logic_vector ( 0 to 31 ) [Port] |

tx_fifo_full out std_logic [Port] |

tx_fifo_lock_n in std_logic [Port] |

tx_fifo_wren in std_logic [Port] |

TXVLD_N out std_logic [Port] |

unisim library [Library] |

vcomponents package [Package] |

The documentation for this class was generated from the following file: