bcm_emac_fifo_rx Entity Reference

Wrapper file for FIFO core for Ethernet RX. More...

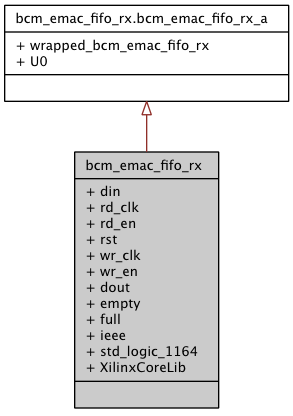

Inheritance diagram for bcm_emac_fifo_rx:

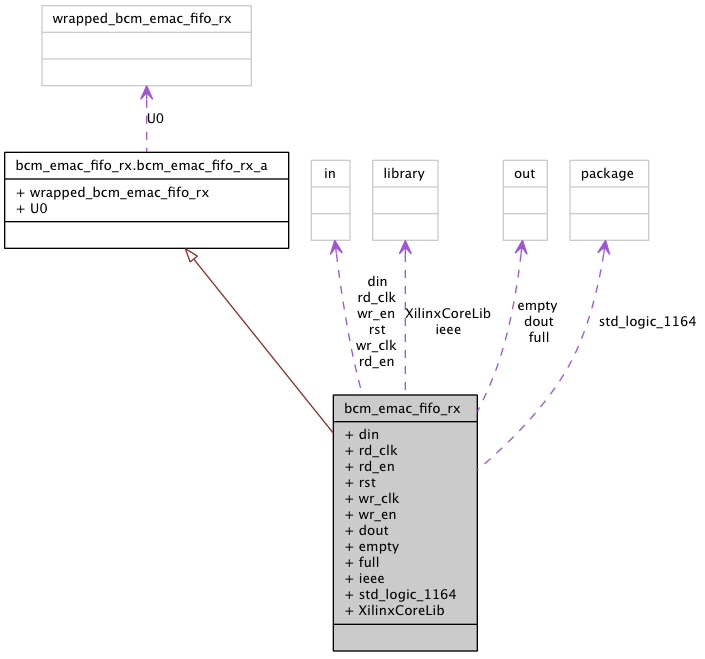

Collaboration diagram for bcm_emac_fifo_rx:

Architectures | |

| bcm_emac_fifo_rx_a | Architecture |

| Wrapper file for FIFO core for Ethernet RX. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| XilinxCoreLib | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

Ports | |

| din | in std_logic_vector ( 8 downto 0 ) |

| Data in. | |

| rd_clk | in std_logic |

| Read clock, 100 MHz. | |

| rd_en | in std_logic |

| Read enable. | |

| rst | in std_logic |

| Reset. | |

| wr_clk | in std_logic |

| Write clock, 12,5 MHz. | |

| wr_en | in std_logic |

| Write enable. | |

| dout | out std_logic_vector ( 8 downto 0 ) |

| Data out. | |

| empty | out std_logic |

| Empty status flag. | |

| full | out std_logic |

| Full status flag. | |

Detailed Description

Wrapper file for FIFO core for Ethernet RX.Read & write clocks need to be at specified values for FIFO status flags to function properly.

Definition at line 70 of file bcm_emac_fifo_rx.vhd.

Member Data Documentation

din in std_logic_vector ( 8 downto 0 ) [Port] |

dout out std_logic_vector ( 8 downto 0 ) [Port] |

empty out std_logic [Port] |

full out std_logic [Port] |

ieee library [Library] |

rd_clk in std_logic [Port] |

rd_en in std_logic [Port] |

rst in std_logic [Port] |

std_logic_1164 package [Package] |

wr_clk in std_logic [Port] |

wr_en in std_logic [Port] |

The documentation for this class was generated from the following file: