clocks.coldplay Architecture Reference

central clock module More...

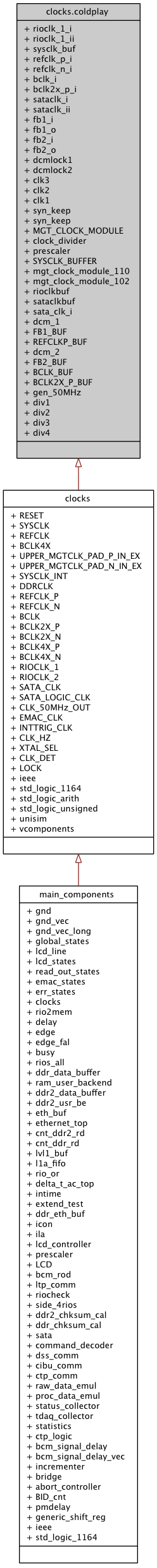

Inheritance diagram for clocks.coldplay:

Collaboration diagram for clocks.coldplay:

Components | |

| MGT_CLOCK_MODULE | <Entity MGT_CLOCK_MODULE> |

| RocketIO clock module. | |

| clock_divider | <Entity clock_divider> |

| simple frequency devider | |

| prescaler | <Entity prescaler> |

| standard prescaler | |

Signals | |

| rioclk_1_i | std_logic := ' 0 ' |

| rioclk_1_ii | std_logic := ' 0 ' |

| sysclk_buf | std_logic := ' 0 ' |

| refclk_p_i | std_logic := ' 0 ' |

| refclk_n_i | std_logic := ' 0 ' |

| bclk_i | std_logic := ' 0 ' |

| bclk2x_p_i | std_logic := ' 0 ' |

| sataclk_i | std_logic := ' 0 ' |

| sataclk_ii | std_logic := ' 0 ' |

| fb1_i | std_logic := ' 0 ' |

| fb1_o | std_logic := ' 0 ' |

| fb2_i | std_logic := ' 0 ' |

| fb2_o | std_logic := ' 0 ' |

| dcmlock1 | std_logic := ' 0 ' |

| dcmlock2 | std_logic := ' 0 ' |

| clk3 | std_logic := ' 0 ' |

| clk2 | std_logic := ' 0 ' |

| clk1 | std_logic := ' 0 ' |

Attributes | |

| syn_keep | boolean |

| syn_keep | true |

Component Instantiations | |

| SYSCLK_BUFFER | IBUFG |

| PLL lock flag of all globally used DCMs. | |

| mgt_clock_module_110 | MGT_CLOCK_MODULE <Entity MGT_CLOCK_MODULE> |

| clock module for DAQ-RIOs | |

| mgt_clock_module_102 | MGT_CLOCK_MODULE <Entity MGT_CLOCK_MODULE> |

| clock module for SATA-RIOs | |

| rioclkbuf | BUFG |

| BUFG for parallel RIO clocks. | |

| sataclkbuf | BUFG |

| BUFG for parallel SATA clocks. | |

| sata_clk_i | clock_divider <Entity clock_divider> |

| derive slow clock for SATA logic | |

| dcm_1 | DCM_BASE |

| FB1_BUF | BUFG |

| REFCLKP_BUF | BUFG |

| BUFG for 200 MHz, positive. | |

| dcm_2 | DCM_BASE |

| FB2_BUF | BUFG |

| BCLK_BUF | BUFG |

| BUFG for 40 MHz. | |

| BCLK2X_P_BUF | BUFG |

| BUFG for 80 MHz. | |

| gen_50MHz | clock_divider <Entity clock_divider> |

| generate 50 MHz for SATA | |

| div1 | prescaler <Entity prescaler> |

| scaler for 1 Hz clock | |

| div2 | prescaler <Entity prescaler> |

| scaler for 1 Hz clock | |

| div3 | prescaler <Entity prescaler> |

| scaler for 1 Hz clock | |

| div4 | prescaler <Entity prescaler> |

| scaler for 1 Hz clock | |

Detailed Description

central clock moduleThis architecture contains 2 DCMs to derive all necessary clocks from the external clock sources. Also the reference clock modules for the RocketIOs are contained in this architecture. All clocks that are used by the rest of the design are put on global clock nets.

Definition at line 76 of file clocks.vhd.

Member Data Documentation

BCLK2X_P_BUF BUFG [Component Instantiation] |

BCLK_BUF BUFG [Component Instantiation] |

clock_divider [Component] |

dcm_1 DCM_BASE [Component Instantiation] |

derive clocks from 100 MHz: 100 MHz for EMAC, 200 MHz for DDR2

Definition at line 195 of file clocks.vhd.

dcm_2 DCM_BASE [Component Instantiation] |

derive clocks from 160 MHz 40, 80, 160 MHz for DAQ, 160 for DDR

Definition at line 239 of file clocks.vhd.

gen_50MHz clock_divider [Component Instantiation] |

MGT_CLOCK_MODULE [Component] |

mgt_clock_module_102 MGT_CLOCK_MODULE [Component Instantiation] |

mgt_clock_module_110 MGT_CLOCK_MODULE [Component Instantiation] |

prescaler [Component] |

REFCLKP_BUF BUFG [Component Instantiation] |

rioclkbuf BUFG [Component Instantiation] |

sata_clk_i clock_divider [Component Instantiation] |

sataclkbuf BUFG [Component Instantiation] |

SYSCLK_BUFFER IBUFG [Component Instantiation] |

PLL lock flag of all globally used DCMs.

Input clock buffer for 100 MHz clock from oscillator on ML410

Definition at line 141 of file clocks.vhd.

The documentation for this class was generated from the following file: