bridge.bridge_arc Architecture Reference

top module of SATA More...

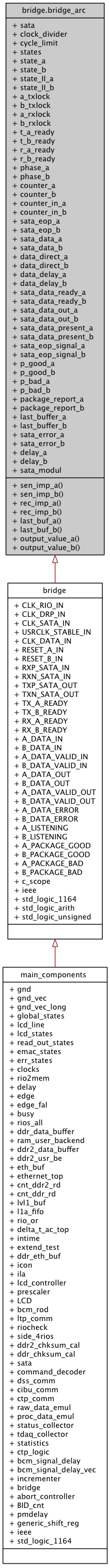

Inheritance diagram for bridge.bridge_arc:

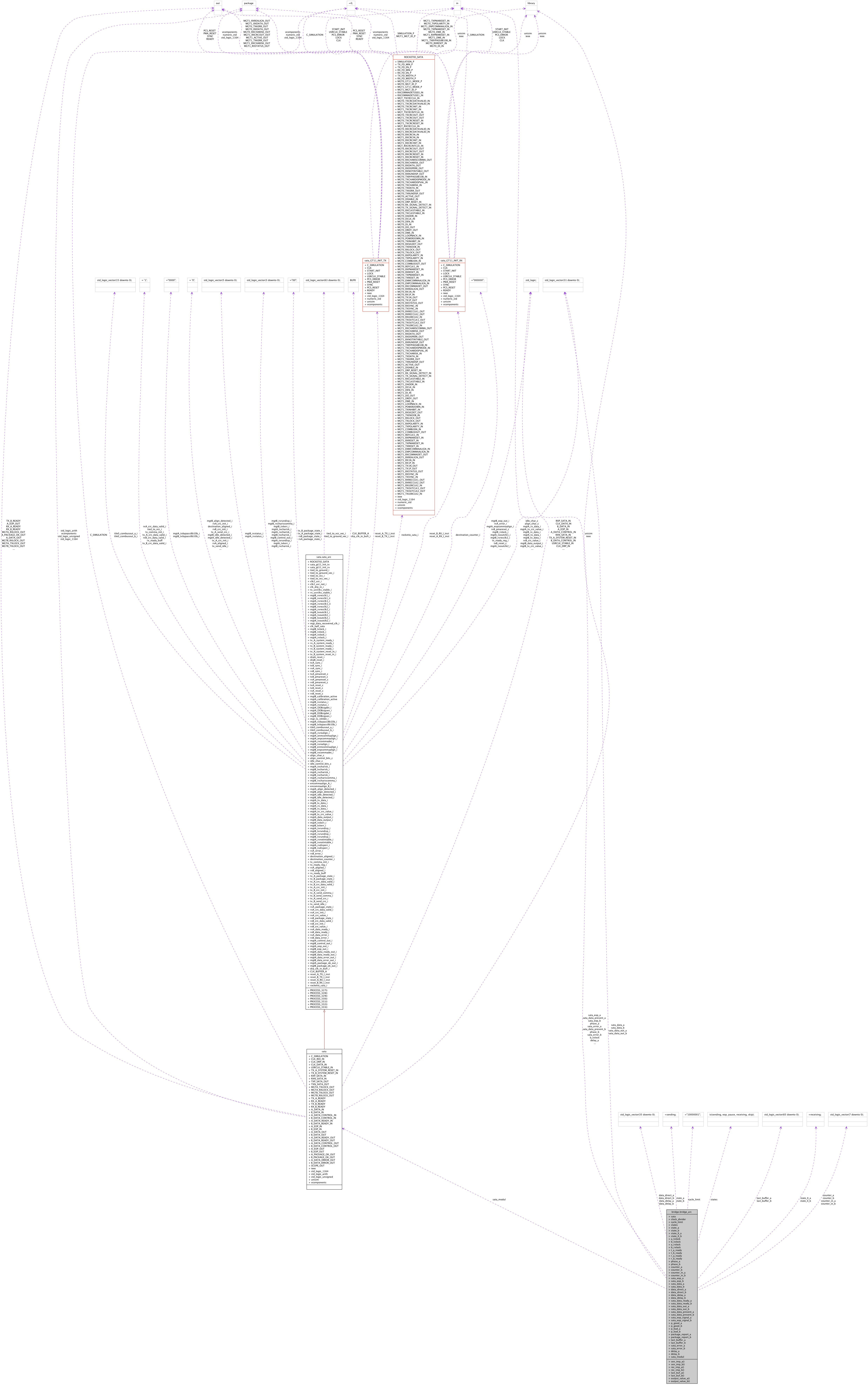

Collaboration diagram for bridge.bridge_arc:

Processes | |

| sen_imp_a | ( CLK_SATA_IN ) |

| sending with "holes" = EOPs, ch A | |

| sen_imp_b | ( CLK_SATA_IN ) |

| sending with "holes" = EOPs, ch B | |

| rec_imp_a | ( CLK_SATA_IN ) |

| receiving with "holes" = EOPs, ch A | |

| rec_imp_b | ( CLK_SATA_IN ) |

| receiving with "holes" = EOPs, ch B | |

| last_buf_a | ( CLK_SATA_IN ) |

| assemble data of two cycles for output | |

| last_buf_b | ( CLK_SATA_IN ) |

| assemble data of two cycles for output | |

| output_value_a | ( CLK_DATA_IN ) |

| assemble data of two cycles for output | |

| output_value_b | ( CLK_DATA_IN ) |

| assemble data of two cycles for output | |

Components | |

| sata | <Entity sata> |

| SATA wrapper. | |

| clock_divider | <Entity clock_divider> |

| simple clock divider | |

Constants | |

| cycle_limit | std_logic_vector ( 7 downto 0 ) := " 10000001 " |

Types | |

| states | ( sending , eop , pause , receiving , skip ) |

Signals | |

| state_a | states := sending |

| state_b | states := sending |

| state_II_a | states := receiving |

| state_II_b | states := receiving |

| a_txlock | std_logic |

| b_txlock | std_logic |

| a_rxlock | std_logic |

| b_rxlock | std_logic |

| t_a_ready | std_logic |

| t_b_ready | std_logic |

| r_a_ready | std_logic |

| r_b_ready | std_logic |

| phase_a | std_logic |

| phase_b | std_logic |

| counter_a | std_logic_vector ( 7 downto 0 ) |

| counter_b | std_logic_vector ( 7 downto 0 ) |

| counter_in_a | std_logic_vector ( 7 downto 0 ) |

| counter_in_b | std_logic_vector ( 7 downto 0 ) |

| sata_eop_a | std_logic |

| sata_eop_b | std_logic |

| sata_data_a | std_logic_vector ( 31 downto 0 ) |

| sata_data_b | std_logic_vector ( 31 downto 0 ) |

| data_direct_a | std_logic_vector ( 35 downto 0 ) |

| data_direct_b | std_logic_vector ( 35 downto 0 ) |

| data_delay_a | std_logic_vector ( 35 downto 0 ) |

| data_delay_b | std_logic_vector ( 35 downto 0 ) |

| sata_data_ready_a | std_logic |

| sata_data_ready_b | std_logic |

| sata_data_out_a | std_logic_vector ( 31 downto 0 ) |

| sata_data_out_b | std_logic_vector ( 31 downto 0 ) |

| sata_data_present_a | std_logic |

| sata_data_present_b | std_logic |

| sata_eop_signal_a | std_logic |

| sata_eop_signal_b | std_logic |

| p_good_a | std_logic |

| p_good_b | std_logic |

| p_bad_a | std_logic |

| p_bad_b | std_logic |

| package_report_a | std_logic |

| package_report_b | std_logic |

| last_buffer_a | std_logic_vector ( 65 downto 0 ) |

| last_buffer_b | std_logic_vector ( 65 downto 0 ) |

| sata_error_a | std_logic |

| sata_error_b | std_logic |

| delay_a | std_logic |

| delay_b | std_logic |

Component Instantiations | |

| sata_modul | sata <Entity sata> |

Detailed Description

top module of SATADefinition at line 78 of file bridge.vhd.

Member Function Documentation

| last_buf_a | ( CLK_SATA_IN ) |

assemble data of two cycles for output

Definition at line 462 of file bridge.vhd.

00462 last_buf_a : process (CLK_SATA_IN) 00463 begin 00464 if CLK_SATA_IN'event and CLK_SATA_IN = '1' then 00465 if CLK_DATA_IN = '1' then 00466 last_buffer_a(31 downto 0) <= sata_data_out_a; 00467 else 00468 last_buffer_a(63 downto 32) <= sata_data_out_a; 00469 last_buffer_a(64) <= sata_data_present_a; 00470 last_buffer_a(65) <= sata_error_a; 00471 end if; 00472 end if; 00473 end process;

| last_buf_b | ( CLK_SATA_IN ) |

assemble data of two cycles for output

Definition at line 476 of file bridge.vhd.

00476 last_buf_b : process (CLK_SATA_IN) 00477 begin 00478 if CLK_SATA_IN'event and CLK_SATA_IN = '1' then 00479 if CLK_DATA_IN = '1' then 00480 last_buffer_b(31 downto 0) <= sata_data_out_b; 00481 else 00482 last_buffer_b(63 downto 32) <= sata_data_out_b; 00483 last_buffer_b(64) <= sata_data_present_b; 00484 last_buffer_b(65) <= sata_error_b; 00485 end if; 00486 end if; 00487 end process;

| output_value_a | ( CLK_DATA_IN ) |

assemble data of two cycles for output

Definition at line 490 of file bridge.vhd.

00490 output_value_a : process(CLK_DATA_IN) 00491 begin 00492 if CLK_DATA_IN'event and CLK_DATA_IN = '1' then 00493 A_DATA_OUT <= last_buffer_a(63 downto 0); 00494 A_DATA_VALID_OUT <= last_buffer_a(64); 00495 A_DATA_ERROR <= last_buffer_a(65); 00496 end if; 00497 end process;

| output_value_b | ( CLK_DATA_IN ) |

assemble data of two cycles for output

Definition at line 500 of file bridge.vhd.

00500 output_value_b : process(CLK_DATA_IN) 00501 begin 00502 if CLK_DATA_IN'event and CLK_DATA_IN = '1' then 00503 B_DATA_OUT <= last_buffer_b(63 downto 0); 00504 B_DATA_VALID_OUT <= last_buffer_b(64); 00505 B_DATA_ERROR <= last_buffer_b(65); 00506 end if; 00507 end process;

| rec_imp_a | ( CLK_SATA_IN ) |

receiving with "holes" = EOPs, ch A

Definition at line 361 of file bridge.vhd.

00361 rec_imp_a : process (CLK_SATA_IN) 00362 begin 00363 if CLK_SATA_IN'event and CLK_SATA_IN = '1' then 00364 if RESET_A_IN = '1' then 00365 --we are in the middle of reset 00366 counter_in_a <= (others => '0'); 00367 state_II_a <= receiving; 00368 delay_a <= '0'; 00369 else 00370 --normal running 00371 case state_II_a is 00372 when receiving => 00373 if sata_eop_signal_a = '1' then 00374 state_II_a <= eop; 00375 counter_in_a <= (others => '0'); 00376 if CLK_DATA_IN = '0' then 00377 delay_a <= not delay_a; 00378 state_II_a <= skip; 00379 end if; 00380 end if; 00381 when eop => 00382 counter_in_a <= counter_in_a + 1; 00383 if counter_in_a = 2 then 00384 if package_report_a = '1' then 00385 p_good_a <= '1'; 00386 else 00387 p_bad_a <= '1'; 00388 end if; 00389 elsif counter_in_a = 4 then 00390 state_II_a <= receiving; 00391 counter_in_a <= (others => '0'); 00392 p_good_a <= '0'; 00393 p_bad_a <= '0'; 00394 end if; 00395 00396 when skip => 00397 state_II_a <= receiving; 00398 00399 when others => 00400 state_II_a <= receiving; 00401 counter_in_a <= (others => '0'); 00402 00403 end case; 00404 end if; 00405 end if; 00406 end process;

| rec_imp_b | ( CLK_SATA_IN ) |

receiving with "holes" = EOPs, ch B

Definition at line 409 of file bridge.vhd.

00409 rec_imp_b : process (CLK_SATA_IN) 00410 begin 00411 if CLK_SATA_IN'event and CLK_SATA_IN = '1' then 00412 if RESET_B_IN = '1' then 00413 --we are in the middle of reset 00414 counter_in_b <= (others => '0'); 00415 state_II_b <= receiving; 00416 delay_b <= '0'; 00417 else 00418 --normal running 00419 case state_II_b is 00420 when receiving => 00421 if sata_eop_signal_b = '1' then 00422 state_II_b <= eop; 00423 counter_in_b <= (others => '0'); 00424 if CLK_DATA_IN = '0' then 00425 delay_b <= not delay_b; 00426 state_II_b <= skip; 00427 end if; 00428 end if; 00429 when eop => 00430 counter_in_b <= counter_in_b + 1; 00431 if counter_in_b = 2 then 00432 if package_report_b = '1' then 00433 p_good_b <= '1'; 00434 else 00435 p_bad_b <= '1'; 00436 end if; 00437 elsif counter_in_b = 4 then 00438 state_II_b <= receiving; 00439 counter_in_b <= (others => '0'); 00440 p_good_b <= '0'; 00441 p_bad_b <= '0'; 00442 end if; 00443 00444 when skip => 00445 state_II_b <= receiving; 00446 00447 when others => 00448 state_II_b <= receiving; 00449 counter_in_b <= (others => '0'); 00450 00451 end case; 00452 end if; 00453 end if; 00454 end process;

| sen_imp_a | ( CLK_SATA_IN ) |

sending with "holes" = EOPs, ch A

Definition at line 275 of file bridge.vhd.

00275 sen_imp_a : process (CLK_SATA_IN) 00276 begin 00277 if CLK_SATA_IN'event and CLK_SATA_IN = '1' then 00278 if RESET_A_IN = '1' then 00279 --we are in the middle of reset 00280 counter_a <= (others => '0'); 00281 phase_a <= '0'; 00282 state_a <= sending; 00283 sata_eop_a <= '0'; 00284 else 00285 --normal running 00286 phase_a <= not phase_a; 00287 case state_a is 00288 when sending => 00289 counter_a <= counter_a + 1; 00290 if counter_a = cycle_limit then 00291 state_a <= eop; 00292 counter_a <= (others => '0'); 00293 sata_eop_a <= '1'; 00294 end if; 00295 00296 when eop => 00297 sata_eop_a <= '0'; 00298 state_a <= pause; 00299 00300 when pause => 00301 counter_a <= counter_a + 1; 00302 if counter_a = 2 then 00303 counter_a <= (others => '0'); 00304 state_a <= sending; 00305 end if; 00306 00307 when others => 00308 counter_a <= (others => '0'); 00309 state_a <= sending; 00310 00311 end case; 00312 00313 end if; 00314 end if; 00315 end process;

| sen_imp_b | ( CLK_SATA_IN ) |

sending with "holes" = EOPs, ch B

Definition at line 318 of file bridge.vhd.

00318 sen_imp_b : process (CLK_SATA_IN) 00319 begin 00320 if CLK_SATA_IN'event and CLK_SATA_IN = '1' then 00321 if RESET_B_IN = '1' then 00322 --we are in the middle of reset 00323 counter_b <= (others => '0'); 00324 phase_b <= '0'; 00325 state_b <= sending; 00326 sata_eop_b <= '0'; 00327 else 00328 --normal running 00329 phase_b <= not phase_b; 00330 case state_b is 00331 when sending => 00332 counter_b <= counter_b + 1; 00333 if counter_b = cycle_limit then 00334 state_b <= eop; 00335 counter_b <= (others => '0'); 00336 sata_eop_b <= '1'; 00337 end if; 00338 00339 when eop => 00340 sata_eop_b <= '0'; 00341 state_b <= pause; 00342 00343 when pause => 00344 counter_b <= counter_b + 1; 00345 if counter_b = 2 then 00346 counter_b <= (others => '0'); 00347 state_b <= sending; 00348 end if; 00349 00350 when others => 00351 counter_b <= (others => '0'); 00352 state_b <= sending; 00353 00354 end case; 00355 00356 end if; 00357 end if; 00358 end process;

Member Data Documentation

clock_divider [Component] |

sata [Component] |

The documentation for this class was generated from the following file: