bridge Entity Reference

top module of SATA More...

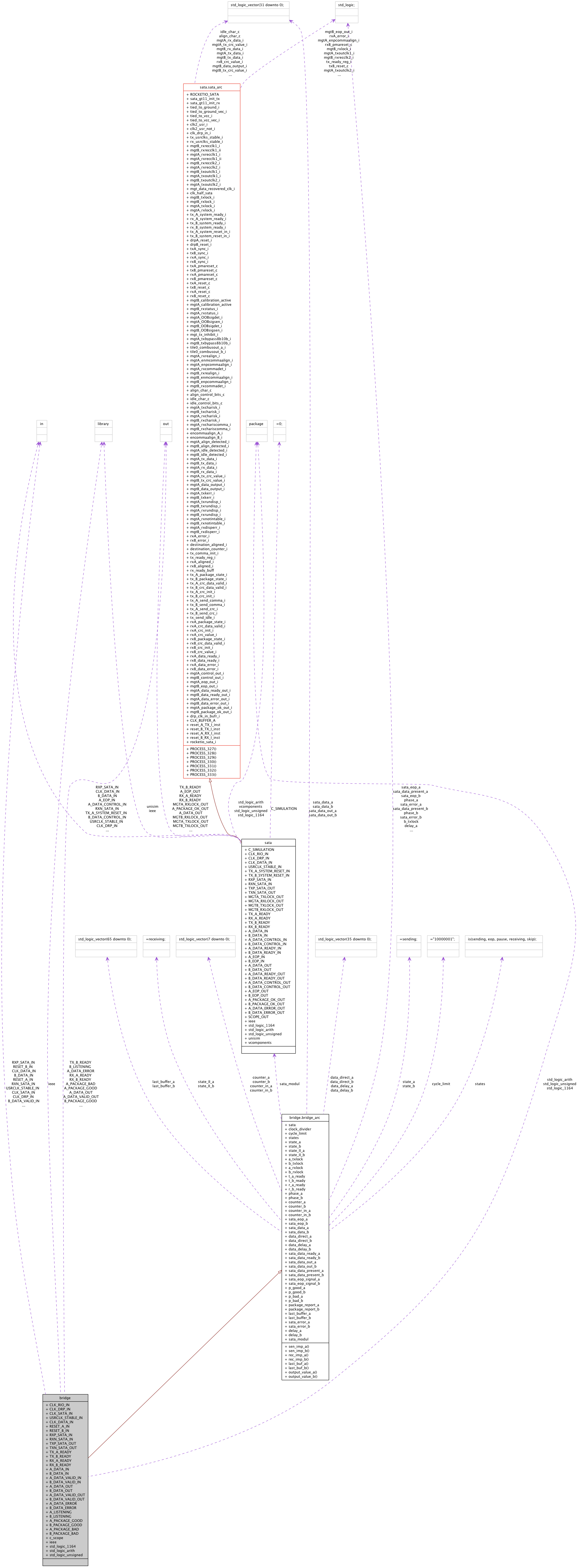

Inheritance diagram for bridge:

Collaboration diagram for bridge:

Architectures | |

| bridge_arc | Architecture |

| top module of SATA More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

Ports | |

| CLK_RIO_IN | in std_logic |

| RIOs reference clock. | |

| CLK_DRP_IN | in std_logic |

| 50MHz system clock for PLL correction (used) and DRP (nou used), used also for reset clocking since it is slover than TXOUTCLK1/2 = 75 MHz | |

| CLK_SATA_IN | in std_logic |

| clock for data Retrieval from rio (80 MHz) | |

| USRCLK_STABLE_IN | in std_logic |

| indicates a stable input clocks | |

| CLK_DATA_IN | in std_logic |

| clock for data interface (40 MHz) | |

| RESET_A_IN | in std_logic |

| reset | |

| RESET_B_IN | in std_logic |

| reset | |

| RXP_SATA_IN | in std_logic_vector ( 1 downto 0 ) |

| package pins | |

| RXN_SATA_IN | in std_logic_vector ( 1 downto 0 ) |

| package pins | |

| TXP_SATA_OUT | out std_logic_vector ( 1 downto 0 ) |

| package pins | |

| TXN_SATA_OUT | out std_logic_vector ( 1 downto 0 ) |

| package pins | |

| TX_A_READY | out std_logic |

| transmitrers ready | |

| TX_B_READY | out std_logic |

| transmitrers ready | |

| RX_A_READY | out std_logic |

| receivers ready | |

| RX_B_READY | out std_logic |

| receivers ready | |

| A_DATA_IN | in std_logic_vector ( 63 downto 0 ) |

| data to be send | |

| B_DATA_IN | in std_logic_vector ( 63 downto 0 ) |

| data to be send | |

| A_DATA_VALID_IN | in std_logic |

| when '1' the data is transmitted | |

| B_DATA_VALID_IN | in std_logic |

| when '1' the data is transmitted | |

| A_DATA_OUT | out std_logic_vector ( 63 downto 0 ) |

| data from the other side | |

| B_DATA_OUT | out std_logic_vector ( 63 downto 0 ) |

| data from the other side | |

| A_DATA_VALID_OUT | out std_logic |

| when '1' the data is ready to be read | |

| B_DATA_VALID_OUT | out std_logic |

| when '1' the data is ready to be read | |

| A_DATA_ERROR | out std_logic |

| value '1' indicates that an error ocured and the data can not be trusted | |

| B_DATA_ERROR | out std_logic |

| value '1' indicates that an error ocured and the data can not be trusted | |

| A_LISTENING | out std_logic |

| when '1' the data will be send | |

| B_LISTENING | out std_logic |

| when '1' the data will be send | |

| A_PACKAGE_GOOD | out std_logic |

| signals that the previous package was good | |

| B_PACKAGE_GOOD | out std_logic |

| signals that the previous package was good | |

| A_PACKAGE_BAD | out std_logic |

| signals that an error occured in the previous package | |

| B_PACKAGE_BAD | out std_logic |

| signals that an error occured in the previous package | |

| c_scope | out std_logic_vector ( 165 downto 0 ) |

| ChipScope probe. | |

Detailed Description

top module of SATADefinition at line 33 of file bridge.vhd.

Member Data Documentation

A_DATA_ERROR out std_logic [Port] |

value '1' indicates that an error ocured and the data can not be trusted

Definition at line 63 of file bridge.vhd.

A_DATA_IN in std_logic_vector ( 63 downto 0 ) [Port] |

A_DATA_OUT out std_logic_vector ( 63 downto 0 ) [Port] |

A_DATA_VALID_IN in std_logic [Port] |

A_DATA_VALID_OUT out std_logic [Port] |

A_LISTENING out std_logic [Port] |

A_PACKAGE_BAD out std_logic [Port] |

A_PACKAGE_GOOD out std_logic [Port] |

B_DATA_ERROR out std_logic [Port] |

value '1' indicates that an error ocured and the data can not be trusted

Definition at line 64 of file bridge.vhd.

B_DATA_IN in std_logic_vector ( 63 downto 0 ) [Port] |

B_DATA_OUT out std_logic_vector ( 63 downto 0 ) [Port] |

B_DATA_VALID_IN in std_logic [Port] |

B_DATA_VALID_OUT out std_logic [Port] |

B_LISTENING out std_logic [Port] |

B_PACKAGE_BAD out std_logic [Port] |

B_PACKAGE_GOOD out std_logic [Port] |

c_scope out std_logic_vector ( 165 downto 0 ) [Port] |

CLK_DATA_IN in std_logic [Port] |

CLK_DRP_IN in std_logic [Port] |

50MHz system clock for PLL correction (used) and DRP (nou used), used also for reset clocking since it is slover than TXOUTCLK1/2 = 75 MHz

Definition at line 37 of file bridge.vhd.

CLK_RIO_IN in std_logic [Port] |

CLK_SATA_IN in std_logic [Port] |

ieee library [Library] |

RESET_A_IN in std_logic [Port] |

RESET_B_IN in std_logic [Port] |

RX_A_READY out std_logic [Port] |

RX_B_READY out std_logic [Port] |

RXN_SATA_IN in std_logic_vector ( 1 downto 0 ) [Port] |

RXP_SATA_IN in std_logic_vector ( 1 downto 0 ) [Port] |

std_logic_1164 package [Package] |

std_logic definitions, see file

Reimplemented in main_components.

Definition at line 26 of file bridge.vhd.

std_logic_arith package [Package] |

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 30 of file bridge.vhd.

TX_A_READY out std_logic [Port] |

TX_B_READY out std_logic [Port] |

TXN_SATA_OUT out std_logic_vector ( 1 downto 0 ) [Port] |

TXP_SATA_OUT out std_logic_vector ( 1 downto 0 ) [Port] |

USRCLK_STABLE_IN in std_logic [Port] |

The documentation for this class was generated from the following file: