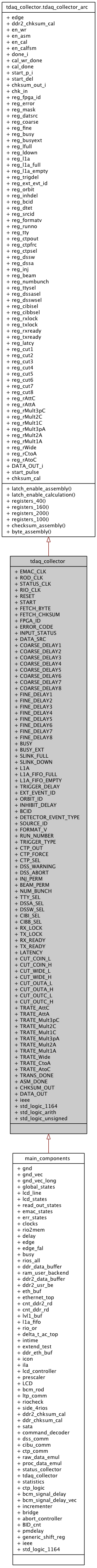

tdaq_collector Entity Reference

Data collector for TDAQ status messages. More...

Architectures | |

| tdaq_collector_arc | Architecture |

| Data collector for status messages. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

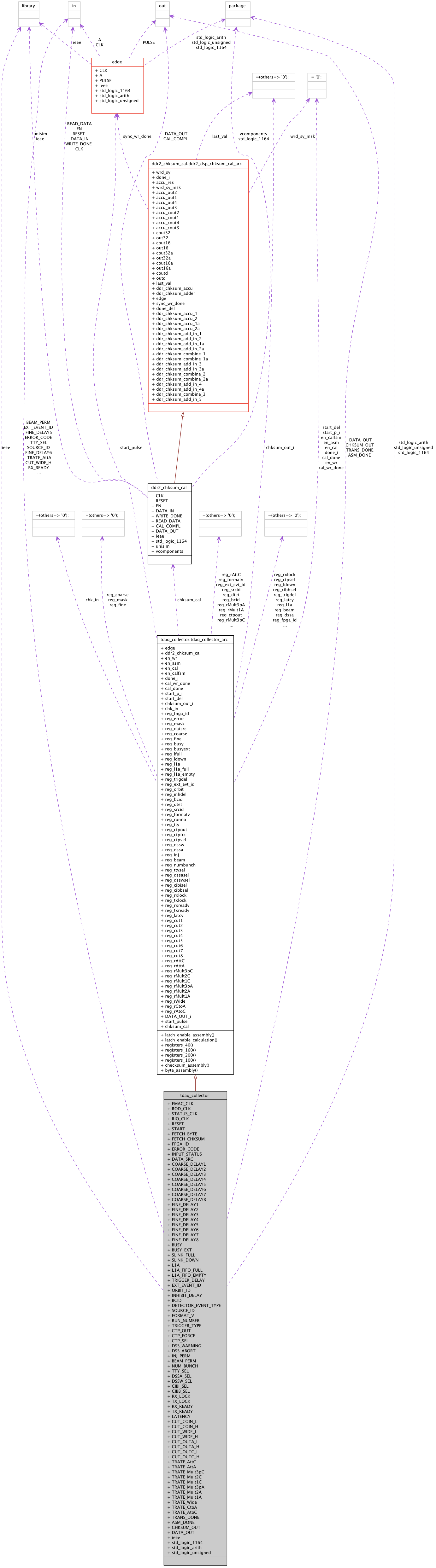

Ports | |

| EMAC_CLK | in std_logic |

| 100 MHz | |

| ROD_CLK | in std_logic |

| 40 MHz | |

| STATUS_CLK | in std_logic |

| 200 MHz | |

| RIO_CLK | in std_logic |

| 160 MHz | |

| RESET | in std_logic |

| Reset. | |

| START | in std_logic |

| Start assembling packet. | |

| FETCH_BYTE | in std_logic |

| Get data byte, hold high until TRANS_DONE = 1. | |

| FETCH_CHKSUM | in std_logic |

| Get checksum, set for 1 clk cycle. | |

| FPGA_ID | in std_logic_vector ( 7 downto 0 ) := x " 00 " |

| FPGA ID. | |

| ERROR_CODE | in std_logic_vector ( 7 downto 0 ) |

| Error code. | |

| INPUT_STATUS | in std_logic_vector ( 63 downto 0 ) |

| Status of inputs, ie active or masked. | |

| DATA_SRC | in std_logic_vector ( 7 downto 0 ) |

| 0xff = Detector, 0x00 = Pattern Generator | |

| COARSE_DELAY1 | in std_logic_vector ( 7 downto 0 ) |

| Coarse Delay Ch1. | |

| COARSE_DELAY2 | in std_logic_vector ( 7 downto 0 ) |

| Coarse Delay Ch2. | |

| COARSE_DELAY3 | in std_logic_vector ( 7 downto 0 ) |

| Coarse Delay Ch3. | |

| COARSE_DELAY4 | in std_logic_vector ( 7 downto 0 ) |

| Coarse Delay Ch4. | |

| COARSE_DELAY5 | in std_logic_vector ( 7 downto 0 ) |

| Coarse Delay Ch5. | |

| COARSE_DELAY6 | in std_logic_vector ( 7 downto 0 ) |

| Coarse Delay Ch6. | |

| COARSE_DELAY7 | in std_logic_vector ( 7 downto 0 ) |

| Coarse Delay Ch7. | |

| COARSE_DELAY8 | in std_logic_vector ( 7 downto 0 ) |

| Coarse Delay Ch8. | |

| FINE_DELAY1 | in std_logic_vector ( 7 downto 0 ) |

| Fine Delay Ch1. | |

| FINE_DELAY2 | in std_logic_vector ( 7 downto 0 ) |

| Fine Delay Ch2. | |

| FINE_DELAY3 | in std_logic_vector ( 7 downto 0 ) |

| Fine Delay Ch3. | |

| FINE_DELAY4 | in std_logic_vector ( 7 downto 0 ) |

| Fine Delay Ch4. | |

| FINE_DELAY5 | in std_logic_vector ( 7 downto 0 ) |

| Fine Delay Ch5. | |

| FINE_DELAY6 | in std_logic_vector ( 7 downto 0 ) |

| Fine Delay Ch6. | |

| FINE_DELAY7 | in std_logic_vector ( 7 downto 0 ) |

| Fine Delay Ch7. | |

| FINE_DELAY8 | in std_logic_vector ( 7 downto 0 ) |

| Fine Delay Ch8. | |

| BUSY | in std_logic_vector ( 7 downto 0 ) |

| Busy flag. | |

| BUSY_EXT | in std_logic_vector ( 7 downto 0 ) |

| Busy flag set by TDAQ. | |

| SLINK_FULL | in std_logic_vector ( 7 downto 0 ) |

| Link full flag. | |

| SLINK_DOWN | in std_logic_vector ( 7 downto 0 ) |

| Link down flag. | |

| L1A | in std_logic |

| Level-1 Accept. | |

| L1A_FIFO_FULL | in std_logic |

| L1A FIFO Status. | |

| L1A_FIFO_EMPTY | in std_logic |

| L1A FIFO Status. | |

| TRIGGER_DELAY | in std_logic_vector ( 7 downto 0 ) |

| L1A Trigger delay. | |

| EXT_EVENT_ID | in std_logic_vector ( 31 downto 0 ) |

| Extended Level-1 Event ID (L1A Cnt & ECR Cnt). | |

| ORBIT_ID | in std_logic_vector ( 31 downto 0 ) |

| Orbit ID. | |

| INHIBIT_DELAY | in std_logic_vector ( 7 downto 0 ) |

| Inhibit Delay. | |

| BCID | in std_logic_vector ( 31 downto 0 ) |

| Bunch ID. | |

| DETECTOR_EVENT_TYPE | in std_logic_vector ( 31 downto 0 ) |

| Detector Event Type. | |

| SOURCE_ID | in std_logic_vector ( 31 downto 0 ) |

| ROD Source ID. | |

| FORMAT_V | in std_logic_vector ( 31 downto 0 ) |

| ROD Format Version. | |

| RUN_NUMBER | in std_logic_vector ( 31 downto 0 ) |

| ATLAS run number. | |

| TRIGGER_TYPE | in std_logic_vector ( 7 downto 0 ) |

| L1A Type. | |

| CTP_OUT | in std_logic_vector ( 8 downto 0 ) |

| Status of CTP Outputs. | |

| CTP_FORCE | in std_logic_vector ( 8 downto 0 ) |

| CTP Pattern forced by PC. | |

| CTP_SEL | in std_logic_vector ( 7 downto 0 ) |

| Source for CTP Outs, 0xff = intern, 0x00 = extern. | |

| DSS_WARNING | in std_logic |

| DSS Warning Out value. | |

| DSS_ABORT | in std_logic |

| DSS Abort Out value. | |

| INJ_PERM | in std_logic |

| Injection Permit Out value. | |

| BEAM_PERM | in std_logic |

| Beam Permit Out value. | |

| NUM_BUNCH | in std_logic_vector ( 7 downto 0 ) |

| Number of bunches per L1A. | |

| TTY_SEL | in std_logic_vector ( 7 downto 0 ) |

| Source for Trigger Type, 0xff = intern, 0x00 = extern. | |

| DSSA_SEL | in std_logic_vector ( 7 downto 0 ) |

| Source for DSS Abort Out, 0xff = intern, 0x00 = extern. | |

| DSSW_SEL | in std_logic_vector ( 7 downto 0 ) |

| Source for DSS Abort Out, 0xff = intern, 0x00 = extern. | |

| CIBI_SEL | in std_logic_vector ( 7 downto 0 ) |

| Source for CIBU Outs, 0xff = intern, 0x00 = extern. | |

| CIBB_SEL | in std_logic_vector ( 7 downto 0 ) |

| Source for CIBU Outs, 0xff = intern, 0x00 = extern. | |

| RX_LOCK | in std_logic_vector ( 7 downto 0 ) |

| RIO status. | |

| TX_LOCK | in std_logic_vector ( 7 downto 0 ) |

| RIO status. | |

| RX_READY | in std_logic_vector ( 7 downto 0 ) |

| RIO status. | |

| TX_READY | in std_logic_vector ( 7 downto 0 ) |

| RIO status. | |

| LATENCY | in std_logic_vector ( 7 downto 0 ) |

| readout latency | |

| CUT_COIN_L | in std_logic_vector ( 7 downto 0 ) |

| Time cut in-time coincidence. | |

| CUT_COIN_H | in std_logic_vector ( 7 downto 0 ) |

| Time cut in-time coincidence. | |

| CUT_WIDE_L | in std_logic_vector ( 7 downto 0 ) |

| Wide in-time time cut. | |

| CUT_WIDE_H | in std_logic_vector ( 7 downto 0 ) |

| Wide in-time time cut. | |

| CUT_OUTA_L | in std_logic_vector ( 7 downto 0 ) |

| Out-of-time cut side A. | |

| CUT_OUTA_H | in std_logic_vector ( 7 downto 0 ) |

| Out-of-time cut side A. | |

| CUT_OUTC_L | in std_logic_vector ( 7 downto 0 ) |

| Out-of-time cut side C. | |

| CUT_OUTC_H | in std_logic_vector ( 7 downto 0 ) |

| Out-of-time cut side A. | |

| TRATE_AttC | in std_logic_vector ( 31 downto 0 ) |

| Trigger rate. | |

| TRATE_AttA | in std_logic_vector ( 31 downto 0 ) |

| Trigger rate. | |

| TRATE_Mult3pC | in std_logic_vector ( 31 downto 0 ) |

| Trigger rate. | |

| TRATE_Mult2C | in std_logic_vector ( 31 downto 0 ) |

| Trigger rate. | |

| TRATE_Mult1C | in std_logic_vector ( 31 downto 0 ) |

| Trigger rate. | |

| TRATE_Mult3pA | in std_logic_vector ( 31 downto 0 ) |

| Trigger rate. | |

| TRATE_Mult2A | in std_logic_vector ( 31 downto 0 ) |

| Trigger rate. | |

| TRATE_Mult1A | in std_logic_vector ( 31 downto 0 ) |

| Trigger rate. | |

| TRATE_Wide | in std_logic_vector ( 31 downto 0 ) |

| Trigger rate. | |

| TRATE_CtoA | in std_logic_vector ( 31 downto 0 ) |

| Trigger rate. | |

| TRATE_AtoC | in std_logic_vector ( 31 downto 0 ) |

| Trigger rate. | |

| TRANS_DONE | out std_logic |

| Transfer of full packet done. | |

| ASM_DONE | out std_logic |

| Packet assembly done, set FETCH_BYTE & FETCH_CHKSUM afterwards. | |

| CHKSUM_OUT | out std_logic_vector ( 15 downto 0 ) |

| Checksum out to EMAC. | |

| DATA_OUT | out std_logic_vector ( 7 downto 0 ) |

| Data byte to EMAC. | |

Detailed Description

Data collector for TDAQ status messages.This entity collects all the data for the TDAQ status messages. It synchronizes all inputs from various clock domains to 100 MHz, puts them in the correct byte order & computes the UDP checksum. When everything is done an output flag is asserted.

Definition at line 38 of file tdaq_collector.vhd.

Member Data Documentation

ASM_DONE out std_logic [Port] |

Packet assembly done, set FETCH_BYTE & FETCH_CHKSUM afterwards.

Definition at line 124 of file tdaq_collector.vhd.

BCID in std_logic_vector ( 31 downto 0 ) [Port] |

BEAM_PERM in std_logic [Port] |

BUSY in std_logic_vector ( 7 downto 0 ) [Port] |

BUSY_EXT in std_logic_vector ( 7 downto 0 ) [Port] |

CHKSUM_OUT out std_logic_vector ( 15 downto 0 ) [Port] |

CIBB_SEL in std_logic_vector ( 7 downto 0 ) [Port] |

Source for CIBU Outs, 0xff = intern, 0x00 = extern.

Definition at line 98 of file tdaq_collector.vhd.

CIBI_SEL in std_logic_vector ( 7 downto 0 ) [Port] |

Source for CIBU Outs, 0xff = intern, 0x00 = extern.

Definition at line 97 of file tdaq_collector.vhd.

COARSE_DELAY1 in std_logic_vector ( 7 downto 0 ) [Port] |

COARSE_DELAY2 in std_logic_vector ( 7 downto 0 ) [Port] |

COARSE_DELAY3 in std_logic_vector ( 7 downto 0 ) [Port] |

COARSE_DELAY4 in std_logic_vector ( 7 downto 0 ) [Port] |

COARSE_DELAY5 in std_logic_vector ( 7 downto 0 ) [Port] |

COARSE_DELAY6 in std_logic_vector ( 7 downto 0 ) [Port] |

COARSE_DELAY7 in std_logic_vector ( 7 downto 0 ) [Port] |

COARSE_DELAY8 in std_logic_vector ( 7 downto 0 ) [Port] |

CTP_FORCE in std_logic_vector ( 8 downto 0 ) [Port] |

CTP_OUT in std_logic_vector ( 8 downto 0 ) [Port] |

CTP_SEL in std_logic_vector ( 7 downto 0 ) [Port] |

Source for CTP Outs, 0xff = intern, 0x00 = extern.

Definition at line 88 of file tdaq_collector.vhd.

CUT_COIN_H in std_logic_vector ( 7 downto 0 ) [Port] |

CUT_COIN_L in std_logic_vector ( 7 downto 0 ) [Port] |

CUT_OUTA_H in std_logic_vector ( 7 downto 0 ) [Port] |

CUT_OUTA_L in std_logic_vector ( 7 downto 0 ) [Port] |

CUT_OUTC_H in std_logic_vector ( 7 downto 0 ) [Port] |

CUT_OUTC_L in std_logic_vector ( 7 downto 0 ) [Port] |

CUT_WIDE_H in std_logic_vector ( 7 downto 0 ) [Port] |

CUT_WIDE_L in std_logic_vector ( 7 downto 0 ) [Port] |

DATA_OUT out std_logic_vector ( 7 downto 0 ) [Port] |

DATA_SRC in std_logic_vector ( 7 downto 0 ) [Port] |

DETECTOR_EVENT_TYPE in std_logic_vector ( 31 downto 0 ) [Port] |

DSS_ABORT in std_logic [Port] |

DSS_WARNING in std_logic [Port] |

DSSA_SEL in std_logic_vector ( 7 downto 0 ) [Port] |

Source for DSS Abort Out, 0xff = intern, 0x00 = extern.

Definition at line 95 of file tdaq_collector.vhd.

DSSW_SEL in std_logic_vector ( 7 downto 0 ) [Port] |

Source for DSS Abort Out, 0xff = intern, 0x00 = extern.

Definition at line 96 of file tdaq_collector.vhd.

EMAC_CLK in std_logic [Port] |

ERROR_CODE in std_logic_vector ( 7 downto 0 ) [Port] |

EXT_EVENT_ID in std_logic_vector ( 31 downto 0 ) [Port] |

FETCH_BYTE in std_logic [Port] |

FETCH_CHKSUM in std_logic [Port] |

FINE_DELAY1 in std_logic_vector ( 7 downto 0 ) [Port] |

FINE_DELAY2 in std_logic_vector ( 7 downto 0 ) [Port] |

FINE_DELAY3 in std_logic_vector ( 7 downto 0 ) [Port] |

FINE_DELAY4 in std_logic_vector ( 7 downto 0 ) [Port] |

FINE_DELAY5 in std_logic_vector ( 7 downto 0 ) [Port] |

FINE_DELAY6 in std_logic_vector ( 7 downto 0 ) [Port] |

FINE_DELAY7 in std_logic_vector ( 7 downto 0 ) [Port] |

FINE_DELAY8 in std_logic_vector ( 7 downto 0 ) [Port] |

FORMAT_V in std_logic_vector ( 31 downto 0 ) [Port] |

FPGA_ID in std_logic_vector ( 7 downto 0 ) := x " 00 " [Port] |

ieee library [Library] |

standard IEEE library

Reimplemented in main_components.

Definition at line 25 of file tdaq_collector.vhd.

INHIBIT_DELAY in std_logic_vector ( 7 downto 0 ) [Port] |

INJ_PERM in std_logic [Port] |

INPUT_STATUS in std_logic_vector ( 63 downto 0 ) [Port] |

L1A in std_logic [Port] |

L1A_FIFO_EMPTY in std_logic [Port] |

L1A_FIFO_FULL in std_logic [Port] |

LATENCY in std_logic_vector ( 7 downto 0 ) [Port] |

NUM_BUNCH in std_logic_vector ( 7 downto 0 ) [Port] |

ORBIT_ID in std_logic_vector ( 31 downto 0 ) [Port] |

RESET in std_logic [Port] |

RIO_CLK in std_logic [Port] |

ROD_CLK in std_logic [Port] |

RUN_NUMBER in std_logic_vector ( 31 downto 0 ) [Port] |

RX_LOCK in std_logic_vector ( 7 downto 0 ) [Port] |

RX_READY in std_logic_vector ( 7 downto 0 ) [Port] |

SLINK_DOWN in std_logic_vector ( 7 downto 0 ) [Port] |

SLINK_FULL in std_logic_vector ( 7 downto 0 ) [Port] |

SOURCE_ID in std_logic_vector ( 31 downto 0 ) [Port] |

START in std_logic [Port] |

STATUS_CLK in std_logic [Port] |

std_logic_1164 package [Package] |

std_logic definitions, see file

Reimplemented in main_components.

Definition at line 27 of file tdaq_collector.vhd.

std_logic_arith package [Package] |

arithmetic operations on std_logic datatypes, see file

Definition at line 29 of file tdaq_collector.vhd.

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 31 of file tdaq_collector.vhd.

TRANS_DONE out std_logic [Port] |

TRATE_AtoC in std_logic_vector ( 31 downto 0 ) [Port] |

TRATE_AttA in std_logic_vector ( 31 downto 0 ) [Port] |

TRATE_AttC in std_logic_vector ( 31 downto 0 ) [Port] |

TRATE_CtoA in std_logic_vector ( 31 downto 0 ) [Port] |

TRATE_Mult1A in std_logic_vector ( 31 downto 0 ) [Port] |

TRATE_Mult1C in std_logic_vector ( 31 downto 0 ) [Port] |

TRATE_Mult2A in std_logic_vector ( 31 downto 0 ) [Port] |

TRATE_Mult2C in std_logic_vector ( 31 downto 0 ) [Port] |

TRATE_Mult3pA in std_logic_vector ( 31 downto 0 ) [Port] |

TRATE_Mult3pC in std_logic_vector ( 31 downto 0 ) [Port] |

TRATE_Wide in std_logic_vector ( 31 downto 0 ) [Port] |

TRIGGER_DELAY in std_logic_vector ( 7 downto 0 ) [Port] |

TRIGGER_TYPE in std_logic_vector ( 7 downto 0 ) [Port] |

TTY_SEL in std_logic_vector ( 7 downto 0 ) [Port] |

Source for Trigger Type, 0xff = intern, 0x00 = extern.

Definition at line 94 of file tdaq_collector.vhd.

TX_LOCK in std_logic_vector ( 7 downto 0 ) [Port] |

TX_READY in std_logic_vector ( 7 downto 0 ) [Port] |

The documentation for this class was generated from the following file: