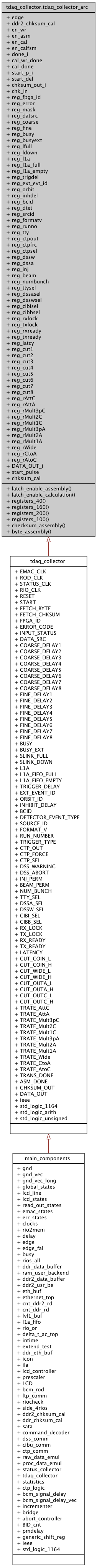

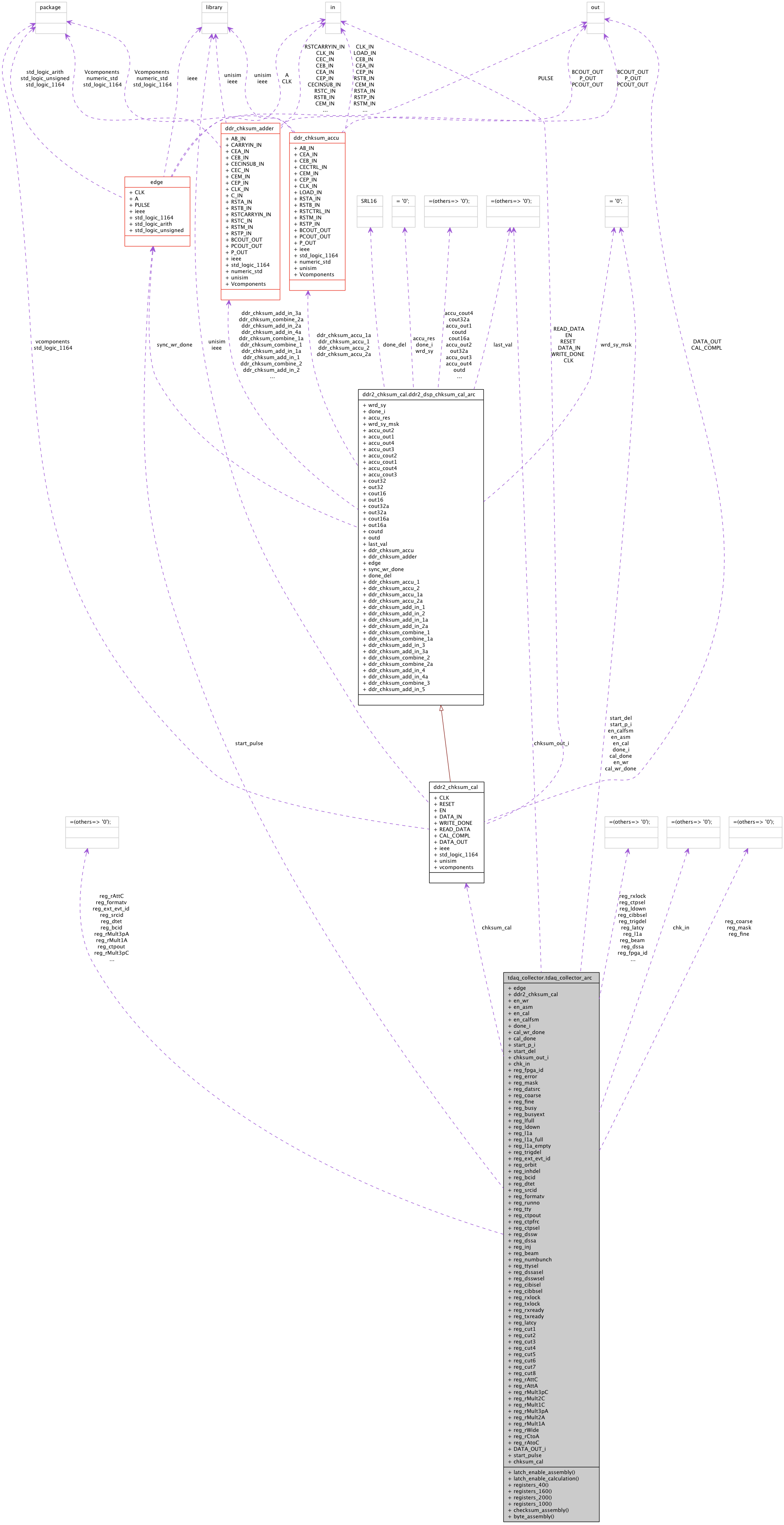

tdaq_collector.tdaq_collector_arc Architecture Reference

Data collector for status messages. More...

Processes | |

| latch_enable_assembly | ( EMAC_CLK , RESET ) |

| enable for general assembly | |

| latch_enable_calculation | ( EMAC_CLK , RESET ) |

| enable for chksum assembly FSM | |

| registers_40 | ( ROD_CLK , RESET ) |

| 40 MHz registers | |

| registers_160 | ( RIO_CLK , RESET ) |

| 160 MHz registers | |

| registers_200 | ( STATUS_CLK , RESET ) |

| 200 MHz registers | |

| registers_100 | ( EMAC_CLK , RESET ) |

| 100 MHz registers | |

| checksum_assembly | ( EMAC_CLK , RESET ) |

| assemble for checksum calculation | |

| byte_assembly | ( EMAC_CLK , RESET ) |

Components | |

| edge | <Entity edge> |

| edge detection | |

| ddr2_chksum_cal | <Entity ddr2_chksum_cal> |

| checksum calculation | |

Signals | |

| en_wr | std_logic := ' 0 ' |

| en_asm | std_logic := ' 0 ' |

| en_cal | std_logic := ' 0 ' |

| en_calfsm | std_logic := ' 0 ' |

| done_i | std_logic := ' 0 ' |

| cal_wr_done | std_logic := ' 0 ' |

| cal_done | std_logic := ' 0 ' |

| start_p_i | std_logic := ' 0 ' |

| start_del | std_logic := ' 0 ' |

| chksum_out_i | std_logic_vector ( 15 downto 0 ) := ( others = > ' 0 ' ) |

| chk_in | std_logic_vector ( 127 downto 0 ) := ( others = > ' 0 ' ) |

| reg_fpga_id | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_error | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_mask | std_logic_vector ( 63 downto 0 ) := ( others = > ' 0 ' ) |

| reg_datsrc | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_coarse | std_logic_vector ( 63 downto 0 ) := ( others = > ' 0 ' ) |

| reg_fine | std_logic_vector ( 63 downto 0 ) := ( others = > ' 0 ' ) |

| reg_busy | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_busyext | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_lfull | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_ldown | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_l1a | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_l1a_full | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_l1a_empty | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_trigdel | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_ext_evt_id | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_orbit | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_inhdel | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_bcid | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_dtet | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_srcid | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_formatv | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_runno | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_tty | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_ctpout | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_ctpfrc | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_ctpsel | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_dssw | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_dssa | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_inj | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_beam | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_numbunch | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_ttysel | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_dssasel | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_dsswsel | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_cibisel | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_cibbsel | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_rxlock | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_txlock | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_rxready | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_txready | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_latcy | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_cut1 | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_cut2 | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_cut3 | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_cut4 | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_cut5 | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_cut6 | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_cut7 | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_cut8 | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_rAttC | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_rAttA | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_rMult3pC | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_rMult2C | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_rMult1C | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_rMult3pA | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_rMult2A | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_rMult1A | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_rWide | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_rCtoA | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_rAtoC | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| DATA_OUT_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

Component Instantiations | |

| start_pulse | edge <Entity edge> |

| make start pulse | |

| chksum_cal | ddr2_chksum_cal <Entity ddr2_chksum_cal> |

| checksum calculation | |

Detailed Description

Data collector for status messages.This architecture collects all the data for the TDAQ status messages. It synchronizes all inputs from various clock domains to 100 MHz, puts them in the correct byte order & computes the UDP checksum. When everything is done an output flag is asserted.

Definition at line 136 of file tdaq_collector.vhd.

Member Function Documentation

| checksum_assembly | ( EMAC_CLK , | |

| RESET ) |

assemble for checksum calculation

Definition at line 473 of file tdaq_collector.vhd.

00473 checksum_assembly : process (EMAC_CLK, RESET) 00474 variable cnt : integer range 0 to 31 := 0; 00475 begin -- process checksum_assembly 00476 if RESET = '1' then -- asynchronous reset (active high) 00477 chk_in <= (others => '0'); 00478 en_cal <= '0'; 00479 cal_wr_done <= '0'; 00480 cnt := 0; 00481 elsif EMAC_CLK'event and EMAC_CLK = '1' then -- rising clock edge 00482 if en_calfsm = '1' then 00483 en_cal <= '1'; 00484 cal_wr_done <= '0'; 00485 case cnt is 00486 when 0 => chk_in <= reg_fpga_id & reg_error & reg_mask & reg_datsrc & reg_coarse(63 downto 24); 00487 when 1 => chk_in <= reg_coarse(23 downto 0) & reg_fine & reg_busy & reg_busyext & reg_lfull & 00488 reg_ldown & reg_l1a; 00489 when 2 => chk_in <= reg_l1a_full & reg_l1a_empty & reg_trigdel & reg_ext_evt_id & 00490 reg_orbit & reg_inhdel & reg_bcid; 00491 when 3 => chk_in <= reg_dtet & reg_srcid & reg_formatv & reg_runno; 00492 when 4 => chk_in <= reg_tty & reg_ctpout & reg_ctpfrc & reg_ctpsel & reg_dssw & reg_dssa & reg_inj & 00493 reg_beam & reg_numbunch & reg_ttysel; 00494 when 5 => chk_in <= reg_dsswsel & reg_dssasel & reg_cibisel & reg_cibbsel & reg_rxlock & 00495 reg_txlock & reg_rxready & reg_txready & reg_latcy & reg_rAttC & reg_rAttA(31 downto 8); 00496 when 6 => chk_in <= reg_rAttA(7 downto 0) & reg_rMult3pC & reg_rMult2C & reg_rMult1C & reg_rMult3pA(31 downto 8); 00497 when 7 => chk_in <= reg_rMult3pA(7 downto 0) & reg_rMult2A & reg_rMult1A & reg_rWide & reg_rCtoA(31 downto 8); 00498 when 8 => chk_in <= reg_rCtoA(7 downto 0) & reg_rAtoC & x"00_00_00_00_00_00_00_00_00_00_00"; 00499 when 9 => chk_in <= (others => '0'); 00500 cal_wr_done <= '1'; 00501 when others => chk_in <= (others => '0'); 00502 cal_wr_done <= '0'; 00503 end case; 00504 cnt := cnt + 1; 00505 else 00506 cnt := 0; 00507 chk_in <= (others => '0'); 00508 cal_wr_done <= '0'; 00509 en_cal <= '0'; 00510 end if; 00511 end if; 00512 end process checksum_assembly;

| latch_enable_assembly | ( EMAC_CLK , | |

| RESET ) |

enable for general assembly

Definition at line 249 of file tdaq_collector.vhd.

00249 latch_enable_assembly : process (EMAC_CLK, RESET) 00250 begin -- process latch_enable_assembly 00251 if RESET = '1' then -- asynchronous reset (active high) 00252 en_asm <= '0'; 00253 elsif EMAC_CLK'event and EMAC_CLK = '1' then -- rising clock edge 00254 if start_del = '1' then 00255 en_asm <= '1'; 00256 elsif done_i = '1' then 00257 en_asm <= '0'; 00258 end if; 00259 end if; 00260 end process latch_enable_assembly;

| latch_enable_calculation | ( EMAC_CLK , | |

| RESET ) |

enable for chksum assembly FSM

Definition at line 263 of file tdaq_collector.vhd.

00263 latch_enable_calculation : process (EMAC_CLK, RESET) 00264 begin -- process latch_enable_assembly 00265 if RESET = '1' then -- asynchronous reset (active high) 00266 en_calfsm <= '0'; 00267 elsif EMAC_CLK'event and EMAC_CLK = '1' then -- rising clock edge 00268 if start_p_i = '1' then 00269 en_calfsm <= '1'; 00270 elsif cal_wr_done = '1' then 00271 en_calfsm <= '0'; 00272 end if; 00273 end if; 00274 end process latch_enable_calculation;

| registers_100 | ( EMAC_CLK , | |

| RESET ) |

100 MHz registers

Definition at line 459 of file tdaq_collector.vhd.

00459 registers_100 : process (EMAC_CLK, RESET) 00460 begin -- process registers 00461 if RESET = '1' then -- asynchronous reset (active high) 00462 reg_fpga_id <= (others => '0'); 00463 reg_numbunch <= (others => '0'); 00464 elsif EMAC_CLK'event and EMAC_CLK = '1' then 00465 if en_wr = '1' then 00466 reg_fpga_id <= FPGA_ID; 00467 reg_numbunch <= NUM_BUNCH; 00468 end if; 00469 end if; 00470 end process registers_100;

| registers_160 | ( RIO_CLK , | |

| RESET ) |

160 MHz registers

Definition at line 427 of file tdaq_collector.vhd.

00427 registers_160 : process (RIO_CLK, RESET) 00428 begin -- process registers 00429 if RESET = '1' then -- asynchronous reset (active high) 00430 reg_mask <= (others => '0'); 00431 reg_rxready <= (others => '0'); 00432 reg_rxlock <= (others => '0'); 00433 reg_txready <= (others => '0'); 00434 reg_txlock <= (others => '0'); 00435 elsif RIO_CLK'event and RIO_CLK = '1' then 00436 if en_wr = '1' then 00437 reg_mask <= INPUT_STATUS; 00438 reg_rxlock <= RX_LOCK; 00439 reg_rxready <= RX_READY; 00440 reg_txlock <= TX_LOCK; 00441 reg_txready <= TX_READY; 00442 end if; 00443 end if; 00444 end process registers_160;

| registers_200 | ( STATUS_CLK , | |

| RESET ) |

200 MHz registers

Definition at line 447 of file tdaq_collector.vhd.

00447 registers_200 : process (STATUS_CLK, RESET) 00448 begin -- process registers 00449 if RESET = '1' then -- asynchronous reset (active high) 00450 reg_error <= (others => '0'); 00451 elsif STATUS_CLK'event and STATUS_CLK = '1' then 00452 if en_wr = '1' then 00453 reg_error <= ERROR_CODE; 00454 end if; 00455 end if; 00456 end process registers_200;

| registers_40 | ( ROD_CLK , | |

| RESET ) |

40 MHz registers

Definition at line 283 of file tdaq_collector.vhd.

00283 registers_40 : process (ROD_CLK, RESET) 00284 begin -- process registers 00285 if RESET = '1' then -- asynchronous reset (active high) 00286 reg_coarse <= (others => '0'); 00287 reg_datsrc <= (others => '0'); 00288 reg_fine <= (others => '0'); 00289 reg_busy <= (others => '0'); 00290 reg_busyext <= (others => '0'); 00291 reg_lfull <= (others => '0'); 00292 reg_ldown <= (others => '0'); 00293 reg_l1a <= (others => '0'); 00294 reg_l1a_full <= (others => '0'); 00295 reg_l1a_empty <= (others => '0'); 00296 reg_trigdel <= (others => '0'); 00297 reg_ext_evt_id <= (others => '0'); 00298 reg_orbit <= (others => '0'); 00299 reg_inhdel <= (others => '0'); 00300 reg_bcid <= (others => '0'); 00301 reg_dtet <= (others => '0'); 00302 reg_srcid <= (others => '0'); 00303 reg_formatv <= (others => '0'); 00304 reg_runno <= (others => '0'); 00305 reg_tty <= (others => '0'); 00306 reg_ctpout(8 downto 0) <= (others => '0'); 00307 reg_ctpfrc(8 downto 0) <= (others => '0'); 00308 reg_ctpsel <= (others => '0'); 00309 reg_ttysel <= (others => '0'); 00310 reg_dssasel <= (others => '0'); 00311 reg_dsswsel <= (others => '0'); 00312 reg_cibisel <= (others => '0'); 00313 reg_cibbsel <= (others => '0'); 00314 reg_dssw <= (others => '0'); 00315 reg_dssa <= (others => '0'); 00316 reg_inj <= (others => '0'); 00317 reg_beam <= (others => '0'); 00318 reg_latcy <= (others => '0'); 00319 reg_cut1 <= (others => '0'); 00320 reg_cut2 <= (others => '0'); 00321 reg_cut3 <= (others => '0'); 00322 reg_cut4 <= (others => '0'); 00323 reg_cut5 <= (others => '0'); 00324 reg_cut6 <= (others => '0'); 00325 reg_cut7 <= (others => '0'); 00326 reg_cut8 <= (others => '0'); 00327 reg_rAttC <= (others => '0'); 00328 reg_rAttA <= (others => '0'); 00329 reg_rMult3pC <= (others => '0'); 00330 reg_rMult2C <= (others => '0'); 00331 reg_rMult1C <= (others => '0'); 00332 reg_rMult3pA <= (others => '0'); 00333 reg_rMult2A <= (others => '0'); 00334 reg_rMult1A <= (others => '0'); 00335 reg_rWide <= (others => '0'); 00336 reg_rCtoA <= (others => '0'); 00337 reg_rAtoC <= (others => '0'); 00338 elsif ROD_CLK'event and ROD_CLK = '1' then 00339 if en_wr = '1' then 00340 reg_coarse <= COARSE_DELAY1 & COARSE_DELAY2 & COARSE_DELAY3 & COARSE_DELAY4 & 00341 COARSE_DELAY5 & COARSE_DELAY6 & COARSE_DELAY7 & COARSE_DELAY8; 00342 reg_fine <= FINE_DELAY1 & FINE_DELAY2 & FINE_DELAY3 & FINE_DELAY4 & 00343 FINE_DELAY5 & FINE_DELAY6 & FINE_DELAY7 & FINE_DELAY8; 00344 reg_datsrc <= DATA_SRC; 00345 reg_busy <= BUSY; 00346 reg_busyext <= BUSY_EXT; 00347 reg_lfull <= SLINK_FULL; 00348 reg_ldown <= SLINK_DOWN; 00349 reg_trigdel <= TRIGGER_DELAY; 00350 reg_ext_evt_id <= EXT_EVENT_ID; 00351 reg_orbit <= ORBIT_ID; 00352 reg_inhdel <= INHIBIT_DELAY; 00353 reg_bcid <= BCID; 00354 reg_dtet <= DETECTOR_EVENT_TYPE; 00355 reg_srcid <= SOURCE_ID; 00356 reg_formatv <= FORMAT_V; 00357 reg_runno <= RUN_NUMBER; 00358 reg_tty <= TRIGGER_TYPE; 00359 reg_ctpout(8 downto 0) <= CTP_OUT; 00360 reg_ctpfrc(8 downto 0) <= CTP_FORCE; 00361 reg_ctpsel <= CTP_SEL; 00362 reg_ttysel <= TTY_SEL; 00363 reg_dsswsel <= DSSW_SEL; 00364 reg_dssasel <= DSSA_SEL; 00365 reg_cibisel <= CIBI_SEL; 00366 reg_cibbsel <= CIBB_SEL; 00367 reg_latcy <= LATENCY; 00368 reg_cut1 <= CUT_COIN_L; 00369 reg_cut2 <= CUT_COIN_H; 00370 reg_cut3 <= CUT_WIDE_L; 00371 reg_cut4 <= CUT_WIDE_H; 00372 reg_cut5 <= CUT_OUTA_L; 00373 reg_cut6 <= CUT_OUTA_H; 00374 reg_cut7 <= CUT_OUTC_L; 00375 reg_cut8 <= CUT_OUTC_H; 00376 reg_rAttC <= TRATE_AttC; 00377 reg_rAttA <= TRATE_AttA; 00378 reg_rMult3pC <= TRATE_Mult3pC; 00379 reg_rMult2C <= TRATE_Mult2C; 00380 reg_rMult1C <= TRATE_Mult1C; 00381 reg_rMult3pA <= TRATE_Mult3pA; 00382 reg_rMult2A <= TRATE_Mult2A; 00383 reg_rMult1A <= TRATE_Mult1A; 00384 reg_rWide <= TRATE_Wide; 00385 reg_rCtoA <= TRATE_CtoA; 00386 reg_rAtoC <= TRATE_AtoC; 00387 if INJ_PERM = '1' then 00388 reg_inj <= (others => '1'); 00389 else 00390 reg_inj <= (others => '0'); 00391 end if; 00392 if BEAM_PERM = '1' then 00393 reg_beam <= (others => '1'); 00394 else 00395 reg_beam <= (others => '0'); 00396 end if; 00397 if DSS_WARNING = '1' then 00398 reg_dssw <= (others => '1'); 00399 else 00400 reg_dssw <= (others => '0'); 00401 end if; 00402 if DSS_ABORT = '1' then 00403 reg_dssa <= (others => '1'); 00404 else 00405 reg_dssa <= (others => '0'); 00406 end if; 00407 if L1A = '1' then 00408 reg_l1a <= (others => '1'); 00409 else 00410 reg_l1a <= (others => '0'); 00411 end if; 00412 if L1A_FIFO_FULL = '1' then 00413 reg_l1a_full <= (others => '1'); 00414 else 00415 reg_l1a_full <= (others => '0'); 00416 end if; 00417 if L1A_FIFO_EMPTY = '1' then 00418 reg_l1a_empty <= (others => '1'); 00419 else 00420 reg_l1a_empty <= (others => '0'); 00421 end if; 00422 end if; 00423 end if; 00424 end process registers_40;

Member Data Documentation

chksum_cal ddr2_chksum_cal [Component Instantiation] |

ddr2_chksum_cal [Component] |

checksum calculation

Reimplemented in main_components.

Definition at line 148 of file tdaq_collector.vhd.

edge [Component] |

start_pulse edge [Component Instantiation] |

The documentation for this class was generated from the following file: