pmdelay.pmdelay_arc Architecture Reference

Variable Post-Mortem layoff - orbit delay. More...

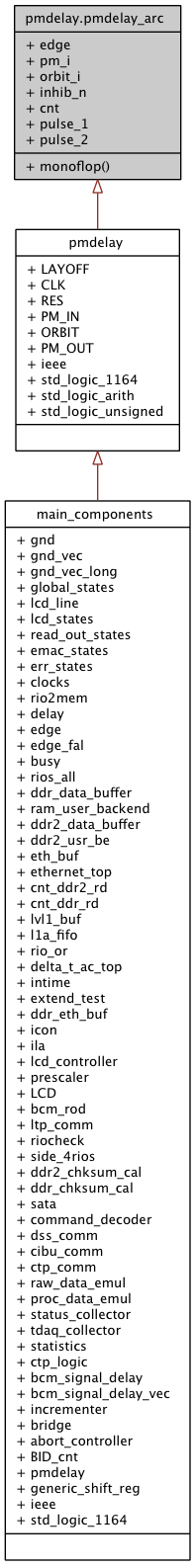

Inheritance diagram for pmdelay.pmdelay_arc:

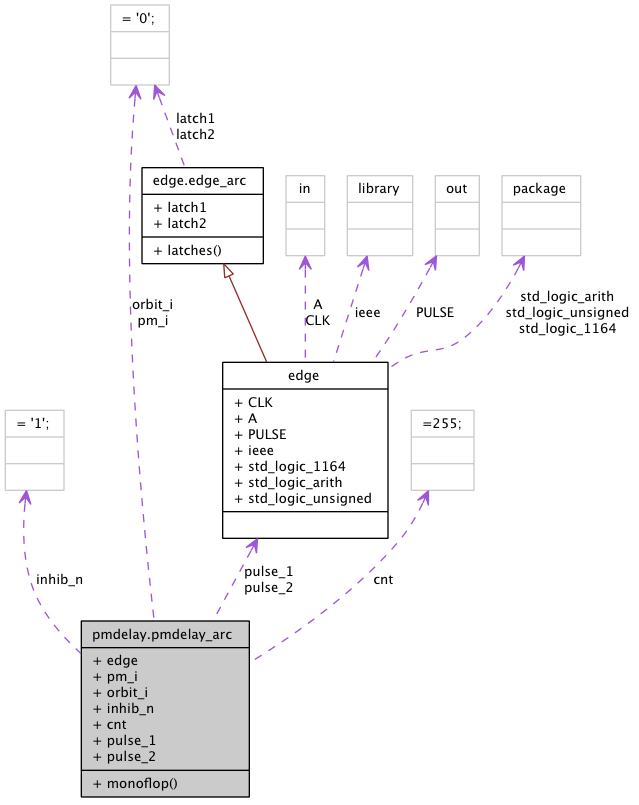

Collaboration diagram for pmdelay.pmdelay_arc:

Processes | |

| monoflop | ( CLK , RES ) |

Components | |

| edge | <Entity edge> |

| edge detection | |

Signals | |

| pm_i | std_logic := ' 0 ' |

| orbit_i | std_logic := ' 0 ' |

| inhib_n | std_logic := ' 1 ' |

| cnt | integer range 0 to 255 := 255 |

Component Instantiations | |

| pulse_1 | edge <Entity edge> |

| sync input | |

| pulse_2 | edge <Entity edge> |

| sync input | |

Detailed Description

Variable Post-Mortem layoff - orbit delay.While a Post Mortem is pending, all further input pulses are ignored. Inputs are synchronized internally with respect to the clock. The layoff is implemented similar to a monoflop. A rising edge on the PM_IN port triggers a counter, when it reaches the LAYOFF value, an pulse on the PM_OUT port is generated.

Definition at line 59 of file pmdelay.vhd.

Member Function Documentation

| monoflop | ( CLK , | |

| RES ) |

purpose: monoflop to layoff post mortem input type : sequential inputs : CLK, RES, orbit_i, pm_i outputs: PM_OUT

Definition at line 97 of file pmdelay.vhd.

00097 monoflop : process (CLK, RES) 00098 begin -- process monoflop 00099 if RES = '1' then -- asynchronous reset (active high) 00100 PM_OUT <= '0'; 00101 inhib_n <= '1'; 00102 cnt <= 255; 00103 elsif CLK'event and CLK = '1' then -- rising clock edge 00104 00105 if (pm_i and inhib_n) = '1' then 00106 cnt <= 0; 00107 inhib_n <= '0'; 00108 end if; 00109 00110 if (inhib_n = '0') and (orbit_i = '1') then 00111 cnt <= cnt + 1; 00112 end if; 00113 00114 if cnt = LAYOFF then 00115 PM_OUT <= '1'; 00116 inhib_n <= '1'; 00117 cnt <= 255; 00118 else 00119 PM_OUT <= '0'; 00120 end if; 00121 00122 end if; 00123 end process monoflop;

Member Data Documentation

edge [Component] |

The documentation for this class was generated from the following file: