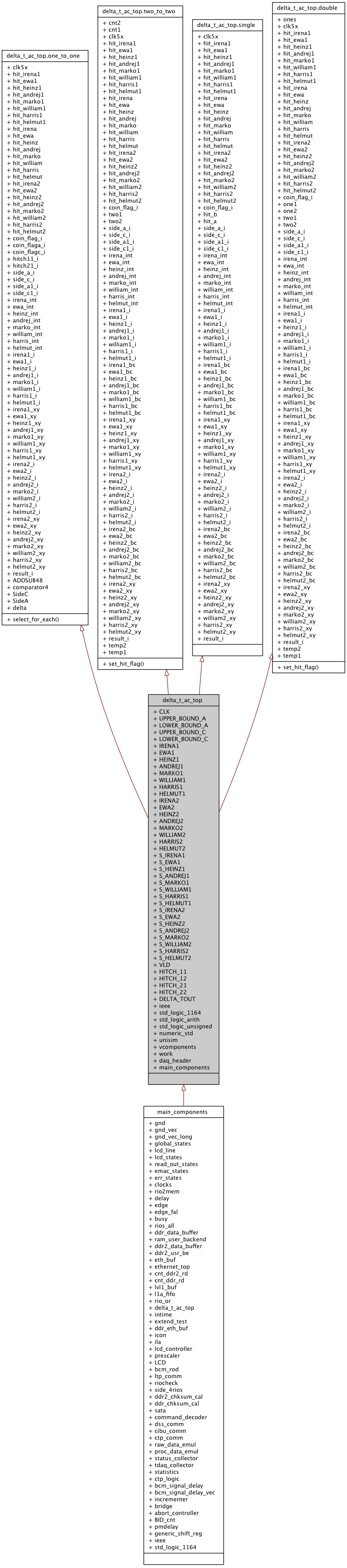

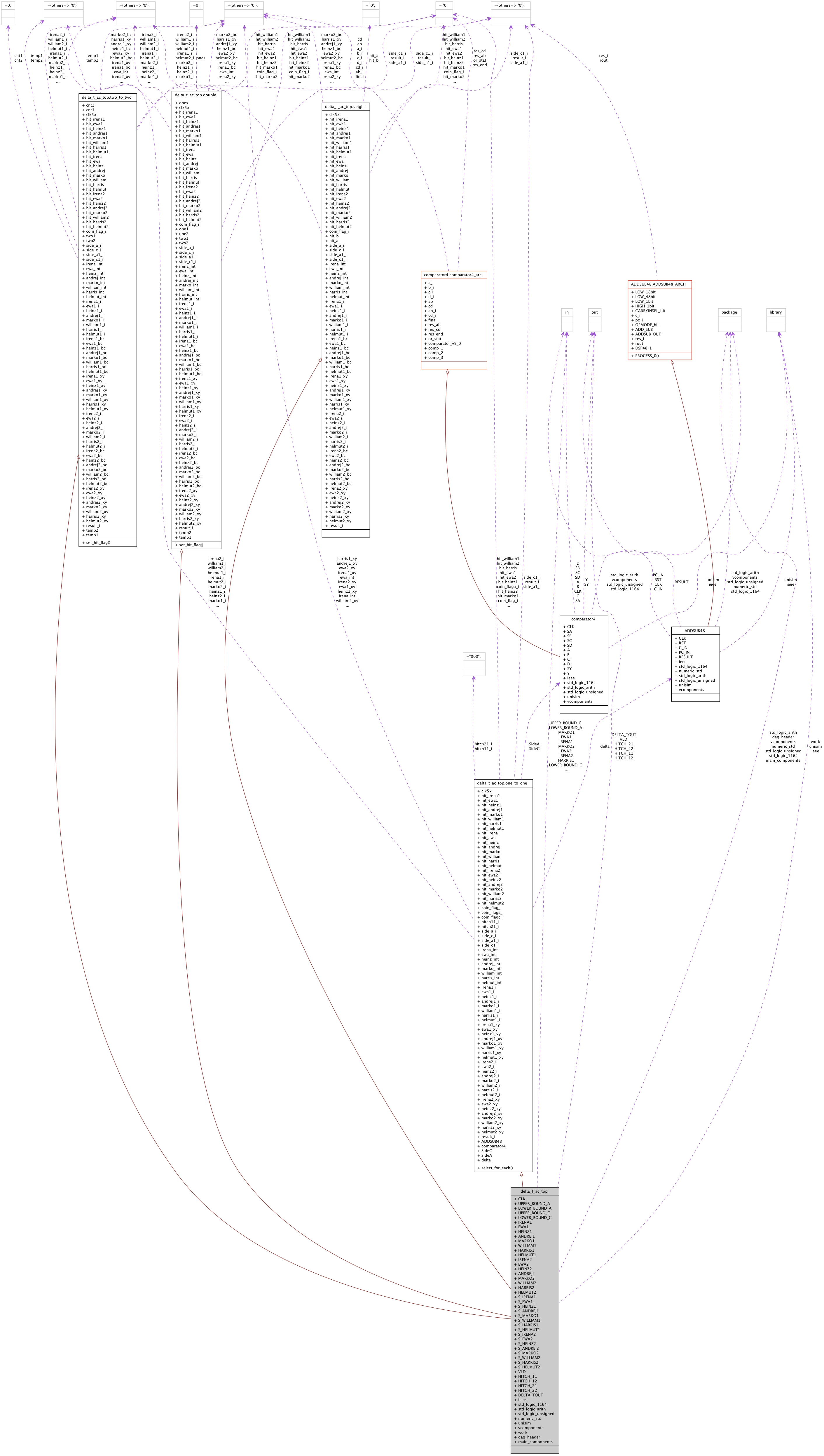

delta_t_ac_top Entity Reference

Top module of time window & coincidence logic. More...

Architectures | |

| double | Architecture |

| Register 2 hits within time window. More... | |

| one_to_one | Architecture |

| 1-1 Coincidence within time window More... | |

| single | Architecture |

| Register hit within time window. More... | |

| two_to_two | Architecture |

| 2-2 Coincidence within time window More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| unisim | |

| Library with Xilinx primitives. | |

| work | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

| numeric_std | |

| arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file | |

| vcomponents | |

| Header with Xilinx primitives. | |

| daq_header | Package <daq_header> |

| main_components | Package <main_components> |

Ports | |

| CLK | in std_logic |

| Clock. | |

| UPPER_BOUND_A | in std_logic_vector ( 5 downto 0 ) := " 101110 " |

| Time window upper boundary side A. | |

| LOWER_BOUND_A | in std_logic_vector ( 5 downto 0 ) := " 010000 " |

| Time window lower boundary side A. | |

| UPPER_BOUND_C | in std_logic_vector ( 5 downto 0 ) := " 101110 " |

| Time window upper boundary side C. | |

| LOWER_BOUND_C | in std_logic_vector ( 5 downto 0 ) := " 010000 " |

| Time window lower boundary side C. | |

| IRENA1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| EWA1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| HEINZ1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| ANDREJ1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| MARKO1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| WILLIAM1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| HARRIS1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| HELMUT1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| IRENA2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| EWA2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| HEINZ2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| ANDREJ2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| MARKO2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| WILLIAM2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| HARRIS2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| HELMUT2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| S_IRENA1 | in std_logic |

| 1 CH status bit | |

| S_EWA1 | in std_logic |

| 1 CH status bit | |

| S_HEINZ1 | in std_logic |

| 1 CH status bit | |

| S_ANDREJ1 | in std_logic |

| 1 CH status bit | |

| S_MARKO1 | in std_logic |

| 1 CH status bit | |

| S_WILLIAM1 | in std_logic |

| 1 CH status bit | |

| S_HARRIS1 | in std_logic |

| 1 CH status bit | |

| S_HELMUT1 | in std_logic |

| 1 CH status bit | |

| S_IRENA2 | in std_logic |

| 1 CH status bit | |

| S_EWA2 | in std_logic |

| 1 CH status bit | |

| S_HEINZ2 | in std_logic |

| 1 CH status bit | |

| S_ANDREJ2 | in std_logic |

| 1 CH status bit | |

| S_MARKO2 | in std_logic |

| 1 CH status bit | |

| S_WILLIAM2 | in std_logic |

| 1 CH status bit | |

| S_HARRIS2 | in std_logic |

| 1 CH status bit | |

| S_HELMUT2 | in std_logic |

| 1 CH status bit | |

| VLD | out std_logic |

| Coincidence flag. | |

| HITCH_11 | out std_logic_vector ( 2 downto 0 ) |

| Channel with hit (Side A). | |

| HITCH_12 | out std_logic_vector ( 2 downto 0 ) |

| Channel with hit (Side A). | |

| HITCH_21 | out std_logic_vector ( 2 downto 0 ) |

| Channel with hit (Side C). | |

| HITCH_22 | out std_logic_vector ( 2 downto 0 ) |

| Channel with hit (Side C). | |

| DELTA_TOUT | out std_logic_vector ( 6 downto 0 ) |

between sides between sides | |

Detailed Description

Top module of time window & coincidence logic.

This Entity is the top module of all the time window & coincidence logic. Takes up to three rising edge values per channel plus status bits for each. Time windows can be specified at runtime through ports. Can be set differently for each side of the IP. Returns a valid flag if a hit or coincidence is found (dependent on the respective architecture). The latency varies between the architectures, therefore a valid bit is set. If a coincidence between Side A & Side C is searched for the  between the hits is calculated and returned as an absolute value.

between the hits is calculated and returned as an absolute value.

Definition at line 52 of file delta_t_ac_top.vhd.

Member Data Documentation

ANDREJ1 in std_logic_vector ( 7 downto 0 ) [Port] |

ANDREJ2 in std_logic_vector ( 7 downto 0 ) [Port] |

CLK in std_logic [Port] |

DELTA_TOUT out std_logic_vector ( 6 downto 0 ) [Port] |

EWA1 in std_logic_vector ( 7 downto 0 ) [Port] |

EWA2 in std_logic_vector ( 7 downto 0 ) [Port] |

HARRIS1 in std_logic_vector ( 7 downto 0 ) [Port] |

HARRIS2 in std_logic_vector ( 7 downto 0 ) [Port] |

HEINZ1 in std_logic_vector ( 7 downto 0 ) [Port] |

HEINZ2 in std_logic_vector ( 7 downto 0 ) [Port] |

HELMUT1 in std_logic_vector ( 7 downto 0 ) [Port] |

HELMUT2 in std_logic_vector ( 7 downto 0 ) [Port] |

HITCH_11 out std_logic_vector ( 2 downto 0 ) [Port] |

HITCH_12 out std_logic_vector ( 2 downto 0 ) [Port] |

HITCH_21 out std_logic_vector ( 2 downto 0 ) [Port] |

HITCH_22 out std_logic_vector ( 2 downto 0 ) [Port] |

ieee library [Library] |

standard IEEE library

Reimplemented in main_components.

Definition at line 25 of file delta_t_ac_top.vhd.

IRENA1 in std_logic_vector ( 7 downto 0 ) [Port] |

IRENA2 in std_logic_vector ( 7 downto 0 ) [Port] |

LOWER_BOUND_A in std_logic_vector ( 5 downto 0 ) := " 010000 " [Port] |

LOWER_BOUND_C in std_logic_vector ( 5 downto 0 ) := " 010000 " [Port] |

MARKO1 in std_logic_vector ( 7 downto 0 ) [Port] |

MARKO2 in std_logic_vector ( 7 downto 0 ) [Port] |

numeric_std package [Package] |

arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file

Definition at line 33 of file delta_t_ac_top.vhd.

S_ANDREJ1 in std_logic [Port] |

S_ANDREJ2 in std_logic [Port] |

S_EWA1 in std_logic [Port] |

S_EWA2 in std_logic [Port] |

S_HARRIS1 in std_logic [Port] |

S_HARRIS2 in std_logic [Port] |

S_HEINZ1 in std_logic [Port] |

S_HEINZ2 in std_logic [Port] |

S_HELMUT1 in std_logic [Port] |

S_HELMUT2 in std_logic [Port] |

S_IRENA1 in std_logic [Port] |

S_IRENA2 in std_logic [Port] |

S_MARKO1 in std_logic [Port] |

S_MARKO2 in std_logic [Port] |

S_WILLIAM1 in std_logic [Port] |

S_WILLIAM2 in std_logic [Port] |

std_logic_1164 package [Package] |

std_logic definitions, see file

Reimplemented in main_components.

Definition at line 27 of file delta_t_ac_top.vhd.

std_logic_arith package [Package] |

arithmetic operations on std_logic datatypes, see file

Definition at line 29 of file delta_t_ac_top.vhd.

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 31 of file delta_t_ac_top.vhd.

unisim library [Library] |

UPPER_BOUND_A in std_logic_vector ( 5 downto 0 ) := " 101110 " [Port] |

UPPER_BOUND_C in std_logic_vector ( 5 downto 0 ) := " 101110 " [Port] |

vcomponents package [Package] |

VLD out std_logic [Port] |

WILLIAM1 in std_logic_vector ( 7 downto 0 ) [Port] |

WILLIAM2 in std_logic_vector ( 7 downto 0 ) [Port] |

The documentation for this class was generated from the following file: