delta_t_ac_top.one_to_one Architecture Reference

1-1 Coincidence within time window More...

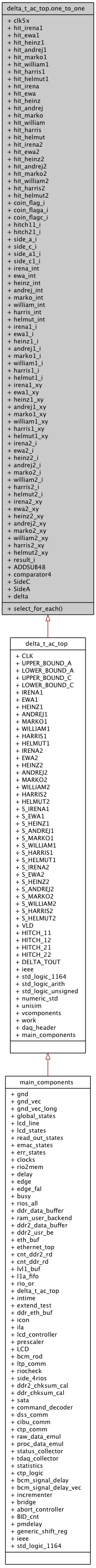

Inheritance diagram for delta_t_ac_top.one_to_one:

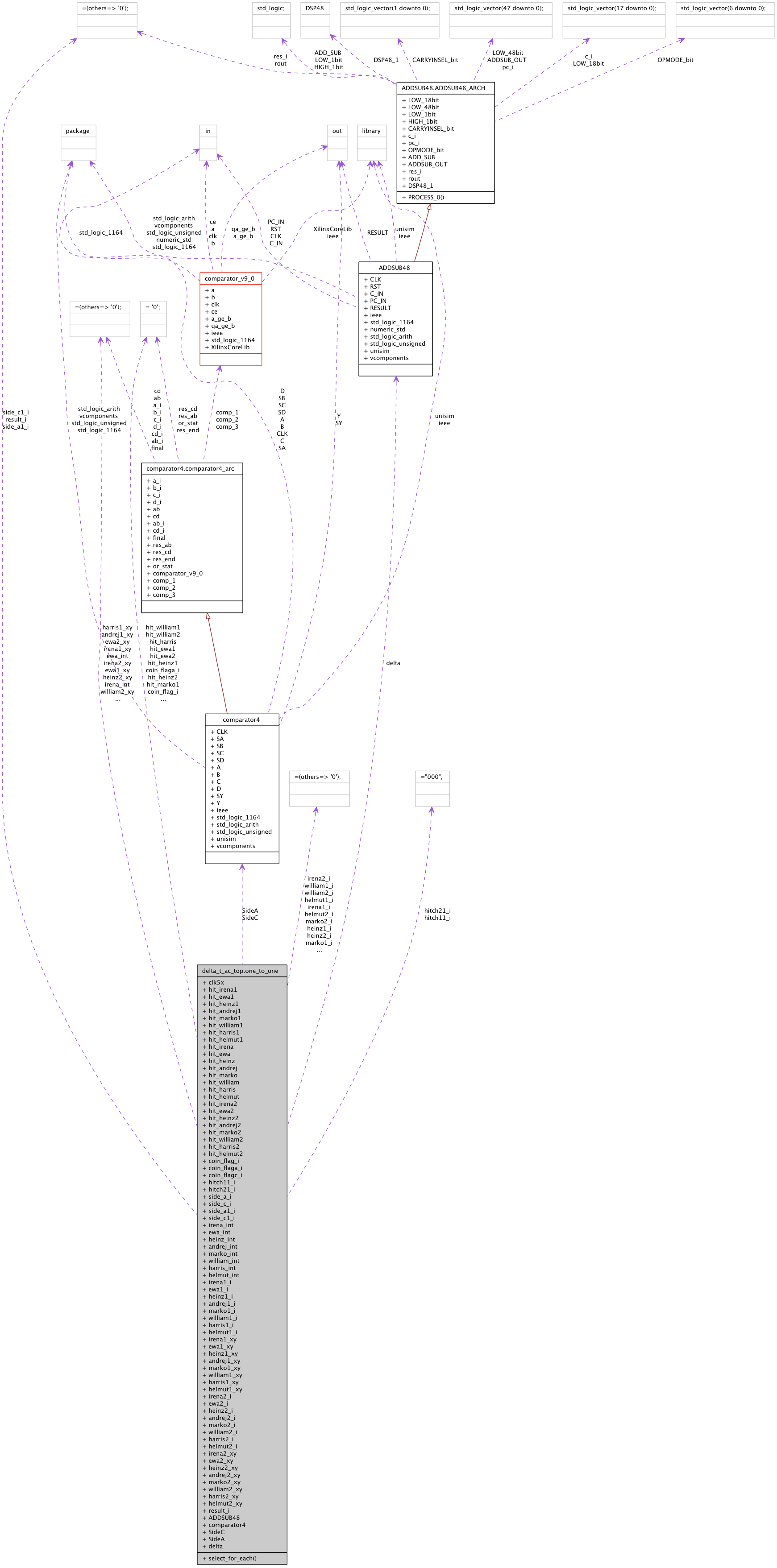

Collaboration diagram for delta_t_ac_top.one_to_one:

Processes | |

| select_for_each | ( clk5x ) |

| 2-to-1 decoder for each channel | |

Components | |

| ADDSUB48 | <Entity ADDSUB48> |

| Virtex-4 DSP Core. | |

| comparator4 | <Entity comparator4> |

| custom 4-input comparator core | |

Signals | |

| clk5x | std_logic := ' 0 ' |

| hit_irena1 | std_logic := ' 0 ' |

| hit_ewa1 | std_logic := ' 0 ' |

| hit_heinz1 | std_logic := ' 0 ' |

| hit_andrej1 | std_logic := ' 0 ' |

| hit_marko1 | std_logic := ' 0 ' |

| hit_william1 | std_logic := ' 0 ' |

| hit_harris1 | std_logic := ' 0 ' |

| hit_helmut1 | std_logic := ' 0 ' |

| hit_irena | std_logic := ' 0 ' |

| hit_ewa | std_logic := ' 0 ' |

| hit_heinz | std_logic := ' 0 ' |

| hit_andrej | std_logic := ' 0 ' |

| hit_marko | std_logic := ' 0 ' |

| hit_william | std_logic := ' 0 ' |

| hit_harris | std_logic := ' 0 ' |

| hit_helmut | std_logic := ' 0 ' |

| hit_irena2 | std_logic := ' 0 ' |

| hit_ewa2 | std_logic := ' 0 ' |

| hit_heinz2 | std_logic := ' 0 ' |

| hit_andrej2 | std_logic := ' 0 ' |

| hit_marko2 | std_logic := ' 0 ' |

| hit_william2 | std_logic := ' 0 ' |

| hit_harris2 | std_logic := ' 0 ' |

| hit_helmut2 | std_logic := ' 0 ' |

| coin_flag_i | std_logic := ' 0 ' |

| coin_flaga_i | std_logic := ' 0 ' |

| coin_flagc_i | std_logic := ' 0 ' |

| hitch11_i | std_logic_vector ( 2 downto 0 ) := " 000 " |

| hitch21_i | std_logic_vector ( 2 downto 0 ) := " 000 " |

| side_a_i | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| side_c_i | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| side_a1_i | std_logic_vector ( 6 downto 0 ) := ( others = > ' 0 ' ) |

| side_c1_i | std_logic_vector ( 6 downto 0 ) := ( others = > ' 0 ' ) |

| irena_int | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| ewa_int | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| heinz_int | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| andrej_int | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| marko_int | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| william_int | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| harris_int | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| helmut_int | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| irena1_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| ewa1_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| heinz1_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| andrej1_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| marko1_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| william1_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| harris1_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| helmut1_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| irena1_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| ewa1_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| heinz1_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| andrej1_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| marko1_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| william1_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| harris1_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| helmut1_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| irena2_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| ewa2_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| heinz2_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| andrej2_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| marko2_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| william2_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| harris2_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| helmut2_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| irena2_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| ewa2_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| heinz2_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| andrej2_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| marko2_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| william2_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| harris2_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| helmut2_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| result_i | std_logic_vector ( 6 downto 0 ) := ( others = > ' 0 ' ) |

Component Instantiations | |

| SideC | comparator4 <Entity comparator4> |

| SideA | comparator4 <Entity comparator4> |

| delta | ADDSUB48 <Entity ADDSUB48> |

Detailed Description

1-1 Coincidence within time windowThis architecture applies a time window to each data input and if a hit within this window is found the first one for each side is determined. If both sides signal a valid hit the output VLD is set high and the time difference between the two is calculated and returned as an absolute value. Currently needs 5 clock cycles for the whole computation

- Todo:

- run at higher clock speed

Definition at line 111 of file delta_t_ac_top.vhd.

Member Function Documentation

| select_for_each | ( clk5x ) |

2-to-1 decoder for each channel

Definition at line 227 of file delta_t_ac_top.vhd.

00227 select_for_each : process(clk5x) 00228 begin 00229 if clk5x'event and clk5x = '1' then 00230 00231 hit_irena <= '1'; 00232 if S_irena1 = '1' then 00233 irena_int <= irena1(5 downto 0); 00234 elsif S_irena2 = '1' then 00235 irena_int <= irena2(5 downto 0); 00236 else 00237 irena_int <= (others => '0'); 00238 hit_irena <= '0'; 00239 end if; 00240 00241 hit_ewa <= '1'; 00242 if S_ewa1 = '1' then 00243 ewa_int <= ewa1(5 downto 0); 00244 elsif S_ewa2 = '1' then 00245 ewa_int <= ewa2(5 downto 0); 00246 else 00247 ewa_int <= (others => '0'); 00248 hit_ewa <= '0'; 00249 end if; 00250 00251 hit_heinz <= '1'; 00252 if S_heinz1 = '1' then 00253 heinz_int <= heinz1(5 downto 0); 00254 elsif S_heinz2 = '1' then 00255 heinz_int <= heinz2(5 downto 0); 00256 else 00257 heinz_int <= (others => '0'); 00258 hit_heinz <= '0'; 00259 end if; 00260 00261 hit_andrej <= '1'; 00262 if S_andrej1 = '1' then 00263 andrej_int <= andrej1(5 downto 0); 00264 elsif S_andrej2 = '1' then 00265 andrej_int <= andrej2(5 downto 0); 00266 else 00267 andrej_int <= (others => '0'); 00268 hit_andrej <= '0'; 00269 end if; 00270 00271 hit_marko <= '1'; 00272 if S_marko1 = '1' then 00273 marko_int <= marko1(5 downto 0); 00274 elsif S_marko2 = '1' then 00275 marko_int <= marko2(5 downto 0); 00276 else 00277 marko_int <= (others => '0'); 00278 hit_marko <= '0'; 00279 end if; 00280 00281 hit_william <= '1'; 00282 if S_william1 = '1' then 00283 william_int <= william1(5 downto 0); 00284 elsif S_william2 = '1' then 00285 william_int <= william2(5 downto 0); 00286 else 00287 william_int <= (others => '0'); 00288 hit_william <= '0'; 00289 end if; 00290 00291 hit_harris <= '1'; 00292 if S_harris1 = '1' then 00293 harris_int <= harris1(5 downto 0); 00294 elsif S_harris2 = '1' then 00295 harris_int <= harris2(5 downto 0); 00296 else 00297 harris_int <= (others => '0'); 00298 hit_harris <= '0'; 00299 end if; 00300 00301 hit_helmut <= '1'; 00302 if S_helmut1 = '1' then 00303 helmut_int <= helmut1(5 downto 0); 00304 elsif S_helmut2 = '1' then 00305 helmut_int <= helmut2(5 downto 0); 00306 else 00307 helmut_int <= (others => '0'); 00308 hit_helmut <= '0'; 00309 end if; 00310 00311 end if; 00312 end process;

Member Data Documentation

ADDSUB48 [Component] |

comparator4 [Component] |

The documentation for this class was generated from the following file: