delta_t_ac_top.two_to_two Architecture Reference

2-2 Coincidence within time window More...

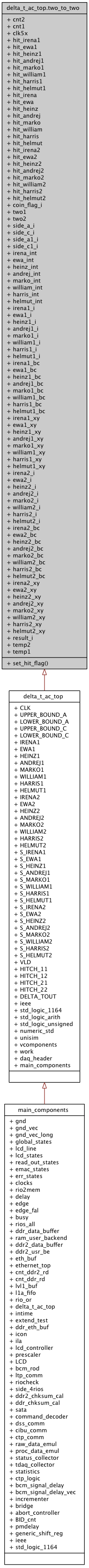

Inheritance diagram for delta_t_ac_top.two_to_two:

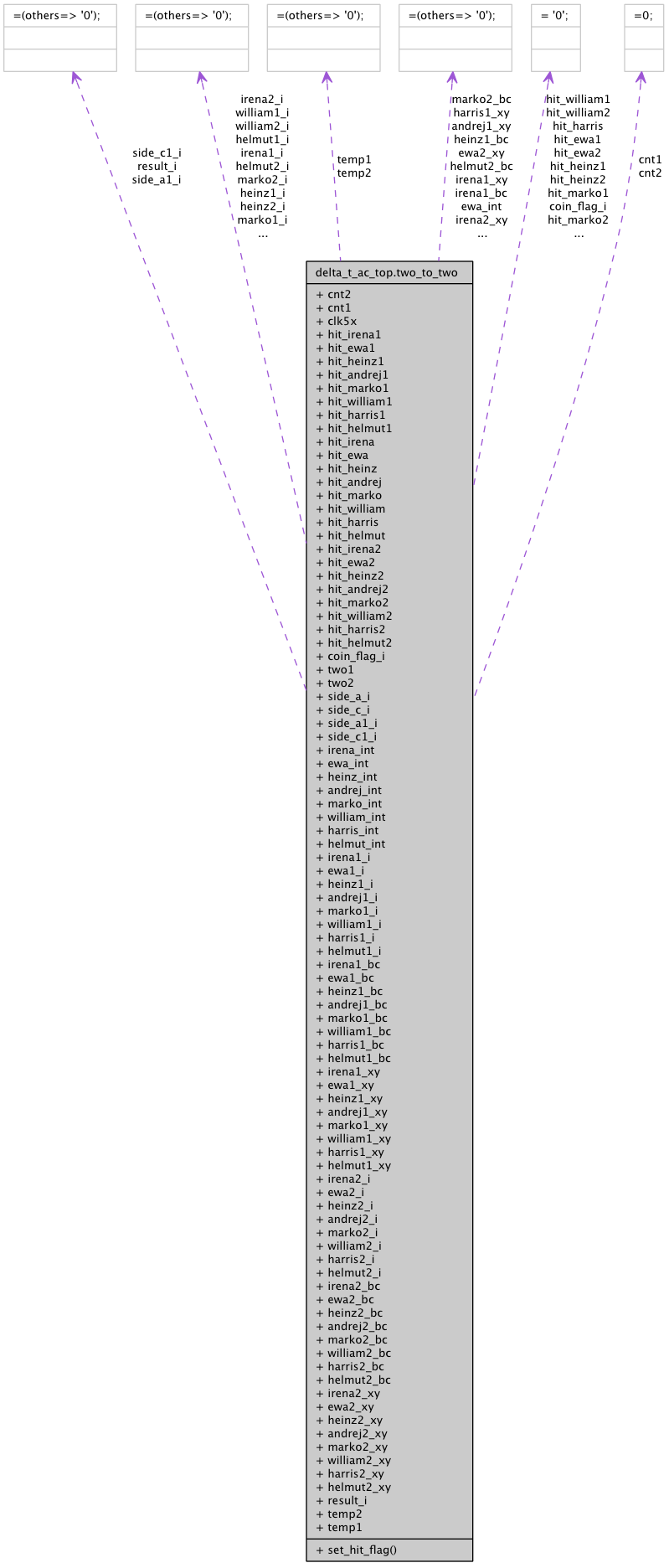

Collaboration diagram for delta_t_ac_top.two_to_two:

Processes | |

| set_hit_flag | ( clk5x ) |

Signals | |

| cnt2 | integer range 0 to 4 := 0 |

| cnt1 | integer range 0 to 4 := 0 |

| clk5x | std_logic := ' 0 ' |

| hit_irena1 | std_logic := ' 0 ' |

| hit_ewa1 | std_logic := ' 0 ' |

| hit_heinz1 | std_logic := ' 0 ' |

| hit_andrej1 | std_logic := ' 0 ' |

| hit_marko1 | std_logic := ' 0 ' |

| hit_william1 | std_logic := ' 0 ' |

| hit_harris1 | std_logic := ' 0 ' |

| hit_helmut1 | std_logic := ' 0 ' |

| hit_irena | std_logic := ' 0 ' |

| hit_ewa | std_logic := ' 0 ' |

| hit_heinz | std_logic := ' 0 ' |

| hit_andrej | std_logic := ' 0 ' |

| hit_marko | std_logic := ' 0 ' |

| hit_william | std_logic := ' 0 ' |

| hit_harris | std_logic := ' 0 ' |

| hit_helmut | std_logic := ' 0 ' |

| hit_irena2 | std_logic := ' 0 ' |

| hit_ewa2 | std_logic := ' 0 ' |

| hit_heinz2 | std_logic := ' 0 ' |

| hit_andrej2 | std_logic := ' 0 ' |

| hit_marko2 | std_logic := ' 0 ' |

| hit_william2 | std_logic := ' 0 ' |

| hit_harris2 | std_logic := ' 0 ' |

| hit_helmut2 | std_logic := ' 0 ' |

| coin_flag_i | std_logic := ' 0 ' |

| two1 | std_logic := ' 0 ' |

| two2 | std_logic := ' 0 ' |

| side_a_i | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| side_c_i | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| side_a1_i | std_logic_vector ( 6 downto 0 ) := ( others = > ' 0 ' ) |

| side_c1_i | std_logic_vector ( 6 downto 0 ) := ( others = > ' 0 ' ) |

| irena_int | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| ewa_int | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| heinz_int | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| andrej_int | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| marko_int | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| william_int | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| harris_int | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| helmut_int | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| irena1_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| ewa1_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| heinz1_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| andrej1_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| marko1_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| william1_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| harris1_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| helmut1_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| irena1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| ewa1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| heinz1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| andrej1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| marko1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| william1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| harris1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| helmut1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| irena1_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| ewa1_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| heinz1_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| andrej1_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| marko1_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| william1_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| harris1_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| helmut1_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| irena2_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| ewa2_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| heinz2_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| andrej2_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| marko2_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| william2_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| harris2_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| helmut2_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| irena2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| ewa2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| heinz2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| andrej2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| marko2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| william2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| harris2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| helmut2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| irena2_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| ewa2_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| heinz2_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| andrej2_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| marko2_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| william2_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| harris2_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| helmut2_xy | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| result_i | std_logic_vector ( 6 downto 0 ) := ( others = > ' 0 ' ) |

| temp2 | std_logic_vector ( 3 downto 0 ) := ( others = > ' 0 ' ) |

| temp1 | std_logic_vector ( 3 downto 0 ) := ( others = > ' 0 ' ) |

Detailed Description

2-2 Coincidence within time windowThis architecture applies a time window to each data input. If two hits within a time window are registered on each side of the IP, the VLD output flag is set to high. (Furthermore the time difference between the first hit on each side is returned as an absolute value.)

Definition at line 392 of file delta_t_ac_top.vhd.

The documentation for this class was generated from the following file: