ddr2_mem_rd_data_0.arc_rd_data Architecture Reference

Read datapath. More...

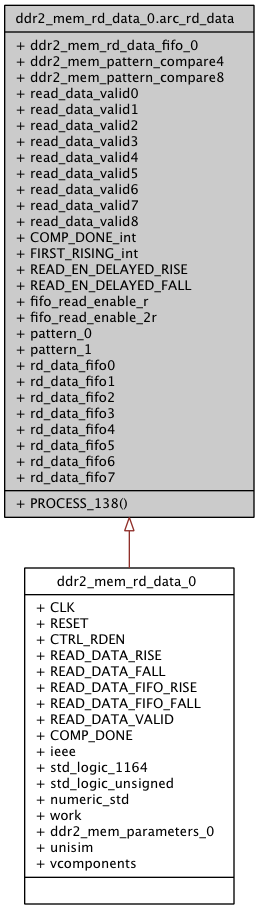

Inheritance diagram for ddr2_mem_rd_data_0.arc_rd_data:

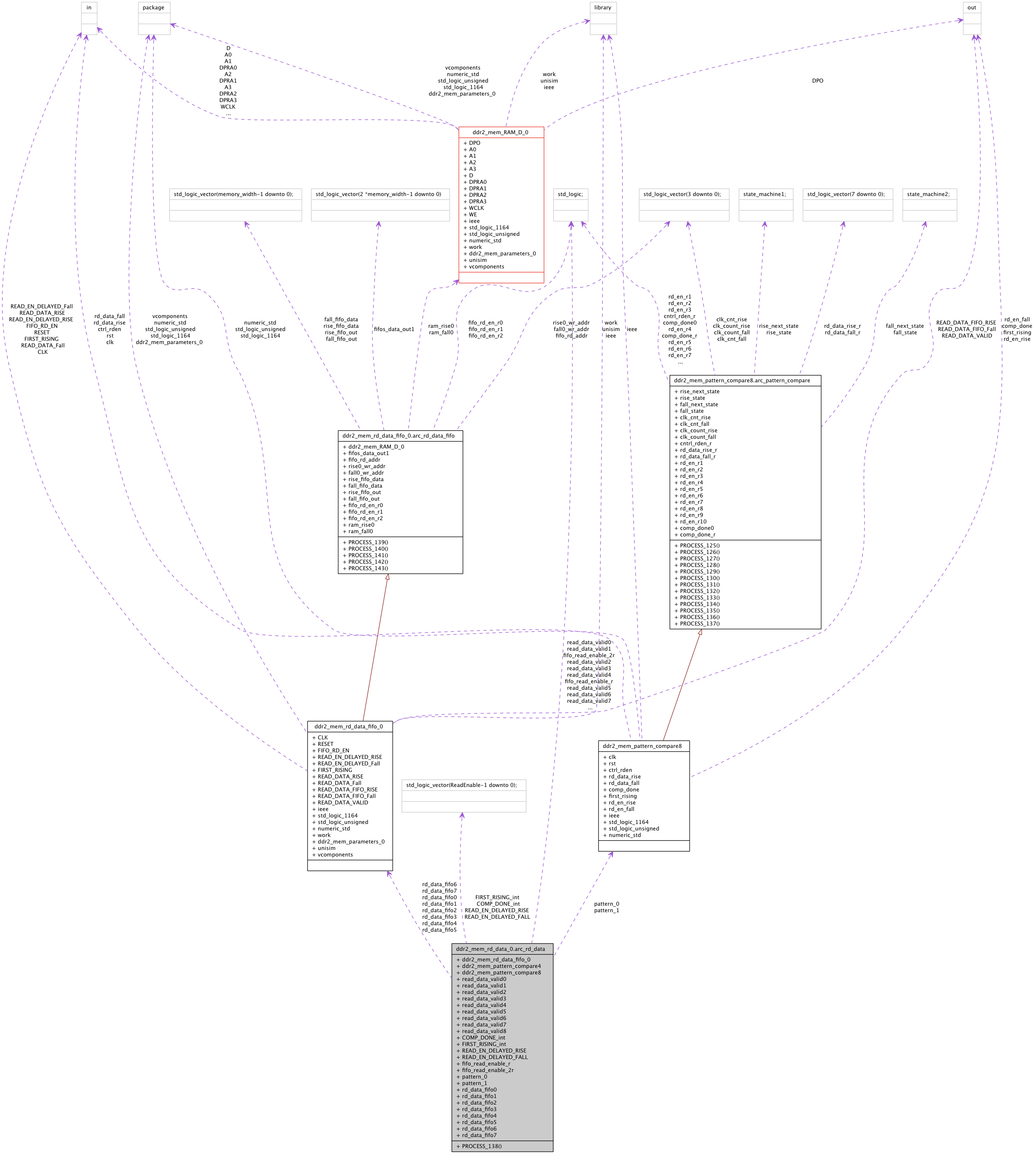

Collaboration diagram for ddr2_mem_rd_data_0.arc_rd_data:

Detailed Description

Read datapath.The delay between the read data with respect to the command issued is calculted in terms of no. of clocks. This data is then stored into the FIFOs and then read back and given as the ouput for comparison.

Definition at line 82 of file ddr2_mem_rd_data_0.vhd.

Member Function Documentation

| PROCESS_138 | ( CLK ) |

enable shift

Definition at line 151 of file ddr2_mem_rd_data_0.vhd.

00151 process(CLK) 00152 begin 00153 if (CLK'event and CLK = '1') then 00154 if (RESET = '1') then 00155 fifo_read_enable_r <= '0'; 00156 fifo_read_enable_2r <= '0'; 00157 else 00158 fifo_read_enable_r <= READ_EN_DELAYED_RISE(0); 00159 fifo_read_enable_2r <= fifo_read_enable_r; 00160 end if; 00161 end if; 00162 end process;

Member Data Documentation

ddr2_mem_pattern_compare4 [Component] |

ddr2_mem_pattern_compare8 [Component] |

ddr2_mem_rd_data_fifo_0 [Component] |

pattern_0 ddr2_mem_pattern_compare8 [Component Instantiation] |

pattern_1 ddr2_mem_pattern_compare8 [Component Instantiation] |

rd_data_fifo0 ddr2_mem_rd_data_fifo_0 [Component Instantiation] |

rd_data_fifo1 ddr2_mem_rd_data_fifo_0 [Component Instantiation] |

rd_data_fifo2 ddr2_mem_rd_data_fifo_0 [Component Instantiation] |

rd_data_fifo3 ddr2_mem_rd_data_fifo_0 [Component Instantiation] |

rd_data_fifo4 ddr2_mem_rd_data_fifo_0 [Component Instantiation] |

rd_data_fifo5 ddr2_mem_rd_data_fifo_0 [Component Instantiation] |

rd_data_fifo6 ddr2_mem_rd_data_fifo_0 [Component Instantiation] |

rd_data_fifo7 ddr2_mem_rd_data_fifo_0 [Component Instantiation] |

The documentation for this class was generated from the following file: