ddr2_mem.arc_ddr2_mem Architecture Reference

Structure of DDR2 Controller. More...

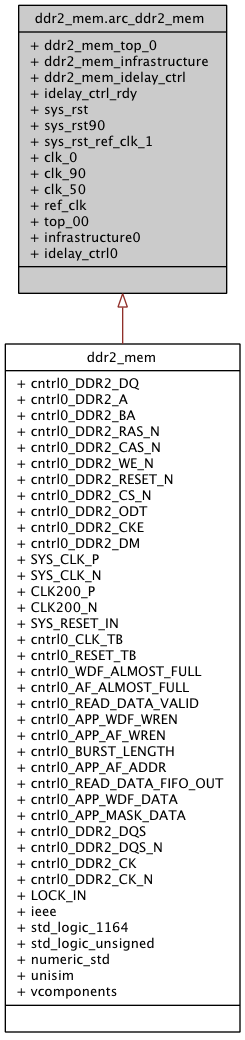

Inheritance diagram for ddr2_mem.arc_ddr2_mem:

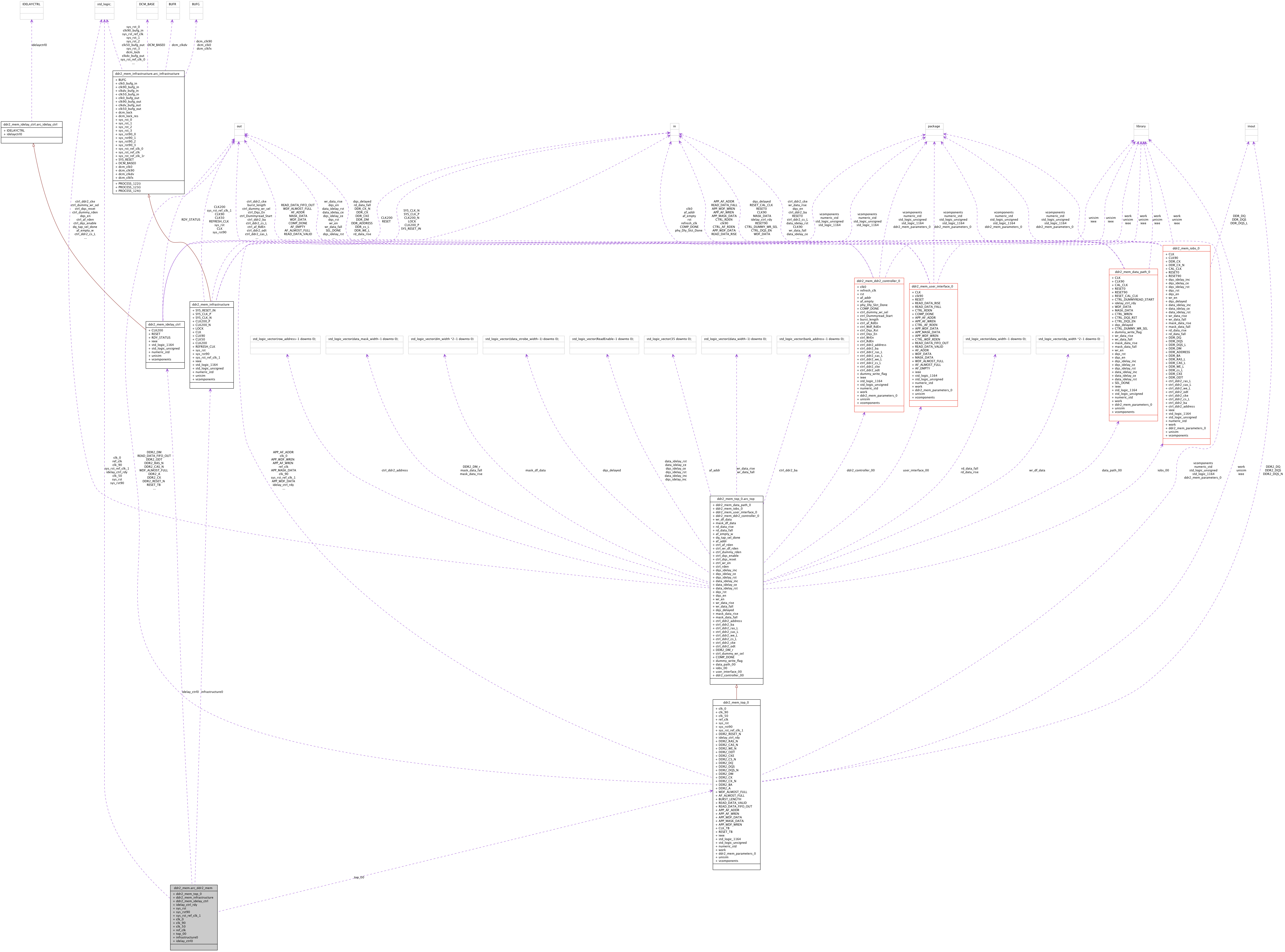

Collaboration diagram for ddr2_mem.arc_ddr2_mem:

Components | |

| ddr2_mem_top_0 | <Entity ddr2_mem_top_0> |

| main DDR2 module | |

| ddr2_mem_infrastructure | <Entity ddr2_mem_infrastructure> |

| Services for DDR2 controller. | |

| ddr2_mem_idelay_ctrl | <Entity ddr2_mem_idelay_ctrl> |

| iDelay modules | |

Signals | |

| idelay_ctrl_rdy | std_logic |

| sys_rst | std_logic |

| sys_rst90 | std_logic |

| sys_rst_ref_clk_1 | std_logic |

| clk_0 | std_logic |

| clk_90 | std_logic |

| clk_50 | std_logic |

| ref_clk | std_logic |

Component Instantiations | |

| top_00 | ddr2_mem_top_0 <Entity ddr2_mem_top_0> |

| main DDR2 controller module | |

| infrastructure0 | ddr2_mem_infrastructure <Entity ddr2_mem_infrastructure> |

| Services for DDR2 controller. | |

| idelay_ctrl0 | ddr2_mem_idelay_ctrl <Entity ddr2_mem_idelay_ctrl> |

| iDelayCtrl instantiation | |

Detailed Description

Structure of DDR2 Controller.It is the top most module which interfaces with the system and the memory.

Definition at line 100 of file ddr2_mem.vhd.

Member Data Documentation

ddr2_mem_idelay_ctrl [Component] |

ddr2_mem_infrastructure [Component] |

ddr2_mem_top_0 [Component] |

idelay_ctrl0 ddr2_mem_idelay_ctrl [Component Instantiation] |

infrastructure0 ddr2_mem_infrastructure [Component Instantiation] |

top_00 ddr2_mem_top_0 [Component Instantiation] |

The documentation for this class was generated from the following file: