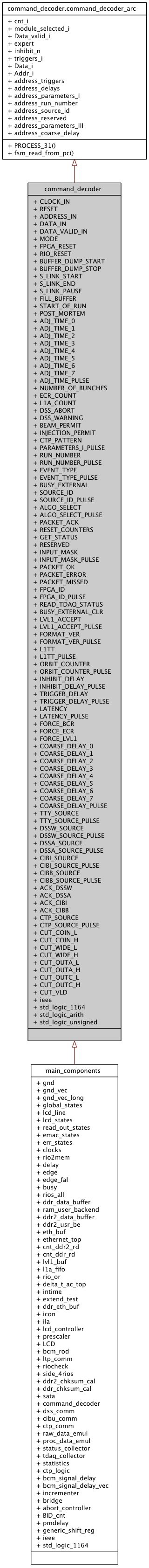

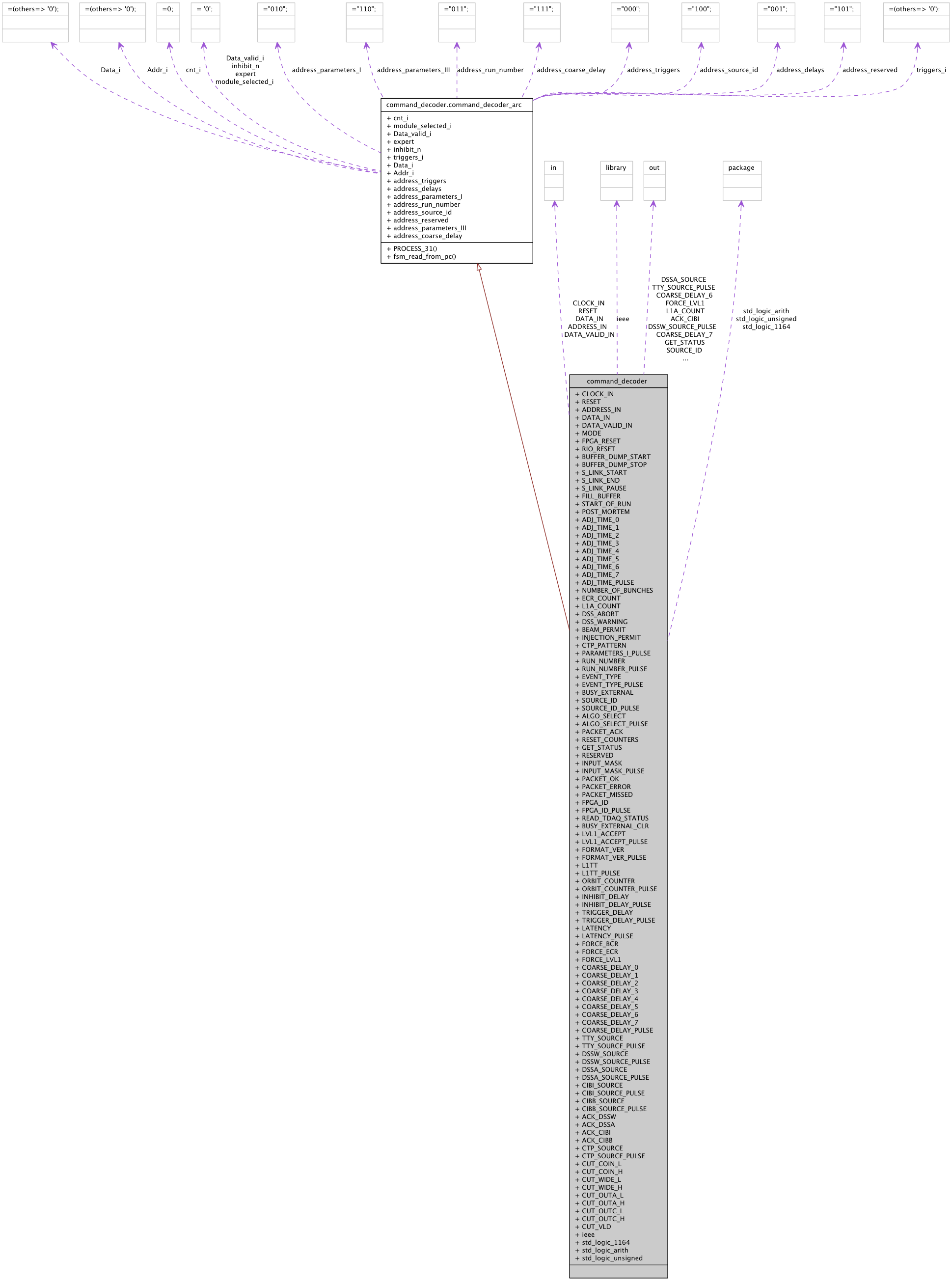

command_decoder Entity Reference

the pc-controlled module inside the FPGA More...

Architectures | |

| command_decoder_arc | Architecture |

| decoder for commands from PC More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

Ports | |

| CLOCK_IN | in std_logic |

| basic clock, the same as for the ethernet module | |

| RESET | in std_logic |

| Reset. | |

| ADDRESS_IN | in std_logic_vector ( 11 downto 0 ) |

| address lines | |

| DATA_IN | in std_logic_vector ( 7 downto 0 ) |

| input pc data | |

| DATA_VALID_IN | in std_logic |

| indicates valid data | |

| MODE | out std_logic |

| 1 = expert mode, 0 = regular | |

| FPGA_RESET | out std_logic |

| fpga reset | |

| RIO_RESET | out std_logic_vector ( 7 downto 0 ) |

| RocketIO resets. | |

| BUFFER_DUMP_START | out std_logic |

| buffer dump trigger | |

| BUFFER_DUMP_STOP | out std_logic |

| stopping the buffer dump | |

| S_LINK_START | out std_logic |

| starting the s-link | |

| S_LINK_END | out std_logic |

| end the s-link | |

| S_LINK_PAUSE | out std_logic |

| pause the s-link | |

| FILL_BUFFER | out std_logic |

| fill the buffer | |

| START_OF_RUN | out std_logic |

| start of the run | |

| POST_MORTEM | out std_logic |

| post mortem | |

| ADJ_TIME_0 | out integer range 0 to 64 |

| time delay | |

| ADJ_TIME_1 | out integer range 0 to 64 |

| time delay | |

| ADJ_TIME_2 | out integer range 0 to 64 |

| time delay | |

| ADJ_TIME_3 | out integer range 0 to 64 |

| time delay | |

| ADJ_TIME_4 | out integer range 0 to 64 |

| time delay | |

| ADJ_TIME_5 | out integer range 0 to 64 |

| time delay | |

| ADJ_TIME_6 | out integer range 0 to 64 |

| time delay | |

| ADJ_TIME_7 | out integer range 0 to 64 |

| time delay | |

| ADJ_TIME_PULSE | out std_logic_vector ( 7 downto 0 ) |

| pulse on x bit when time delay is set on ADJ_TIME_x | |

| NUMBER_OF_BUNCHES | out integer range 0 to 127 |

| bit 0 of PARAMETERS_I_PULSE | |

| ECR_COUNT | out std_logic_vector ( 7 downto 0 ) |

| bit 1 of PARAMETERS_I_PULSE | |

| L1A_COUNT | out std_logic_vector ( 23 downto 0 ) |

| bit 2 of PARAMETERS_I_PULSE | |

| DSS_ABORT | out std_logic |

| bit 3 of PARAMETERS_I_PULSE | |

| DSS_WARNING | out std_logic |

| bit 4 of PARAMETERS_I_PULSE | |

| BEAM_PERMIT | out std_logic |

| bit 5 of PARAMETERS_I_PULSE | |

| INJECTION_PERMIT | out std_logic |

| bit 6 of PARAMETERS_I_PULSE | |

| CTP_PATTERN | out std_logic_vector ( 9 downto 1 ) |

| bit 7 of PARAMETERS_I_PULSE | |

| PARAMETERS_I_PULSE | out std_logic_vector ( 7 downto 0 ) |

| enable for parameters | |

| RUN_NUMBER | out std_logic_vector ( 31 downto 0 ) |

| run number | |

| RUN_NUMBER_PULSE | out std_logic |

| enable pulse for run number | |

| EVENT_TYPE | out std_logic_vector ( 31 downto 0 ) |

| detector event type | |

| EVENT_TYPE_PULSE | out std_logic |

| enable pulse for detector event type | |

| BUSY_EXTERNAL | out std_logic |

| externally induced busy signal | |

| SOURCE_ID | out std_logic_vector ( 23 downto 0 ) |

| source ID | |

| SOURCE_ID_PULSE | out std_logic |

| enable pulse for source ID | |

| ALGO_SELECT | out std_logic_vector ( 7 downto 0 ) |

| selection of algorithms | |

| ALGO_SELECT_PULSE | out std_logic |

| enable pulse for algsorithm selection | |

| PACKET_ACK | out std_logic |

| simple ack. for packet | |

| RESET_COUNTERS | out std_logic |

| reset the counters | |

| GET_STATUS | out std_logic |

| get the status | |

| RESERVED | out std_logic_vector ( 7 downto 0 ) |

| reserved | |

| INPUT_MASK | out std_logic_vector ( 7 downto 0 ) |

| input mask | |

| INPUT_MASK_PULSE | out std_logic |

| enable pulse for input mask | |

| PACKET_OK | out std_logic |

| packed received ok | |

| PACKET_ERROR | out std_logic |

| packet received with error | |

| PACKET_MISSED | out std_logic |

| no packet received | |

| FPGA_ID | out std_logic_vector ( 7 downto 0 ) |

| FPGA ID. | |

| FPGA_ID_PULSE | out std_logic |

| enable pulse for FPGA ID | |

| READ_TDAQ_STATUS | out std_logic |

| polling of TDAQ status packet | |

| BUSY_EXTERNAL_CLR | out std_logic |

| signals that the busy should be cleared | |

| LVL1_ACCEPT | out std_logic_vector ( 5 downto 0 ) |

| LVL1 accept. | |

| LVL1_ACCEPT_PULSE | out std_logic |

| enable pulse for LVL1 | |

| FORMAT_VER | out std_logic_vector ( 31 downto 0 ) |

| format version | |

| FORMAT_VER_PULSE | out std_logic |

| enable pulse for format version | |

| L1TT | out std_logic_vector ( 7 downto 0 ) |

| level 1 trigger type | |

| L1TT_PULSE | out std_logic |

| enable pulse for L1TT | |

| ORBIT_COUNTER | out std_logic_vector ( 31 downto 0 ) |

| ORBIT counter. | |

| ORBIT_COUNTER_PULSE | out std_logic |

| enable pulse for ORBIT counter | |

| INHIBIT_DELAY | out std_logic_vector ( 7 downto 0 ) |

| inhibit delay | |

| INHIBIT_DELAY_PULSE | out std_logic |

| enable pulse for inhibit delay | |

| TRIGGER_DELAY | out std_logic_vector ( 7 downto 0 ) |

| trigger delay | |

| TRIGGER_DELAY_PULSE | out std_logic |

| enable pulse for trigger delay | |

| LATENCY | out std_logic_vector ( 7 downto 0 ) |

| read-out latency | |

| LATENCY_PULSE | out std_logic |

| enable pulse for read-out latency | |

| FORCE_BCR | out std_logic |

| BCR trigger. | |

| FORCE_ECR | out std_logic |

| ECR trigger. | |

| FORCE_LVL1 | out std_logic |

| LVL1 trigger. | |

| COARSE_DELAY_0 | out std_logic_vector ( 7 downto 0 ) |

| coarse delay | |

| COARSE_DELAY_1 | out std_logic_vector ( 7 downto 0 ) |

| coarse delay | |

| COARSE_DELAY_2 | out std_logic_vector ( 7 downto 0 ) |

| coarse delay | |

| COARSE_DELAY_3 | out std_logic_vector ( 7 downto 0 ) |

| coarse delay | |

| COARSE_DELAY_4 | out std_logic_vector ( 7 downto 0 ) |

| coarse delay | |

| COARSE_DELAY_5 | out std_logic_vector ( 7 downto 0 ) |

| coarse delay | |

| COARSE_DELAY_6 | out std_logic_vector ( 7 downto 0 ) |

| coarse delay | |

| COARSE_DELAY_7 | out std_logic_vector ( 7 downto 0 ) |

| coarse delay | |

| COARSE_DELAY_PULSE | out std_logic_vector ( 7 downto 0 ) |

| pulse on x bit when time delay is set on COARSE_DELAY_x | |

| TTY_SOURCE | out std_logic |

| source for TTY | |

| TTY_SOURCE_PULSE | out std_logic |

| source for TTY | |

| DSSW_SOURCE | out std_logic |

| source for Warning | |

| DSSW_SOURCE_PULSE | out std_logic |

| source for DSS Warning | |

| DSSA_SOURCE | out std_logic |

| source for Warning | |

| DSSA_SOURCE_PULSE | out std_logic |

| source for DSS Warning | |

| CIBI_SOURCE | out std_logic |

| source for CIBU Injection Permit | |

| CIBI_SOURCE_PULSE | out std_logic |

| source for CIBU Injection Permit | |

| CIBB_SOURCE | out std_logic |

| source for CIBU Beam Permit | |

| CIBB_SOURCE_PULSE | out std_logic |

| source for CIBU Beam Permit | |

| ACK_DSSW | out std_logic |

| acknowledge DSS Warning | |

| ACK_DSSA | out std_logic |

| acknowledge DSS Warning | |

| ACK_CIBI | out std_logic |

| acknowledge CIBU Injection Permit | |

| ACK_CIBB | out std_logic |

| acknowledge CIBU Beam Permit | |

| CTP_SOURCE | out std_logic |

| source for CTP | |

| CTP_SOURCE_PULSE | out std_logic |

| enable pulse for CTP_SOURCE | |

| CUT_COIN_L | out std_logic_vector ( 7 downto 0 ) |

| Time cut in-time coincidence. | |

| CUT_COIN_H | out std_logic_vector ( 7 downto 0 ) |

| Time cut in-time coincidence. | |

| CUT_WIDE_L | out std_logic_vector ( 7 downto 0 ) |

| Wide in-time time cut. | |

| CUT_WIDE_H | out std_logic_vector ( 7 downto 0 ) |

| Wide in-time time cut. | |

| CUT_OUTA_L | out std_logic_vector ( 7 downto 0 ) |

| Out-of-time cut side A. | |

| CUT_OUTA_H | out std_logic_vector ( 7 downto 0 ) |

| Out-of-time cut side A. | |

| CUT_OUTC_L | out std_logic_vector ( 7 downto 0 ) |

| Out-of-time cut side C. | |

| CUT_OUTC_H | out std_logic_vector ( 7 downto 0 ) |

| Out-of-time cut side A. | |

| CUT_VLD | out std_logic_vector ( 7 downto 0 ) |

| Enable for time cuts. | |

Detailed Description

the pc-controlled module inside the FPGA

This entity provides various triggers and settings through the ethernet connection

Further information about the protocol that is used can be found in the following document

Definition at line 37 of file command_decoder.vhd.

Member Data Documentation

ACK_CIBB out std_logic [Port] |

ACK_CIBI out std_logic [Port] |

ACK_DSSA out std_logic [Port] |

ACK_DSSW out std_logic [Port] |

ADDRESS_IN in std_logic_vector ( 11 downto 0 ) [Port] |

ADJ_TIME_0 out integer range 0 to 64 [Port] |

ADJ_TIME_1 out integer range 0 to 64 [Port] |

ADJ_TIME_2 out integer range 0 to 64 [Port] |

ADJ_TIME_3 out integer range 0 to 64 [Port] |

ADJ_TIME_4 out integer range 0 to 64 [Port] |

ADJ_TIME_5 out integer range 0 to 64 [Port] |

ADJ_TIME_6 out integer range 0 to 64 [Port] |

ADJ_TIME_7 out integer range 0 to 64 [Port] |

ADJ_TIME_PULSE out std_logic_vector ( 7 downto 0 ) [Port] |

pulse on x bit when time delay is set on ADJ_TIME_x

Definition at line 66 of file command_decoder.vhd.

ALGO_SELECT out std_logic_vector ( 7 downto 0 ) [Port] |

ALGO_SELECT_PULSE out std_logic [Port] |

BEAM_PERMIT out std_logic [Port] |

BUFFER_DUMP_START out std_logic [Port] |

BUFFER_DUMP_STOP out std_logic [Port] |

BUSY_EXTERNAL out std_logic [Port] |

BUSY_EXTERNAL_CLR out std_logic [Port] |

CIBB_SOURCE out std_logic [Port] |

CIBB_SOURCE_PULSE out std_logic [Port] |

CIBI_SOURCE out std_logic [Port] |

CIBI_SOURCE_PULSE out std_logic [Port] |

CLOCK_IN in std_logic [Port] |

COARSE_DELAY_0 out std_logic_vector ( 7 downto 0 ) [Port] |

COARSE_DELAY_1 out std_logic_vector ( 7 downto 0 ) [Port] |

COARSE_DELAY_2 out std_logic_vector ( 7 downto 0 ) [Port] |

COARSE_DELAY_3 out std_logic_vector ( 7 downto 0 ) [Port] |

COARSE_DELAY_4 out std_logic_vector ( 7 downto 0 ) [Port] |

COARSE_DELAY_5 out std_logic_vector ( 7 downto 0 ) [Port] |

COARSE_DELAY_6 out std_logic_vector ( 7 downto 0 ) [Port] |

COARSE_DELAY_7 out std_logic_vector ( 7 downto 0 ) [Port] |

COARSE_DELAY_PULSE out std_logic_vector ( 7 downto 0 ) [Port] |

pulse on x bit when time delay is set on COARSE_DELAY_x

Definition at line 123 of file command_decoder.vhd.

CTP_PATTERN out std_logic_vector ( 9 downto 1 ) [Port] |

CTP_SOURCE out std_logic [Port] |

CTP_SOURCE_PULSE out std_logic [Port] |

CUT_COIN_H out std_logic_vector ( 7 downto 0 ) [Port] |

CUT_COIN_L out std_logic_vector ( 7 downto 0 ) [Port] |

CUT_OUTA_H out std_logic_vector ( 7 downto 0 ) [Port] |

CUT_OUTA_L out std_logic_vector ( 7 downto 0 ) [Port] |

CUT_OUTC_H out std_logic_vector ( 7 downto 0 ) [Port] |

CUT_OUTC_L out std_logic_vector ( 7 downto 0 ) [Port] |

CUT_VLD out std_logic_vector ( 7 downto 0 ) [Port] |

CUT_WIDE_H out std_logic_vector ( 7 downto 0 ) [Port] |

CUT_WIDE_L out std_logic_vector ( 7 downto 0 ) [Port] |

DATA_IN in std_logic_vector ( 7 downto 0 ) [Port] |

DATA_VALID_IN in std_logic [Port] |

DSS_ABORT out std_logic [Port] |

DSS_WARNING out std_logic [Port] |

DSSA_SOURCE out std_logic [Port] |

DSSA_SOURCE_PULSE out std_logic [Port] |

DSSW_SOURCE out std_logic [Port] |

DSSW_SOURCE_PULSE out std_logic [Port] |

ECR_COUNT out std_logic_vector ( 7 downto 0 ) [Port] |

EVENT_TYPE out std_logic_vector ( 31 downto 0 ) [Port] |

EVENT_TYPE_PULSE out std_logic [Port] |

FILL_BUFFER out std_logic [Port] |

FORCE_BCR out std_logic [Port] |

FORCE_ECR out std_logic [Port] |

FORCE_LVL1 out std_logic [Port] |

FORMAT_VER out std_logic_vector ( 31 downto 0 ) [Port] |

FORMAT_VER_PULSE out std_logic [Port] |

FPGA_ID out std_logic_vector ( 7 downto 0 ) [Port] |

FPGA_ID_PULSE out std_logic [Port] |

FPGA_RESET out std_logic [Port] |

GET_STATUS out std_logic [Port] |

ieee library [Library] |

standard IEEE library

Reimplemented in main_components.

Definition at line 25 of file command_decoder.vhd.

INHIBIT_DELAY out std_logic_vector ( 7 downto 0 ) [Port] |

INHIBIT_DELAY_PULSE out std_logic [Port] |

INJECTION_PERMIT out std_logic [Port] |

INPUT_MASK out std_logic_vector ( 7 downto 0 ) [Port] |

INPUT_MASK_PULSE out std_logic [Port] |

L1A_COUNT out std_logic_vector ( 23 downto 0 ) [Port] |

L1TT out std_logic_vector ( 7 downto 0 ) [Port] |

L1TT_PULSE out std_logic [Port] |

LATENCY out std_logic_vector ( 7 downto 0 ) [Port] |

LATENCY_PULSE out std_logic [Port] |

LVL1_ACCEPT out std_logic_vector ( 5 downto 0 ) [Port] |

LVL1_ACCEPT_PULSE out std_logic [Port] |

MODE out std_logic [Port] |

NUMBER_OF_BUNCHES out integer range 0 to 127 [Port] |

ORBIT_COUNTER out std_logic_vector ( 31 downto 0 ) [Port] |

ORBIT_COUNTER_PULSE out std_logic [Port] |

PACKET_ACK out std_logic [Port] |

PACKET_ERROR out std_logic [Port] |

PACKET_MISSED out std_logic [Port] |

PACKET_OK out std_logic [Port] |

PARAMETERS_I_PULSE out std_logic_vector ( 7 downto 0 ) [Port] |

POST_MORTEM out std_logic [Port] |

READ_TDAQ_STATUS out std_logic [Port] |

RESERVED out std_logic_vector ( 7 downto 0 ) [Port] |

RESET in std_logic [Port] |

RESET_COUNTERS out std_logic [Port] |

RIO_RESET out std_logic_vector ( 7 downto 0 ) [Port] |

RUN_NUMBER out std_logic_vector ( 31 downto 0 ) [Port] |

RUN_NUMBER_PULSE out std_logic [Port] |

S_LINK_END out std_logic [Port] |

S_LINK_PAUSE out std_logic [Port] |

S_LINK_START out std_logic [Port] |

SOURCE_ID out std_logic_vector ( 23 downto 0 ) [Port] |

SOURCE_ID_PULSE out std_logic [Port] |

START_OF_RUN out std_logic [Port] |

std_logic_1164 package [Package] |

std_logic definitions, see file

Reimplemented in main_components.

Definition at line 27 of file command_decoder.vhd.

std_logic_arith package [Package] |

arithmetic operations on std_logic datatypes, see file

Definition at line 29 of file command_decoder.vhd.

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 31 of file command_decoder.vhd.

TRIGGER_DELAY out std_logic_vector ( 7 downto 0 ) [Port] |

TRIGGER_DELAY_PULSE out std_logic [Port] |

TTY_SOURCE out std_logic [Port] |

TTY_SOURCE_PULSE out std_logic [Port] |

The documentation for this class was generated from the following file: