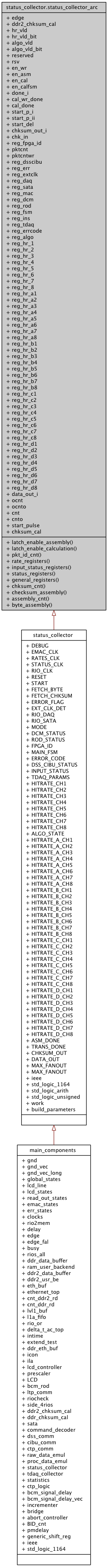

status_collector.status_collector_arc Architecture Reference

Data collector for status messages. More...

Processes | |

| latch_enable_assembly | ( EMAC_CLK , RESET ) |

| enable for general assembly | |

| latch_enable_calculation | ( EMAC_CLK , RESET ) |

| enable for chksum assembly FSM | |

| pkt_id_cnt | ( EMAC_CLK , RESET ) |

| Counter for packet ID. | |

| rate_registers | ( RATES_CLK , RESET ) |

| 40 MHz registers | |

| input_status_registers | ( RIO_CLK , RESET ) |

| 160 MHz registers | |

| status_registers | ( STATUS_CLK , RESET ) |

| 200 MHz registers | |

| general_registers | ( EMAC_CLK , RESET ) |

| 100 MHz registers | |

| chksum_cnt | ( EMAC_CLK , RESET ) |

| checksum_assembly | ( cnt ) |

| assembly_cnt | ( EMAC_CLK , RESET ) |

| byte_assembly | ( ocnt ) |

Components | |

| edge | <Entity edge> |

| edge detection | |

| ddr2_chksum_cal | <Entity ddr2_chksum_cal> |

| checksum calculation | |

Constants | |

| hr_vld | std_logic_vector ( 7 downto 0 ) := kSendHitRate |

| valid for hit rate field | |

| hr_vld_bit | std_logic := hr_vld ( 7 ) and hr_vld ( 6 ) and hr_vld ( 5 ) and hr_vld ( 4 ) and hr_vld ( 3 ) and hr_vld ( 2 ) and hr_vld ( 1 ) and hr_vld ( 0 ) |

| valid bit for hit rate field | |

| algo_vld | std_logic_vector ( 7 downto 0 ) := kSendAlgoRate |

| valid for algo rate field | |

| algo_vld_bit | std_logic := algo_vld ( 7 ) and algo_vld ( 6 ) and algo_vld ( 5 ) and algo_vld ( 4 ) and algo_vld ( 3 ) and algo_vld ( 2 ) and algo_vld ( 1 ) and algo_vld ( 0 ) |

| valid bit for algo rate field | |

| reserved | std_logic_vector ( 7 downto 0 ) := x " 00 " |

| reserved byte | |

Signals | |

| en_wr | std_logic := ' 0 ' |

| en_asm | std_logic := ' 0 ' |

| en_cal | std_logic := ' 0 ' |

| en_calfsm | std_logic := ' 0 ' |

| done_i | std_logic := ' 0 ' |

| cal_wr_done | std_logic := ' 0 ' |

| cal_done | std_logic := ' 0 ' |

| start_p_i | std_logic := ' 0 ' |

| start_p_ii | std_logic := ' 0 ' |

| start_del | std_logic := ' 0 ' |

| chksum_out_i | std_logic_vector ( 15 downto 0 ) := ( others = > ' 0 ' ) |

| chk_in | std_logic_vector ( 127 downto 0 ) := ( others = > ' 0 ' ) |

| reg_fpga_id | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| pktcnt | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| pktcntwr | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_dsscibu | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_err | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_extclk | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_daq | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_sata | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_mac | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_dcm | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_rod | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_fsm | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| reg_ins | std_logic_vector ( 63 downto 0 ) := ( others = > ' 0 ' ) |

| reg_tdaq | std_logic_vector ( 159 downto 0 ) := ( others = > ' 0 ' ) |

| reg_errcode | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_algo | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_1 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_2 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_3 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_4 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_5 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_6 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_7 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_8 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_a1 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_a2 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_a3 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_a4 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_a5 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_a6 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_a7 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_a8 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_b1 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_b2 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_b3 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_b4 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_b5 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_b6 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_b7 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_b8 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_c1 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_c2 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_c3 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_c4 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_c5 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_c6 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_c7 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_c8 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_d1 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_d2 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_d3 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_d4 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_d5 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_d6 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_d7 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| reg_hr_d8 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| data_out_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| ocnt | integer range 0 to 255 := 0 |

| ocnto | integer := 255 |

| cnt | integer range 0 to 31 := 0 |

| cnto | integer := 31 |

Component Instantiations | |

| start_pulse | edge <Entity edge> |

| make start pulse | |

| chksum_cal | ddr2_chksum_cal <Entity ddr2_chksum_cal> |

| checksum calculation | |

Aliases | |

| rsv | reserved |

Detailed Description

Data collector for status messages.This architecture collects all the data for the 1 Hz DCS status messages. It synchronizes all inputs from various clock domains to 100 MHz, puts them in the correct byte order & computes the UDP checksum. When everything is done an output flag is asserted.

Definition at line 125 of file status_collector.vhd.

Member Function Documentation

| general_registers | ( EMAC_CLK , | |

| RESET ) |

100 MHz registers

Definition at line 513 of file status_collector.vhd.

00513 general_registers : process (EMAC_CLK, RESET) 00514 begin -- process general_registers 00515 if RESET = '1' then -- asynchronous reset (active high) 00516 reg_mac <= (others => '0'); 00517 reg_fpga_id <= (others => '0'); 00518 elsif EMAC_CLK'event and EMAC_CLK = '1' then -- rising clock edge 00519 if en_wr = '1' then 00520 reg_fpga_id <= FPGA_ID; 00521 if MODE = '1' then 00522 reg_mac <= (others => '1'); 00523 else 00524 reg_mac <= (others => '0'); 00525 end if; 00526 end if; 00527 end if; 00528 end process general_registers;

| input_status_registers | ( RIO_CLK , | |

| RESET ) |

160 MHz registers

Definition at line 457 of file status_collector.vhd.

00457 input_status_registers : process (RIO_CLK, RESET) 00458 begin -- process input_status_registers 00459 if RESET = '1' then -- asynchronous reset (active high) 00460 reg_daq <= (others => '0'); 00461 reg_sata <= (others => '0'); 00462 reg_ins <= (others => '0'); 00463 elsif RIO_CLK'event and RIO_CLK = '1' then -- rising clock edge 00464 if en_wr = '1' then 00465 reg_ins <= INPUT_STATUS; 00466 if RIO_DAQ = '1' then 00467 reg_daq <= (others => '1'); 00468 else 00469 reg_daq <= (others => '0'); 00470 end if; 00471 if RIO_SATA = '1' then 00472 reg_sata <= (others => '1'); 00473 else 00474 reg_sata <= (others => '0'); 00475 end if; 00476 end if; 00477 end if; 00478 end process input_status_registers;

| latch_enable_assembly | ( EMAC_CLK , | |

| RESET ) |

enable for general assembly

Definition at line 265 of file status_collector.vhd.

00265 latch_enable_assembly : process (EMAC_CLK, RESET) 00266 begin -- process latch_enable_assembly 00267 if RESET = '1' then -- asynchronous reset (active high) 00268 en_asm <= '0'; 00269 elsif EMAC_CLK'event and EMAC_CLK = '1' then -- rising clock edge 00270 if done_i = '1' then 00271 en_asm <= '0'; 00272 elsif start_p_ii = '1' then 00273 en_asm <= '1'; 00274 end if; 00275 end if; 00276 end process latch_enable_assembly;

| latch_enable_calculation | ( EMAC_CLK , | |

| RESET ) |

enable for chksum assembly FSM

Definition at line 279 of file status_collector.vhd.

00279 latch_enable_calculation : process (EMAC_CLK, RESET) 00280 begin -- process latch_enable_assembly 00281 if RESET = '1' then -- asynchronous reset (active high) 00282 en_calfsm <= '0'; 00283 elsif EMAC_CLK'event and EMAC_CLK = '1' then -- rising clock edge 00284 if cal_wr_done = '1' then 00285 en_calfsm <= '0'; 00286 elsif start_p_i = '1' then 00287 en_calfsm <= '1'; 00288 end if; 00289 end if; 00290 end process latch_enable_calculation;

| pkt_id_cnt | ( EMAC_CLK , | |

| RESET ) |

Counter for packet ID.

Definition at line 295 of file status_collector.vhd.

00295 pkt_id_cnt : process (EMAC_CLK, RESET) 00296 begin -- process pkt_id_cnt 00297 if RESET = '1' then -- asynchronous reset (active high) 00298 pktcnt <= (others => '0'); 00299 pktcntwr <= (others => '0'); 00300 elsif EMAC_CLK'event and EMAC_CLK = '1' then -- rising clock edge 00301 if start_p_i = '1' then 00302 pktcntwr <= pktcnt; 00303 pktcnt <= pktcnt + 1; 00304 end if; 00305 end if; 00306 end process pkt_id_cnt;

| rate_registers | ( RATES_CLK , | |

| RESET ) |

40 MHz registers

Definition at line 309 of file status_collector.vhd.

00309 rate_registers : process (RATES_CLK, RESET) 00310 begin -- process registers 00311 if RESET = '1' then -- asynchronous reset (active high) 00312 reg_dsscibu <= (others => '0'); 00313 reg_rod <= (others => '0'); 00314 reg_tdaq <= (others => '0'); 00315 reg_algo <= (others => '0'); 00316 reg_hr_1 <= (others => '0'); 00317 reg_hr_2 <= (others => '0'); 00318 reg_hr_3 <= (others => '0'); 00319 reg_hr_4 <= (others => '0'); 00320 reg_hr_5 <= (others => '0'); 00321 reg_hr_6 <= (others => '0'); 00322 reg_hr_7 <= (others => '0'); 00323 reg_hr_8 <= (others => '0'); 00324 reg_hr_a1 <= (others => '0'); 00325 reg_hr_a2 <= (others => '0'); 00326 reg_hr_a3 <= (others => '0'); 00327 reg_hr_a4 <= (others => '0'); 00328 reg_hr_a5 <= (others => '0'); 00329 reg_hr_a6 <= (others => '0'); 00330 reg_hr_a7 <= (others => '0'); 00331 reg_hr_a8 <= (others => '0'); 00332 reg_hr_b1 <= (others => '0'); 00333 reg_hr_b2 <= (others => '0'); 00334 reg_hr_b3 <= (others => '0'); 00335 reg_hr_b4 <= (others => '0'); 00336 reg_hr_b5 <= (others => '0'); 00337 reg_hr_b6 <= (others => '0'); 00338 reg_hr_b7 <= (others => '0'); 00339 reg_hr_b8 <= (others => '0'); 00340 reg_hr_c1 <= (others => '0'); 00341 reg_hr_c2 <= (others => '0'); 00342 reg_hr_c3 <= (others => '0'); 00343 reg_hr_c4 <= (others => '0'); 00344 reg_hr_c5 <= (others => '0'); 00345 reg_hr_c6 <= (others => '0'); 00346 reg_hr_c7 <= (others => '0'); 00347 reg_hr_c8 <= (others => '0'); 00348 reg_hr_d1 <= (others => '0'); 00349 reg_hr_d2 <= (others => '0'); 00350 reg_hr_d3 <= (others => '0'); 00351 reg_hr_d4 <= (others => '0'); 00352 reg_hr_d5 <= (others => '0'); 00353 reg_hr_d6 <= (others => '0'); 00354 reg_hr_d7 <= (others => '0'); 00355 reg_hr_d8 <= (others => '0'); 00356 elsif RATES_CLK'event and RATES_CLK = '1' then -- rising clock edge 00357 if en_wr = '1' then 00358 if ROD_STATUS = '1' then 00359 reg_rod <= (others => '1'); 00360 else 00361 reg_rod <= (others => '0'); 00362 end if; 00363 reg_tdaq <= TDAQ_PARAMS; 00364 reg_dsscibu <= DSS_CIBU_STATUS; 00365 reg_algo <= ALGO_STATE; 00366 if hr_vld_bit = '1' then 00367 reg_hr_1 <= HITRATE_CH1; 00368 reg_hr_2 <= HITRATE_CH2; 00369 reg_hr_3 <= HITRATE_CH3; 00370 reg_hr_4 <= HITRATE_CH4; 00371 reg_hr_5 <= HITRATE_CH5; 00372 reg_hr_6 <= HITRATE_CH6; 00373 reg_hr_7 <= HITRATE_CH7; 00374 reg_hr_8 <= HITRATE_CH8; 00375 else 00376 reg_hr_1 <= (others => '0'); 00377 reg_hr_2 <= (others => '0'); 00378 reg_hr_3 <= (others => '0'); 00379 reg_hr_4 <= (others => '0'); 00380 reg_hr_5 <= (others => '0'); 00381 reg_hr_6 <= (others => '0'); 00382 reg_hr_7 <= (others => '0'); 00383 reg_hr_8 <= (others => '0'); 00384 end if; 00385 if algo_vld_bit = '1' then 00386 reg_hr_a1 <= HITRATE_A_CH1; 00387 reg_hr_a2 <= HITRATE_A_CH2; 00388 reg_hr_a3 <= HITRATE_A_CH3; 00389 reg_hr_a4 <= HITRATE_A_CH4; 00390 reg_hr_a5 <= HITRATE_A_CH5; 00391 reg_hr_a6 <= HITRATE_A_CH6; 00392 reg_hr_a7 <= HITRATE_A_CH7; 00393 reg_hr_a8 <= HITRATE_A_CH8; 00394 reg_hr_b1 <= HITRATE_B_CH1; 00395 reg_hr_b2 <= HITRATE_B_CH2; 00396 reg_hr_b3 <= HITRATE_B_CH3; 00397 reg_hr_b4 <= HITRATE_B_CH4; 00398 reg_hr_b5 <= HITRATE_B_CH5; 00399 reg_hr_b6 <= HITRATE_B_CH6; 00400 reg_hr_b7 <= HITRATE_B_CH7; 00401 reg_hr_b8 <= HITRATE_B_CH8; 00402 reg_hr_c1 <= HITRATE_C_CH1; 00403 reg_hr_c2 <= HITRATE_C_CH2; 00404 reg_hr_c3 <= HITRATE_C_CH3; 00405 reg_hr_c4 <= HITRATE_C_CH4; 00406 reg_hr_c5 <= HITRATE_C_CH5; 00407 reg_hr_c6 <= HITRATE_C_CH6; 00408 reg_hr_c7 <= HITRATE_C_CH7; 00409 reg_hr_c8 <= HITRATE_C_CH8; 00410 reg_hr_d1 <= HITRATE_D_CH1; 00411 reg_hr_d2 <= HITRATE_D_CH2; 00412 reg_hr_d3 <= HITRATE_D_CH3; 00413 reg_hr_d4 <= HITRATE_D_CH4; 00414 reg_hr_d5 <= HITRATE_D_CH5; 00415 reg_hr_d6 <= HITRATE_D_CH6; 00416 reg_hr_d7 <= HITRATE_D_CH7; 00417 reg_hr_d8 <= HITRATE_D_CH8; 00418 else 00419 reg_hr_a1 <= (others => '0'); 00420 reg_hr_a2 <= (others => '0'); 00421 reg_hr_a3 <= (others => '0'); 00422 reg_hr_a4 <= (others => '0'); 00423 reg_hr_a5 <= (others => '0'); 00424 reg_hr_a6 <= (others => '0'); 00425 reg_hr_a7 <= (others => '0'); 00426 reg_hr_a8 <= (others => '0'); 00427 reg_hr_b1 <= (others => '0'); 00428 reg_hr_b2 <= (others => '0'); 00429 reg_hr_b3 <= (others => '0'); 00430 reg_hr_b4 <= (others => '0'); 00431 reg_hr_b5 <= (others => '0'); 00432 reg_hr_b6 <= (others => '0'); 00433 reg_hr_b7 <= (others => '0'); 00434 reg_hr_b8 <= (others => '0'); 00435 reg_hr_c1 <= (others => '0'); 00436 reg_hr_c2 <= (others => '0'); 00437 reg_hr_c3 <= (others => '0'); 00438 reg_hr_c4 <= (others => '0'); 00439 reg_hr_c5 <= (others => '0'); 00440 reg_hr_c6 <= (others => '0'); 00441 reg_hr_c7 <= (others => '0'); 00442 reg_hr_c8 <= (others => '0'); 00443 reg_hr_d1 <= (others => '0'); 00444 reg_hr_d2 <= (others => '0'); 00445 reg_hr_d3 <= (others => '0'); 00446 reg_hr_d4 <= (others => '0'); 00447 reg_hr_d5 <= (others => '0'); 00448 reg_hr_d6 <= (others => '0'); 00449 reg_hr_d7 <= (others => '0'); 00450 reg_hr_d8 <= (others => '0'); 00451 end if; 00452 end if; 00453 end if; 00454 end process rate_registers;

| status_registers | ( STATUS_CLK , | |

| RESET ) |

200 MHz registers

Definition at line 481 of file status_collector.vhd.

00481 status_registers : process (STATUS_CLK, RESET) 00482 begin -- process status_registers 00483 if RESET = '1' then -- asynchronous reset (active high) 00484 reg_err <= (others => '0'); 00485 reg_errcode <= (others => '0'); 00486 reg_extclk <= (others => '0'); 00487 reg_dcm <= (others => '0'); 00488 reg_fsm <= (others => '0'); 00489 elsif STATUS_CLK'event and STATUS_CLK = '1' then -- rising clock edge 00490 if en_wr = '1' then 00491 if ERROR_FLAG = '1' then 00492 reg_err <= (others => '1'); 00493 else 00494 reg_err <= (others => '0'); 00495 end if; 00496 if EXT_CLK_DET = '1' then 00497 reg_extclk <= (others => '1'); 00498 else 00499 reg_extclk <= (others => '0'); 00500 end if; 00501 if DCM_STATUS = '1' then 00502 reg_dcm <= (others => '1'); 00503 else 00504 reg_dcm <= (others => '0'); 00505 end if; 00506 reg_fsm <= MAIN_FSM; 00507 reg_errcode <= ERROR_CODE; 00508 end if; 00509 end if; 00510 end process status_registers;

Member Data Documentation

algo_vld std_logic_vector ( 7 downto 0 ) := kSendAlgoRate [Constant] |

chksum_cal ddr2_chksum_cal [Component Instantiation] |

ddr2_chksum_cal [Component] |

checksum calculation

Reimplemented in main_components.

Definition at line 137 of file status_collector.vhd.

edge [Component] |

edge detection

Reimplemented in main_components.

Definition at line 128 of file status_collector.vhd.

hr_vld std_logic_vector ( 7 downto 0 ) := kSendHitRate [Constant] |

reserved std_logic_vector ( 7 downto 0 ) := x " 00 " [Constant] |

start_pulse edge [Component Instantiation] |

The documentation for this class was generated from the following file: