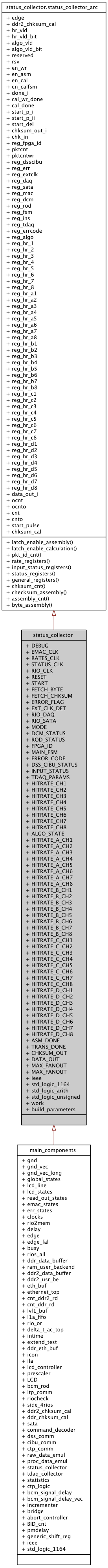

status_collector Entity Reference

Data collector for DCS status messages. More...

Architectures | |

| status_collector_arc | Architecture |

| Data collector for status messages. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| work | |

| Library with project specific headers. | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

| build_parameters | Package <build_parameters> |

| Header with config parameters for building the project. | |

Ports | |

| DEBUG | out std_logic_vector ( 14 downto 0 ) |

| EMAC_CLK | in std_logic |

| 100 MHz | |

| RATES_CLK | in std_logic |

| 40 MHz | |

| STATUS_CLK | in std_logic |

| 200 MHz | |

| RIO_CLK | in std_logic |

| 160 MHz | |

| RESET | in std_logic |

| Global Reset. | |

| START | in std_logic |

| Start assembling packet. | |

| FETCH_BYTE | in std_logic |

| Get data byte, hold high until TRANS_DONE = 1. | |

| FETCH_CHKSUM | in std_logic |

| Get checksum, set for 1 clk cycle. | |

| ERROR_FLAG | in std_logic |

| Error flag. | |

| EXT_CLK_DET | in std_logic |

| Extern clock status flag. | |

| RIO_DAQ | in std_logic |

| DAQ RocketIO status flag. | |

| RIO_SATA | in std_logic |

| SATA RocketIO status flag. | |

| MODE | in std_logic |

| Expert or normal mode. | |

| DCM_STATUS | in std_logic |

| DCM status flag. | |

| ROD_STATUS | in std_logic |

| ROD status flag. | |

| FPGA_ID | in std_logic_vector ( 7 downto 0 ) := x " 00 " |

| FPGA ID. | |

| MAIN_FSM | in std_logic_vector ( 7 downto 0 ) |

| State of main FSM. | |

| ERROR_CODE | in std_logic_vector ( 31 downto 0 ) |

| Error code. | |

| DSS_CIBU_STATUS | in std_logic_vector ( 31 downto 0 ) |

| Status of DSS & CIBU outputs. | |

| INPUT_STATUS | in std_logic_vector ( 63 downto 0 ) |

| Status of inputs, ie active or masked. | |

| TDAQ_PARAMS | in std_logic_vector ( 159 downto 0 ) := ( others = > ' 0 ' ) |

| All TDAQ Parameters. | |

| HITRATE_CH1 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch. | |

| HITRATE_CH2 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch. | |

| HITRATE_CH3 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch. | |

| HITRATE_CH4 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch. | |

| HITRATE_CH5 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch. | |

| HITRATE_CH6 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch. | |

| HITRATE_CH7 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch. | |

| HITRATE_CH8 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch. | |

| ALGO_STATE | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Algo State. | |

| HITRATE_A_CH1 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo A. | |

| HITRATE_A_CH2 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo A. | |

| HITRATE_A_CH3 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo A. | |

| HITRATE_A_CH4 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo A. | |

| HITRATE_A_CH5 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo A. | |

| HITRATE_A_CH6 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo A. | |

| HITRATE_A_CH7 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo A. | |

| HITRATE_A_CH8 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo A. | |

| HITRATE_B_CH1 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo B. | |

| HITRATE_B_CH2 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo B. | |

| HITRATE_B_CH3 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo B. | |

| HITRATE_B_CH4 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo B. | |

| HITRATE_B_CH5 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo B. | |

| HITRATE_B_CH6 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo B. | |

| HITRATE_B_CH7 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo B. | |

| HITRATE_B_CH8 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo B. | |

| HITRATE_C_CH1 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo C. | |

| HITRATE_C_CH2 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo C. | |

| HITRATE_C_CH3 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo C. | |

| HITRATE_C_CH4 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo C. | |

| HITRATE_C_CH5 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo C. | |

| HITRATE_C_CH6 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo C. | |

| HITRATE_C_CH7 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo C. | |

| HITRATE_C_CH8 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo C. | |

| HITRATE_D_CH1 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo D. | |

| HITRATE_D_CH2 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo D. | |

| HITRATE_D_CH3 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo D. | |

| HITRATE_D_CH4 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo D. | |

| HITRATE_D_CH5 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo D. | |

| HITRATE_D_CH6 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo D. | |

| HITRATE_D_CH7 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo D. | |

| HITRATE_D_CH8 | in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| Hit Rate 1 Ch Algo D. | |

| ASM_DONE | out std_logic |

| Packet assembly done, set FETCH_BYTE & FETCH_CHKSUM afterwards. | |

| TRANS_DONE | out std_logic |

| Transfer of full packet done. | |

| CHKSUM_OUT | out std_logic_vector ( 15 downto 0 ) |

| Checksum out to EMAC. | |

| DATA_OUT | out std_logic_vector ( 7 downto 0 ) |

| Data byte to EMAC. | |

Attributes | |

| MAX_FANOUT | string |

| MAX_FANOUT | " 10 " |

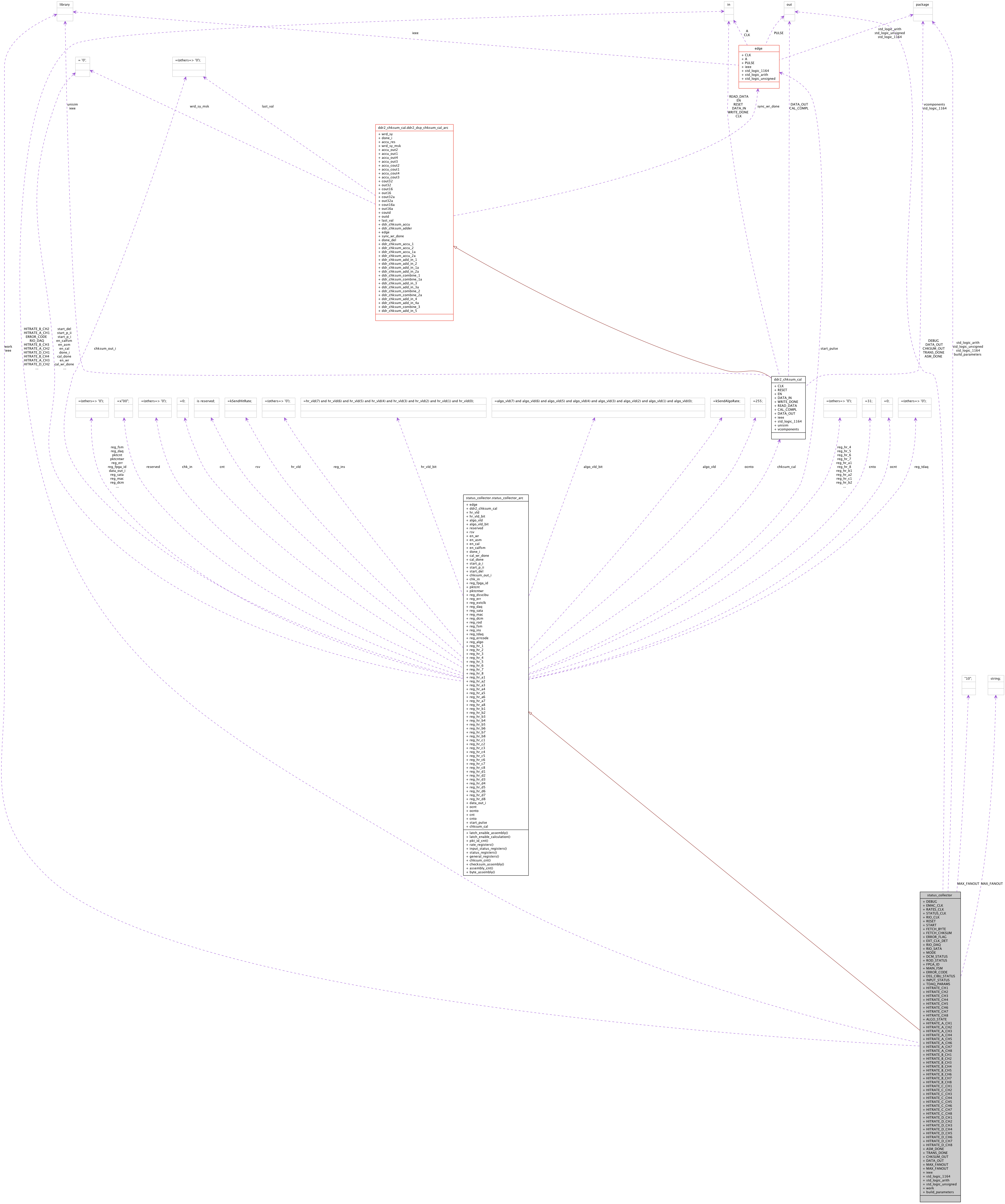

Detailed Description

Data collector for DCS status messages.

This entity collects all the data for the 1 Hz DCS status messages. It synchronizes all inputs from various clock domains to 100 MHz, puts them in the correct byte order & computes the UDP checksum. When everything is done an output flag is asserted.

The packet structure is outlined here

Definition at line 43 of file status_collector.vhd.

Member Data Documentation

ALGO_STATE in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

ASM_DONE out std_logic [Port] |

Packet assembly done, set FETCH_BYTE & FETCH_CHKSUM afterwards.

Definition at line 109 of file status_collector.vhd.

build_parameters package [Package] |

Header with config parameters for building the project.

Definition at line 35 of file status_collector.vhd.

CHKSUM_OUT out std_logic_vector ( 15 downto 0 ) [Port] |

DATA_OUT out std_logic_vector ( 7 downto 0 ) [Port] |

DCM_STATUS in std_logic [Port] |

DSS_CIBU_STATUS in std_logic_vector ( 31 downto 0 ) [Port] |

EMAC_CLK in std_logic [Port] |

ERROR_CODE in std_logic_vector ( 31 downto 0 ) [Port] |

ERROR_FLAG in std_logic [Port] |

EXT_CLK_DET in std_logic [Port] |

FETCH_BYTE in std_logic [Port] |

FETCH_CHKSUM in std_logic [Port] |

FPGA_ID in std_logic_vector ( 7 downto 0 ) := x " 00 " [Port] |

HITRATE_A_CH1 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_A_CH2 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_A_CH3 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_A_CH4 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_A_CH5 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_A_CH6 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_A_CH7 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_A_CH8 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_B_CH1 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_B_CH2 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_B_CH3 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_B_CH4 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_B_CH5 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_B_CH6 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_B_CH7 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_B_CH8 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_C_CH1 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_C_CH2 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_C_CH3 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_C_CH4 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_C_CH5 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_C_CH6 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_C_CH7 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_C_CH8 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_CH1 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_CH2 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_CH3 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_CH4 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_CH5 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_CH6 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_CH7 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_CH8 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_D_CH1 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_D_CH2 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_D_CH3 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_D_CH4 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_D_CH5 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_D_CH6 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_D_CH7 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

HITRATE_D_CH8 in std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Port] |

ieee library [Library] |

standard IEEE library

Reimplemented in main_components.

Definition at line 25 of file status_collector.vhd.

INPUT_STATUS in std_logic_vector ( 63 downto 0 ) [Port] |

MAIN_FSM in std_logic_vector ( 7 downto 0 ) [Port] |

MODE in std_logic [Port] |

RATES_CLK in std_logic [Port] |

RESET in std_logic [Port] |

RIO_CLK in std_logic [Port] |

RIO_DAQ in std_logic [Port] |

RIO_SATA in std_logic [Port] |

ROD_STATUS in std_logic [Port] |

START in std_logic [Port] |

STATUS_CLK in std_logic [Port] |

std_logic_1164 package [Package] |

std_logic definitions, see file

Reimplemented in main_components.

Definition at line 27 of file status_collector.vhd.

std_logic_arith package [Package] |

arithmetic operations on std_logic datatypes, see file

Definition at line 29 of file status_collector.vhd.

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 31 of file status_collector.vhd.

TDAQ_PARAMS in std_logic_vector ( 159 downto 0 ) := ( others = > ' 0 ' ) [Port] |

TRANS_DONE out std_logic [Port] |

work library [Library] |

The documentation for this class was generated from the following file: