side_4rios Entity Reference

Combination of 2 RocketIO-pairs. More...

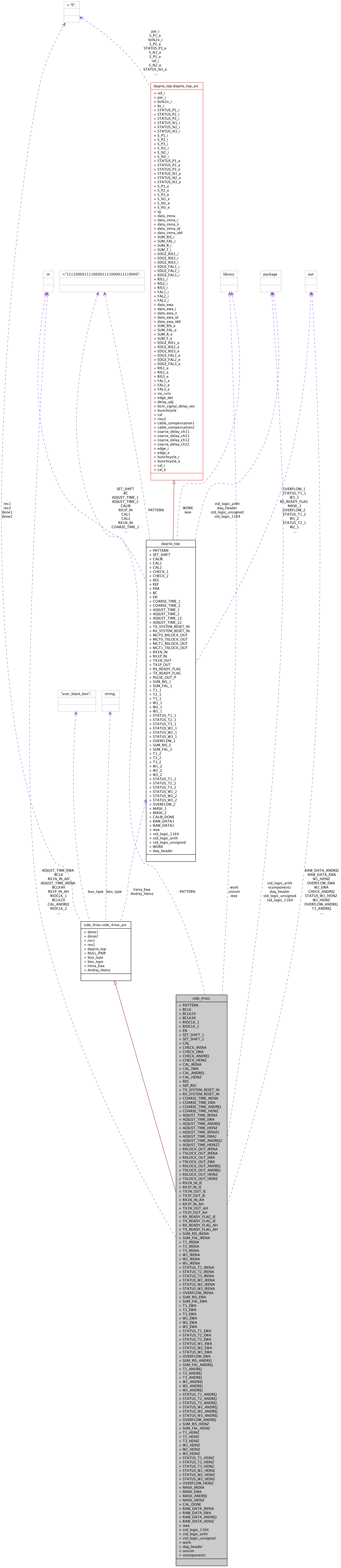

Inheritance diagram for side_4rios:

Collaboration diagram for side_4rios:

Architectures | |

| side_4rios_arc | Architecture |

| Combination of 2 RocketIO-pairs. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| work | |

| unisim | |

| Library with Xilinx primitives. | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

| daq_header | Package <daq_header> |

| vcomponents | |

| Header with Xilinx primitives. | |

Generics | |

| PATTERN | std_logic_vector ( 31 downto 0 ) := " 11110000111100001111000011110000 " |

| Pattern for external XOR. | |

Ports | |

| BCLK | in std_logic |

| Bunch Clock. | |

| BCLK2X | in std_logic |

| BC x2. | |

| BCLK4X | in std_logic |

| BC x4. | |

| RIOCLK_1 | in std_logic |

| BC x4 from RocketIO clock-module. | |

| RIOCLK_2 | in std_logic |

| BC x4 from RocketIO clock-module. | |

| EN | in std_logic |

| Enable to sync edge detection. | |

| SET_SHIFT_1 | in std_logic_vector ( 7 downto 0 ) |

| force calibration-pattern shift | |

| SET_SHIFT_2 | in std_logic_vector ( 7 downto 0 ) |

| force calibration-pattern shift | |

| CAL | in std_logic |

| enable calibration procedure, deassert once CAL_DONE = 1 | |

| CHECK_IRENA | out std_logic |

| Calibration check flag 1ch. | |

| CHECK_EWA | out std_logic |

| Calibration check flag 1ch. | |

| CHECK_ANDREJ | out std_logic |

| Calibration check flag 1ch. | |

| CHECK_HEINZ | out std_logic |

| Calibration check flag 1ch. | |

| CAL_IRENA | in std_logic |

| recalibrate 1 ch after trip | |

| CAL_EWA | in std_logic |

| recalibrate 1 ch after trip | |

| CAL_ANDREJ | in std_logic |

| recalibrate 1 ch after trip | |

| CAL_HEINZ | in std_logic |

| recalibrate 1 ch after trip | |

| RES | in std_logic |

| Reset. | |

| SEP_RES | in std_logic_vector ( 3 downto 0 ) |

| reset for seperate channels | |

| TX_SYSTEM_RESET_IN | in std_logic |

| tx reset | |

| RX_SYSTEM_RESET_IN | in std_logic |

| rx reset | |

| COARSE_TIME_IRENA | in std_logic_vector ( 7 downto 0 ) |

| coarse delay 1ch | |

| COARSE_TIME_EWA | in std_logic_vector ( 7 downto 0 ) |

| coarse delay 1ch | |

| COARSE_TIME_ANDREJ | in std_logic_vector ( 7 downto 0 ) |

| coarse delay 1ch | |

| COARSE_TIME_HEINZ | in std_logic_vector ( 7 downto 0 ) |

| coarse delay 1ch | |

| ADJUST_TIME_IRENA | in integer range 0 to 32 |

| fine delay 1ch | |

| ADJUST_TIME_EWA | in integer range 0 to 32 |

| fine delay 1ch | |

| ADJUST_TIME_ANDREJ | in integer range 0 to 32 |

| fine delay 1ch | |

| ADJUST_TIME_HEINZ | in integer range 0 to 32 |

| fine delay 1ch | |

| ADJUST_TIME_IRENA2 | in integer range 0 to 32 |

| fine delay 1ch | |

| ADJUST_TIME_EWA2 | in integer range 0 to 32 |

| fine delay 1ch | |

| ADJUST_TIME_ANDREJ2 | in integer range 0 to 32 |

| fine delay 1ch | |

| ADJUST_TIME_HEINZ2 | in integer range 0 to 32 |

| fine delay 1ch | |

| RXLOCK_OUT_IRENA | out std_logic |

| PLL lock flag. | |

| TXLOCK_OUT_IRENA | out std_logic |

| PLL lock flag. | |

| RXLOCK_OUT_EWA | out std_logic |

| PLL lock flag. | |

| TXLOCK_OUT_EWA | out std_logic |

| PLL lock flag. | |

| RXLOCK_OUT_ANDREJ | out std_logic |

| PLL lock flag. | |

| TXLOCK_OUT_ANDREJ | out std_logic |

| PLL lock flag. | |

| RXLOCK_OUT_HEINZ | out std_logic |

| PLL lock flag. | |

| TXLOCK_OUT_HEINZ | out std_logic |

| PLL lock flag. | |

| RX1N_IN_IE | in std_logic_vector ( 1 downto 0 ) |

| serial rx data in | |

| RX1P_IN_IE | in std_logic_vector ( 1 downto 0 ) |

| serial rx data in | |

| TX1N_OUT_IE | out std_logic_vector ( 1 downto 0 ) |

| serial tx data out | |

| TX1P_OUT_IE | out std_logic_vector ( 1 downto 0 ) |

| serial tx data out | |

| RX1N_IN_AH | in std_logic_vector ( 1 downto 0 ) |

| serial rx data in | |

| RX1P_IN_AH | in std_logic_vector ( 1 downto 0 ) |

| serial rx data in | |

| TX1N_OUT_AH | out std_logic_vector ( 1 downto 0 ) |

| serial tx data out | |

| TX1P_OUT_AH | out std_logic_vector ( 1 downto 0 ) |

| serial tx data out | |

| RX_READY_FLAG_IE | out std_logic |

| flag rx reset procedure finished | |

| TX_READY_FLAG_IE | out std_logic |

| flag tx reset procedure finished | |

| RX_READY_FLAG_AH | out std_logic |

| flag rx reset procedure finished | |

| TX_READY_FLAG_AH | out std_logic |

| flag tx reset procedure finished | |

| SUM_RIS_IRENA | out std_logic_vector ( 7 downto 0 ) |

| multiplicity 1ch | |

| SUM_FAL_IRENA | out std_logic_vector ( 7 downto 0 ) |

| multiplicity 1ch | |

| T1_IRENA | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| T2_IRENA | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| T3_IRENA | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| W1_IRENA | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| W2_IRENA | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| W3_IRENA | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| STATUS_T1_IRENA | out std_logic |

| proc status bit 1ch | |

| STATUS_T2_IRENA | out std_logic |

| proc status bit 1ch | |

| STATUS_T3_IRENA | out std_logic |

| proc status bit 1ch | |

| STATUS_W1_IRENA | out std_logic |

| proc status bit 1ch | |

| STATUS_W2_IRENA | out std_logic |

| proc status bit 1ch | |

| STATUS_W3_IRENA | out std_logic |

| proc status bit 1ch | |

| OVERFLOW_IRENA | out std_logic |

| proc status bit 1ch | |

| SUM_RIS_EWA | out std_logic_vector ( 7 downto 0 ) |

| multiplicity 1ch | |

| SUM_FAL_EWA | out std_logic_vector ( 7 downto 0 ) |

| multiplicity 1ch | |

| T1_EWA | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| T2_EWA | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| T3_EWA | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| W1_EWA | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| W2_EWA | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| W3_EWA | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| STATUS_T1_EWA | out std_logic |

| proc status bit 1ch | |

| STATUS_T2_EWA | out std_logic |

| proc status bit 1ch | |

| STATUS_T3_EWA | out std_logic |

| proc status bit 1ch | |

| STATUS_W1_EWA | out std_logic |

| proc status bit 1ch | |

| STATUS_W2_EWA | out std_logic |

| proc status bit 1ch | |

| STATUS_W3_EWA | out std_logic |

| proc status bit 1ch | |

| OVERFLOW_EWA | out std_logic |

| proc status bit 1ch | |

| SUM_RIS_ANDREJ | out std_logic_vector ( 7 downto 0 ) |

| multiplicity 1ch | |

| SUM_FAL_ANDREJ | out std_logic_vector ( 7 downto 0 ) |

| multiplicity 1ch | |

| T1_ANDREJ | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| T2_ANDREJ | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| T3_ANDREJ | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| W1_ANDREJ | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| W2_ANDREJ | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| W3_ANDREJ | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| STATUS_T1_ANDREJ | out std_logic |

| proc status bit 1ch | |

| STATUS_T2_ANDREJ | out std_logic |

| proc status bit 1ch | |

| STATUS_T3_ANDREJ | out std_logic |

| proc status bit 1ch | |

| STATUS_W1_ANDREJ | out std_logic |

| proc status bit 1ch | |

| STATUS_W2_ANDREJ | out std_logic |

| proc status bit 1ch | |

| STATUS_W3_ANDREJ | out std_logic |

| proc status bit 1ch | |

| OVERFLOW_ANDREJ | out std_logic |

| proc status bit 1ch | |

| SUM_RIS_HEINZ | out std_logic_vector ( 7 downto 0 ) |

| multiplicity 1ch | |

| SUM_FAL_HEINZ | out std_logic_vector ( 7 downto 0 ) |

| multiplicity 1ch | |

| T1_HEINZ | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| T2_HEINZ | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| T3_HEINZ | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| W1_HEINZ | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| W2_HEINZ | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| W3_HEINZ | out std_logic_vector ( 7 downto 0 ) |

| proc data 1ch | |

| STATUS_T1_HEINZ | out std_logic |

| proc status bit 1ch | |

| STATUS_T2_HEINZ | out std_logic |

| proc status bit 1ch | |

| STATUS_T3_HEINZ | out std_logic |

| proc status bit 1ch | |

| STATUS_W1_HEINZ | out std_logic |

| proc status bit 1ch | |

| STATUS_W2_HEINZ | out std_logic |

| proc status bit 1ch | |

| STATUS_W3_HEINZ | out std_logic |

| proc status bit 1ch | |

| OVERFLOW_HEINZ | out std_logic |

| proc status bit 1ch | |

| MASK_IRENA | out std_logic |

| data mask 1ch | |

| MASK_EWA | out std_logic |

| data mask 1ch | |

| MASK_ANDREJ | out std_logic |

| data mask 1ch | |

| MASK_HEINZ | out std_logic |

| data mask 1ch | |

| CAL_DONE | out std_logic |

| calibration done flag | |

| RAW_DATA_IRENA | out std_logic_vector ( 31 downto 0 ) |

| raw data 1ch | |

| RAW_DATA_EWA | out std_logic_vector ( 31 downto 0 ) |

| raw data 1ch | |

| RAW_DATA_ANDREJ | out std_logic_vector ( 31 downto 0 ) |

| raw data 1ch | |

| RAW_DATA_HEINZ | out std_logic_vector ( 31 downto 0 ) |

| raw data 1ch | |

Detailed Description

Combination of 2 RocketIO-pairs.Definition at line 39 of file side_4rios.vhd.

Member Data Documentation

ADJUST_TIME_ANDREJ in integer range 0 to 32 [Port] |

ADJUST_TIME_ANDREJ2 in integer range 0 to 32 [Port] |

ADJUST_TIME_EWA in integer range 0 to 32 [Port] |

ADJUST_TIME_EWA2 in integer range 0 to 32 [Port] |

ADJUST_TIME_HEINZ in integer range 0 to 32 [Port] |

ADJUST_TIME_HEINZ2 in integer range 0 to 32 [Port] |

ADJUST_TIME_IRENA in integer range 0 to 32 [Port] |

ADJUST_TIME_IRENA2 in integer range 0 to 32 [Port] |

BCLK in std_logic [Port] |

BCLK2X in std_logic [Port] |

BCLK4X in std_logic [Port] |

CAL in std_logic [Port] |

enable calibration procedure, deassert once CAL_DONE = 1

Definition at line 54 of file side_4rios.vhd.

CAL_ANDREJ in std_logic [Port] |

CAL_DONE out std_logic [Port] |

CAL_EWA in std_logic [Port] |

CAL_HEINZ in std_logic [Port] |

CAL_IRENA in std_logic [Port] |

CHECK_ANDREJ out std_logic [Port] |

CHECK_EWA out std_logic [Port] |

CHECK_HEINZ out std_logic [Port] |

CHECK_IRENA out std_logic [Port] |

COARSE_TIME_ANDREJ in std_logic_vector ( 7 downto 0 ) [Port] |

COARSE_TIME_EWA in std_logic_vector ( 7 downto 0 ) [Port] |

COARSE_TIME_HEINZ in std_logic_vector ( 7 downto 0 ) [Port] |

COARSE_TIME_IRENA in std_logic_vector ( 7 downto 0 ) [Port] |

EN in std_logic [Port] |

ieee library [Library] |

standard IEEE library

Reimplemented in main_components.

Definition at line 24 of file side_4rios.vhd.

MASK_ANDREJ out std_logic [Port] |

MASK_EWA out std_logic [Port] |

MASK_HEINZ out std_logic [Port] |

MASK_IRENA out std_logic [Port] |

OVERFLOW_ANDREJ out std_logic [Port] |

OVERFLOW_EWA out std_logic [Port] |

OVERFLOW_HEINZ out std_logic [Port] |

OVERFLOW_IRENA out std_logic [Port] |

PATTERN std_logic_vector ( 31 downto 0 ) := " 11110000111100001111000011110000 " [Generic] |

RAW_DATA_ANDREJ out std_logic_vector ( 31 downto 0 ) [Port] |

RAW_DATA_EWA out std_logic_vector ( 31 downto 0 ) [Port] |

RAW_DATA_HEINZ out std_logic_vector ( 31 downto 0 ) [Port] |

RAW_DATA_IRENA out std_logic_vector ( 31 downto 0 ) [Port] |

RES in std_logic [Port] |

RIOCLK_1 in std_logic [Port] |

RIOCLK_2 in std_logic [Port] |

RX1N_IN_AH in std_logic_vector ( 1 downto 0 ) [Port] |

RX1N_IN_IE in std_logic_vector ( 1 downto 0 ) [Port] |

RX1P_IN_AH in std_logic_vector ( 1 downto 0 ) [Port] |

RX1P_IN_IE in std_logic_vector ( 1 downto 0 ) [Port] |

RX_READY_FLAG_AH out std_logic [Port] |

RX_READY_FLAG_IE out std_logic [Port] |

RX_SYSTEM_RESET_IN in std_logic [Port] |

RXLOCK_OUT_ANDREJ out std_logic [Port] |

RXLOCK_OUT_EWA out std_logic [Port] |

RXLOCK_OUT_HEINZ out std_logic [Port] |

RXLOCK_OUT_IRENA out std_logic [Port] |

SEP_RES in std_logic_vector ( 3 downto 0 ) [Port] |

SET_SHIFT_1 in std_logic_vector ( 7 downto 0 ) [Port] |

SET_SHIFT_2 in std_logic_vector ( 7 downto 0 ) [Port] |

STATUS_T1_ANDREJ out std_logic [Port] |

STATUS_T1_EWA out std_logic [Port] |

STATUS_T1_HEINZ out std_logic [Port] |

STATUS_T1_IRENA out std_logic [Port] |

STATUS_T2_ANDREJ out std_logic [Port] |

STATUS_T2_EWA out std_logic [Port] |

STATUS_T2_HEINZ out std_logic [Port] |

STATUS_T2_IRENA out std_logic [Port] |

STATUS_T3_ANDREJ out std_logic [Port] |

STATUS_T3_EWA out std_logic [Port] |

STATUS_T3_HEINZ out std_logic [Port] |

STATUS_T3_IRENA out std_logic [Port] |

STATUS_W1_ANDREJ out std_logic [Port] |

STATUS_W1_EWA out std_logic [Port] |

STATUS_W1_HEINZ out std_logic [Port] |

STATUS_W1_IRENA out std_logic [Port] |

STATUS_W2_ANDREJ out std_logic [Port] |

STATUS_W2_EWA out std_logic [Port] |

STATUS_W2_HEINZ out std_logic [Port] |

STATUS_W2_IRENA out std_logic [Port] |

STATUS_W3_ANDREJ out std_logic [Port] |

STATUS_W3_EWA out std_logic [Port] |

STATUS_W3_HEINZ out std_logic [Port] |

STATUS_W3_IRENA out std_logic [Port] |

std_logic_1164 package [Package] |

std_logic definitions, see file

Reimplemented in main_components.

Definition at line 26 of file side_4rios.vhd.

std_logic_arith package [Package] |

arithmetic operations on std_logic datatypes, see file

Definition at line 28 of file side_4rios.vhd.

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 30 of file side_4rios.vhd.

SUM_FAL_ANDREJ out std_logic_vector ( 7 downto 0 ) [Port] |

SUM_FAL_EWA out std_logic_vector ( 7 downto 0 ) [Port] |

SUM_FAL_HEINZ out std_logic_vector ( 7 downto 0 ) [Port] |

SUM_FAL_IRENA out std_logic_vector ( 7 downto 0 ) [Port] |

SUM_RIS_ANDREJ out std_logic_vector ( 7 downto 0 ) [Port] |

SUM_RIS_EWA out std_logic_vector ( 7 downto 0 ) [Port] |

SUM_RIS_HEINZ out std_logic_vector ( 7 downto 0 ) [Port] |

SUM_RIS_IRENA out std_logic_vector ( 7 downto 0 ) [Port] |

T1_ANDREJ out std_logic_vector ( 7 downto 0 ) [Port] |

T1_EWA out std_logic_vector ( 7 downto 0 ) [Port] |

T1_HEINZ out std_logic_vector ( 7 downto 0 ) [Port] |

T1_IRENA out std_logic_vector ( 7 downto 0 ) [Port] |

T2_ANDREJ out std_logic_vector ( 7 downto 0 ) [Port] |

T2_EWA out std_logic_vector ( 7 downto 0 ) [Port] |

T2_HEINZ out std_logic_vector ( 7 downto 0 ) [Port] |

T2_IRENA out std_logic_vector ( 7 downto 0 ) [Port] |

T3_ANDREJ out std_logic_vector ( 7 downto 0 ) [Port] |

T3_EWA out std_logic_vector ( 7 downto 0 ) [Port] |

T3_HEINZ out std_logic_vector ( 7 downto 0 ) [Port] |

T3_IRENA out std_logic_vector ( 7 downto 0 ) [Port] |

TX1N_OUT_AH out std_logic_vector ( 1 downto 0 ) [Port] |

TX1N_OUT_IE out std_logic_vector ( 1 downto 0 ) [Port] |

TX1P_OUT_AH out std_logic_vector ( 1 downto 0 ) [Port] |

TX1P_OUT_IE out std_logic_vector ( 1 downto 0 ) [Port] |

TX_READY_FLAG_AH out std_logic [Port] |

TX_READY_FLAG_IE out std_logic [Port] |

TX_SYSTEM_RESET_IN in std_logic [Port] |

TXLOCK_OUT_ANDREJ out std_logic [Port] |

TXLOCK_OUT_EWA out std_logic [Port] |

TXLOCK_OUT_HEINZ out std_logic [Port] |

TXLOCK_OUT_IRENA out std_logic [Port] |

unisim library [Library] |

vcomponents package [Package] |

W1_ANDREJ out std_logic_vector ( 7 downto 0 ) [Port] |

W1_EWA out std_logic_vector ( 7 downto 0 ) [Port] |

W1_HEINZ out std_logic_vector ( 7 downto 0 ) [Port] |

W1_IRENA out std_logic_vector ( 7 downto 0 ) [Port] |

W2_ANDREJ out std_logic_vector ( 7 downto 0 ) [Port] |

W2_EWA out std_logic_vector ( 7 downto 0 ) [Port] |

W2_HEINZ out std_logic_vector ( 7 downto 0 ) [Port] |

W2_IRENA out std_logic_vector ( 7 downto 0 ) [Port] |

W3_ANDREJ out std_logic_vector ( 7 downto 0 ) [Port] |

W3_EWA out std_logic_vector ( 7 downto 0 ) [Port] |

W3_HEINZ out std_logic_vector ( 7 downto 0 ) [Port] |

W3_IRENA out std_logic_vector ( 7 downto 0 ) [Port] |

The documentation for this class was generated from the following file: