rios_all.rios_all_arc Architecture Reference

Combination of RocketIOs for each side of the IP. More...

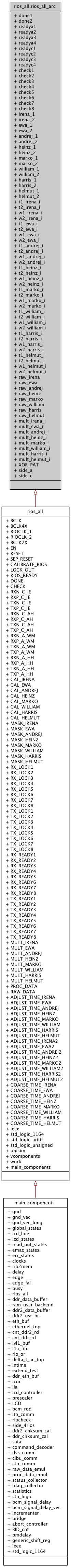

Inheritance diagram for rios_all.rios_all_arc:

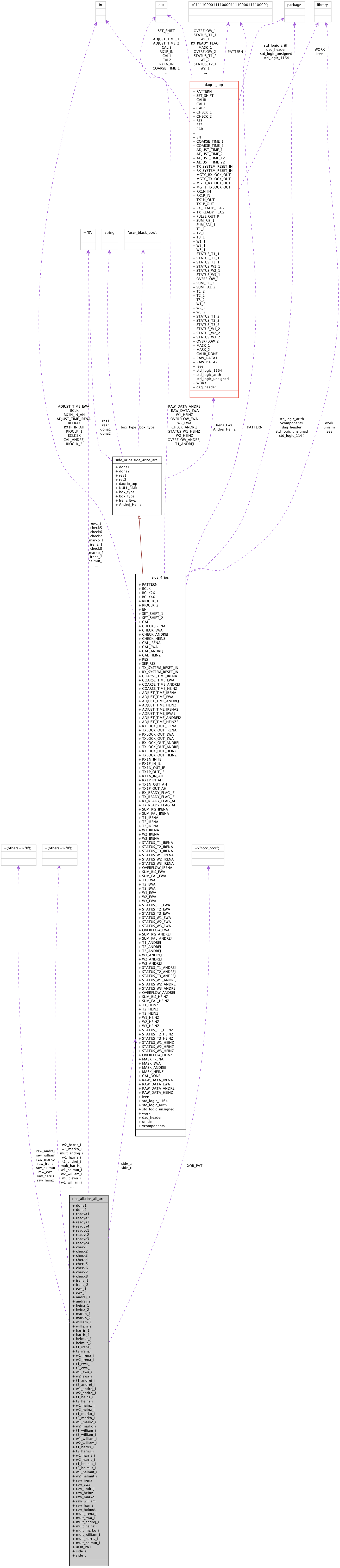

Collaboration diagram for rios_all.rios_all_arc:

Constants | |

| XOR_PAT | std_logic_vector ( 31 downto 0 ) := x " cccc_cccc " |

| external XOR pattern | |

Signals | |

| done1 | std_logic := ' 0 ' |

| done2 | std_logic := ' 0 ' |

| readya1 | std_logic := ' 0 ' |

| readya2 | std_logic := ' 0 ' |

| readya3 | std_logic := ' 0 ' |

| readya4 | std_logic := ' 0 ' |

| readyc1 | std_logic := ' 0 ' |

| readyc2 | std_logic := ' 0 ' |

| readyc3 | std_logic := ' 0 ' |

| readyc4 | std_logic := ' 0 ' |

| check1 | std_logic := ' 0 ' |

| check2 | std_logic := ' 0 ' |

| check3 | std_logic := ' 0 ' |

| check4 | std_logic := ' 0 ' |

| check5 | std_logic := ' 0 ' |

| check6 | std_logic := ' 0 ' |

| check7 | std_logic := ' 0 ' |

| check8 | std_logic := ' 0 ' |

| irena_1 | std_logic := ' 0 ' |

| irena_2 | std_logic := ' 0 ' |

| ewa_1 | std_logic := ' 0 ' |

| ewa_2 | std_logic := ' 0 ' |

| andrej_1 | std_logic := ' 0 ' |

| andrej_2 | std_logic := ' 0 ' |

| heinz_1 | std_logic := ' 0 ' |

| heinz_2 | std_logic := ' 0 ' |

| marko_1 | std_logic := ' 0 ' |

| marko_2 | std_logic := ' 0 ' |

| william_1 | std_logic := ' 0 ' |

| william_2 | std_logic := ' 0 ' |

| harris_1 | std_logic := ' 0 ' |

| harris_2 | std_logic := ' 0 ' |

| helmut_1 | std_logic := ' 0 ' |

| helmut_2 | std_logic := ' 0 ' |

| t1_irena_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| t2_irena_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| w1_irena_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| w2_irena_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| t1_ewa_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| t2_ewa_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| w1_ewa_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| w2_ewa_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| t1_andrej_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| t2_andrej_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| w1_andrej_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| w2_andrej_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| t1_heinz_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| t2_heinz_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| w1_heinz_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| w2_heinz_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| t1_marko_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| t2_marko_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| w1_marko_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| w2_marko_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| t1_william_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| t2_william_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| w1_william_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| w2_william_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| t1_harris_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| t2_harris_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| w1_harris_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| w2_harris_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| t1_helmut_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| t2_helmut_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| w1_helmut_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| w2_helmut_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| raw_irena | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| raw_ewa | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| raw_andrej | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| raw_heinz | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| raw_marko | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| raw_william | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| raw_harris | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| raw_helmut | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| mult_irena_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| mult_ewa_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| mult_andrej_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| mult_heinz_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| mult_marko_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| mult_william_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| mult_harris_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| mult_helmut_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

Component Instantiations | |

| side_a | side_4rios <Entity side_4rios> |

| Side A. | |

| side_c | side_4rios <Entity side_4rios> |

| Side C. | |

Detailed Description

Combination of RocketIOs for each side of the IP.Definition at line 157 of file rios_all.vhd.

Member Data Documentation

side_a side_4rios [Component Instantiation] |

side_c side_4rios [Component Instantiation] |

XOR_PAT std_logic_vector ( 31 downto 0 ) := x " cccc_cccc " [Constant] |

The documentation for this class was generated from the following file: