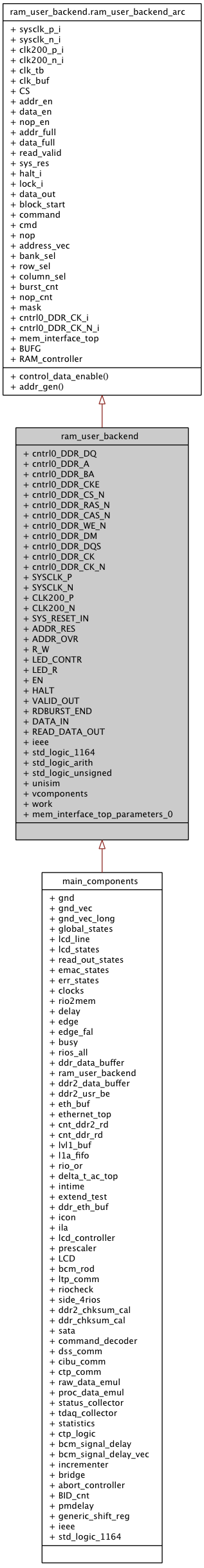

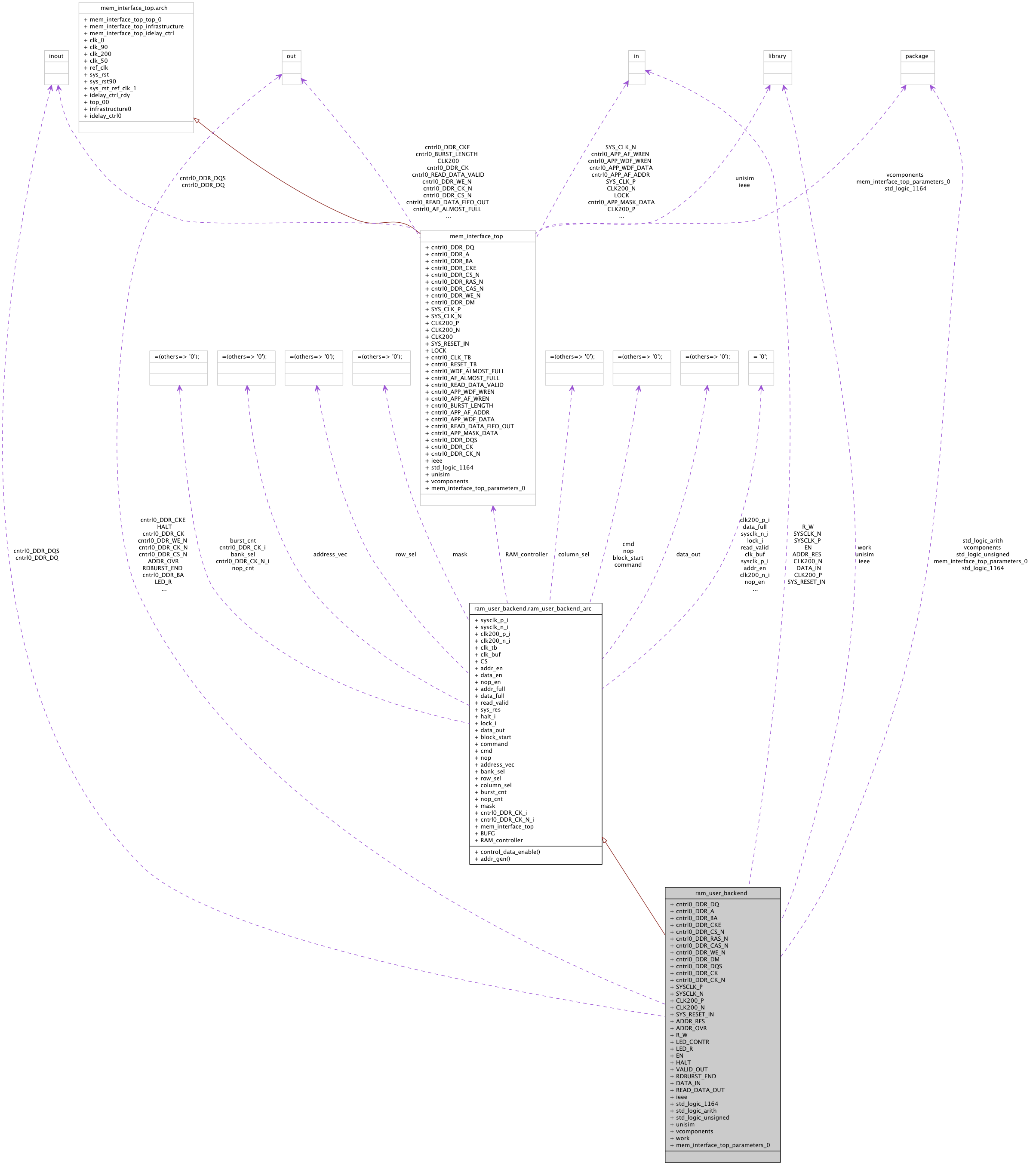

ram_user_backend Entity Reference

Top module of DDR RAM controller. More...

Architectures | |

| ram_user_backend_arc | Architecture |

| Control of interface to external RAM. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| unisim | |

| Library with Xilinx primitives. | |

| work | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

| vcomponents | |

| Header with Xilinx primitives. | |

| mem_interface_top_parameters_0 | Package <mem_interface_top_parameters_0> |

| parameters for DDR RAM controller | |

Ports | |

| cntrl0_DDR_DQ | inout std_logic_vector ( 31 downto 0 ) |

| data to/from RAM | |

| cntrl0_DDR_A | out std_logic_vector ( 12 downto 0 ) |

| address to RAM | |

| cntrl0_DDR_BA | out std_logic_vector ( 1 downto 0 ) |

| Bank select to RAM. | |

| cntrl0_DDR_CKE | out std_logic |

| CLK Enable to RAM. | |

| cntrl0_DDR_CS_N | out std_logic |

| CS to RAM, must be 0. | |

| cntrl0_DDR_RAS_N | out std_logic |

| RAS to RAM. | |

| cntrl0_DDR_CAS_N | out std_logic |

| CAS to RAM. | |

| cntrl0_DDR_WE_N | out std_logic |

| Write EN to RAM. | |

| cntrl0_DDR_DM | out std_logic_vector ( 3 downto 0 ) |

| Data Mask to RAM, 0 = data valid, 1 = data masked. | |

| cntrl0_DDR_DQS | inout std_logic_vector ( 3 downto 0 ) |

| data strobe to/from RAM | |

| cntrl0_DDR_CK | out std_logic |

| diff CLK to RAM p | |

| cntrl0_DDR_CK_N | out std_logic |

| diff CLK to RAM n | |

| SYSCLK_P | in std_logic |

| diff 160 MHz p, working frequency of memory | |

| SYSCLK_N | in std_logic |

| diff 160 MHz n, unused | |

| CLK200_P | in std_logic |

| diff 200 MHz p, reference clock of IDELAY primitives | |

| CLK200_N | in std_logic |

| diff 200 MHz n, unused | |

| SYS_RESET_IN | in std_logic |

| reset | |

| ADDR_RES | in std_logic |

| reset address counters | |

| ADDR_OVR | out std_logic |

| Address counter overflow flag. | |

| R_W | in std_logic |

| switch between read = 1 and write = 0 | |

| LED_CONTR | out std_logic |

| debug LED | |

| LED_R | out std_logic |

| debug LED | |

| EN | in std_logic |

| enable | |

| HALT | out std_logic |

| communication line for buffers | |

| VALID_OUT | out std_logic |

| data out valid | |

| RDBURST_END | out std_logic |

| end of read burst flag | |

| DATA_IN | in std_logic_vector ( 63 downto 0 ) |

| data in | |

| READ_DATA_OUT | out std_logic_vector ( 63 downto 0 ) |

| data out, same mapping | |

Detailed Description

Top module of DDR RAM controller.Interface of DDR RAM to rest of FPGA. All other modules needed for controlling the external DDR RAM are inherited from here.

Definition at line 42 of file ram_user_backend.vhd.

Member Data Documentation

ADDR_OVR out std_logic [Port] |

ADDR_RES in std_logic [Port] |

CLK200_N in std_logic [Port] |

CLK200_P in std_logic [Port] |

diff 200 MHz p, reference clock of IDELAY primitives

Definition at line 59 of file ram_user_backend.vhd.

cntrl0_DDR_A out std_logic_vector ( 12 downto 0 ) [Port] |

cntrl0_DDR_BA out std_logic_vector ( 1 downto 0 ) [Port] |

cntrl0_DDR_CAS_N out std_logic [Port] |

cntrl0_DDR_CK out std_logic [Port] |

cntrl0_DDR_CK_N out std_logic [Port] |

cntrl0_DDR_CKE out std_logic [Port] |

cntrl0_DDR_CS_N out std_logic [Port] |

cntrl0_DDR_DM out std_logic_vector ( 3 downto 0 ) [Port] |

Data Mask to RAM, 0 = data valid, 1 = data masked.

Definition at line 53 of file ram_user_backend.vhd.

cntrl0_DDR_DQ inout std_logic_vector ( 31 downto 0 ) [Port] |

cntrl0_DDR_DQS inout std_logic_vector ( 3 downto 0 ) [Port] |

cntrl0_DDR_RAS_N out std_logic [Port] |

cntrl0_DDR_WE_N out std_logic [Port] |

DATA_IN in std_logic_vector ( 63 downto 0 ) [Port] |

EN in std_logic [Port] |

HALT out std_logic [Port] |

ieee library [Library] |

standard IEEE library

Reimplemented in main_components.

Definition at line 24 of file ram_user_backend.vhd.

LED_CONTR out std_logic [Port] |

LED_R out std_logic [Port] |

mem_interface_top_parameters_0 package [Package] |

R_W in std_logic [Port] |

RDBURST_END out std_logic [Port] |

READ_DATA_OUT out std_logic_vector ( 63 downto 0 ) [Port] |

std_logic_1164 package [Package] |

std_logic definitions, see file

Reimplemented in main_components.

Definition at line 26 of file ram_user_backend.vhd.

std_logic_arith package [Package] |

arithmetic operations on std_logic datatypes, see file

Definition at line 28 of file ram_user_backend.vhd.

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 30 of file ram_user_backend.vhd.

SYS_RESET_IN in std_logic [Port] |

SYSCLK_N in std_logic [Port] |

SYSCLK_P in std_logic [Port] |

unisim library [Library] |

VALID_OUT out std_logic [Port] |

vcomponents package [Package] |

The documentation for this class was generated from the following file: