mem_interface_top_parameters_0 Package Reference

Header file for DDR RAM controller. More...

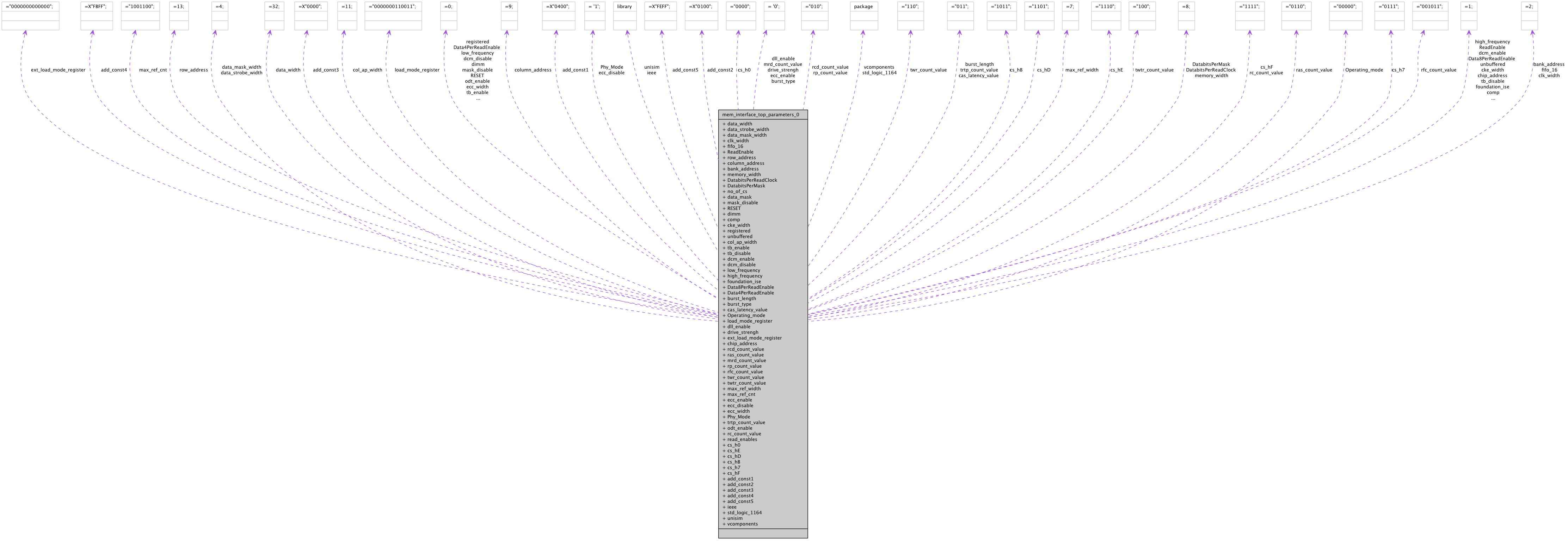

Collaboration diagram for mem_interface_top_parameters_0:

Libraries | |

| ieee | |

| standard IEEE library | |

| unisim | |

| Library with Xilinx primitives. | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| vcomponents | |

| Header with Xilinx primitives. | |

Constants | |

| data_width | integer := 32 |

| data_strobe_width | integer := 4 |

| data_mask_width | integer := 4 |

| clk_width | integer := 2 |

| fifo_16 | integer := 2 |

| ReadEnable | integer := 1 |

| row_address | integer := 13 |

| column_address | integer := 9 |

| bank_address | integer := 2 |

| memory_width | integer := 8 |

| DatabitsPerReadClock | integer := 8 |

| DatabitsPerMask | integer := 8 |

| no_of_cs | integer := 1 |

| data_mask | integer := 1 |

| mask_disable | integer := 0 |

| RESET | integer := 0 |

| dimm | integer := 0 |

| comp | integer := 1 |

| cke_width | integer := 1 |

| registered | integer := 0 |

| unbuffered | integer := 1 |

| col_ap_width | integer := 11 |

| tb_enable | integer := 0 |

| tb_disable | integer := 1 |

| dcm_enable | integer := 1 |

| dcm_disable | integer := 0 |

| low_frequency | integer := 0 |

| high_frequency | integer := 1 |

| foundation_ise | integer := 1 |

| Data8PerReadEnable | integer := 1 |

| Data4PerReadEnable | integer := 0 |

| burst_length | std_logic_vector ( 2 downto 0 ) := " 011 " |

| burst_type | std_logic := ' 0 ' |

| cas_latency_value | std_logic_vector ( 2 downto 0 ) := " 011 " |

| Operating_mode | std_logic_vector ( 4 downto 0 ) := " 00000 " |

| load_mode_register | std_logic_vector ( 12 downto 0 ) := " 0000000110011 " |

| dll_enable | std_logic := ' 0 ' |

| drive_strengh | std_logic := ' 0 ' |

| ext_load_mode_register | std_logic_vector ( 12 downto 0 ) := " 0000000000000 " |

| chip_address | integer := 1 |

| rcd_count_value | std_logic_vector ( 2 downto 0 ) := " 010 " |

| ras_count_value | std_logic_vector ( 3 downto 0 ) := " 0110 " |

| mrd_count_value | std_logic := ' 0 ' |

| rp_count_value | std_logic_vector ( 2 downto 0 ) := " 010 " |

| rfc_count_value | std_logic_vector ( 5 downto 0 ) := " 001011 " |

| twr_count_value | std_logic_vector ( 2 downto 0 ) := " 110 " |

| twtr_count_value | std_logic_vector ( 2 downto 0 ) := " 100 " |

| max_ref_width | integer := 7 |

| max_ref_cnt | std_logic_vector ( 6 downto 0 ) := " 1001100 " |

| ecc_enable | std_logic := ' 0 ' |

| ecc_disable | std_logic := ' 1 ' |

| ecc_width | integer := 0 |

| Phy_Mode | std_logic := ' 1 ' |

| trtp_count_value | std_logic_vector ( 2 downto 0 ) := " 011 " |

| odt_enable | integer := 0 |

| rc_count_value | std_logic_vector ( 3 downto 0 ) := " 1111 " |

| read_enables | integer := 1 |

| cs_h0 | std_logic_vector ( 3 downto 0 ) := " 0000 " |

| cs_hE | std_logic_vector ( 3 downto 0 ) := " 1110 " |

| cs_hD | std_logic_vector ( 3 downto 0 ) := " 1101 " |

| cs_hB | std_logic_vector ( 3 downto 0 ) := " 1011 " |

| cs_h7 | std_logic_vector ( 3 downto 0 ) := " 0111 " |

| cs_hF | std_logic_vector ( 3 downto 0 ) := " 1111 " |

| add_const1 | std_logic_vector ( 15 downto 0 ) := X " 0400 " |

| add_const2 | std_logic_vector ( 15 downto 0 ) := X " 0100 " |

| add_const3 | std_logic_vector ( 15 downto 0 ) := X " 0000 " |

| add_const4 | std_logic_vector ( 15 downto 0 ) := X " FBFF " |

| add_const5 | std_logic_vector ( 15 downto 0 ) := X " FEFF " |

Detailed Description

Header file for DDR RAM controller.According to the user inputs the parameters are defined here. These parameters are used for the generic memory interface code. Various parameters are address widths, data widths, timing parameters according to the frequency selected by the user and some internal parameters also.

Definition at line 54 of file mem_interface_top_parameters_0.vhd.

Member Data Documentation

ieee library [Library] |

std_logic_1164 package [Package] |

unisim library [Library] |

vcomponents package [Package] |

The documentation for this class was generated from the following file: