ncm_temac.ncm_temac_arc Architecture Reference

interface to HW MAC More...

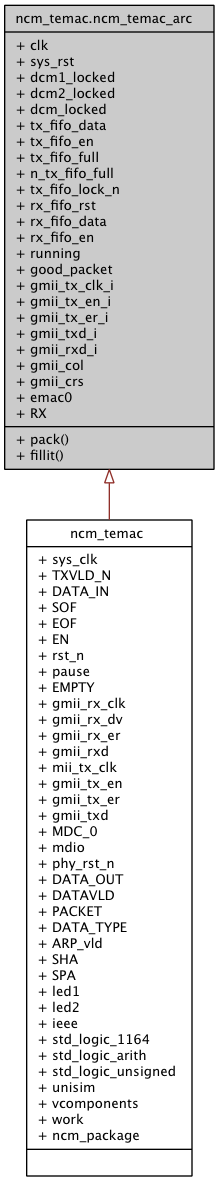

Inheritance diagram for ncm_temac.ncm_temac_arc:

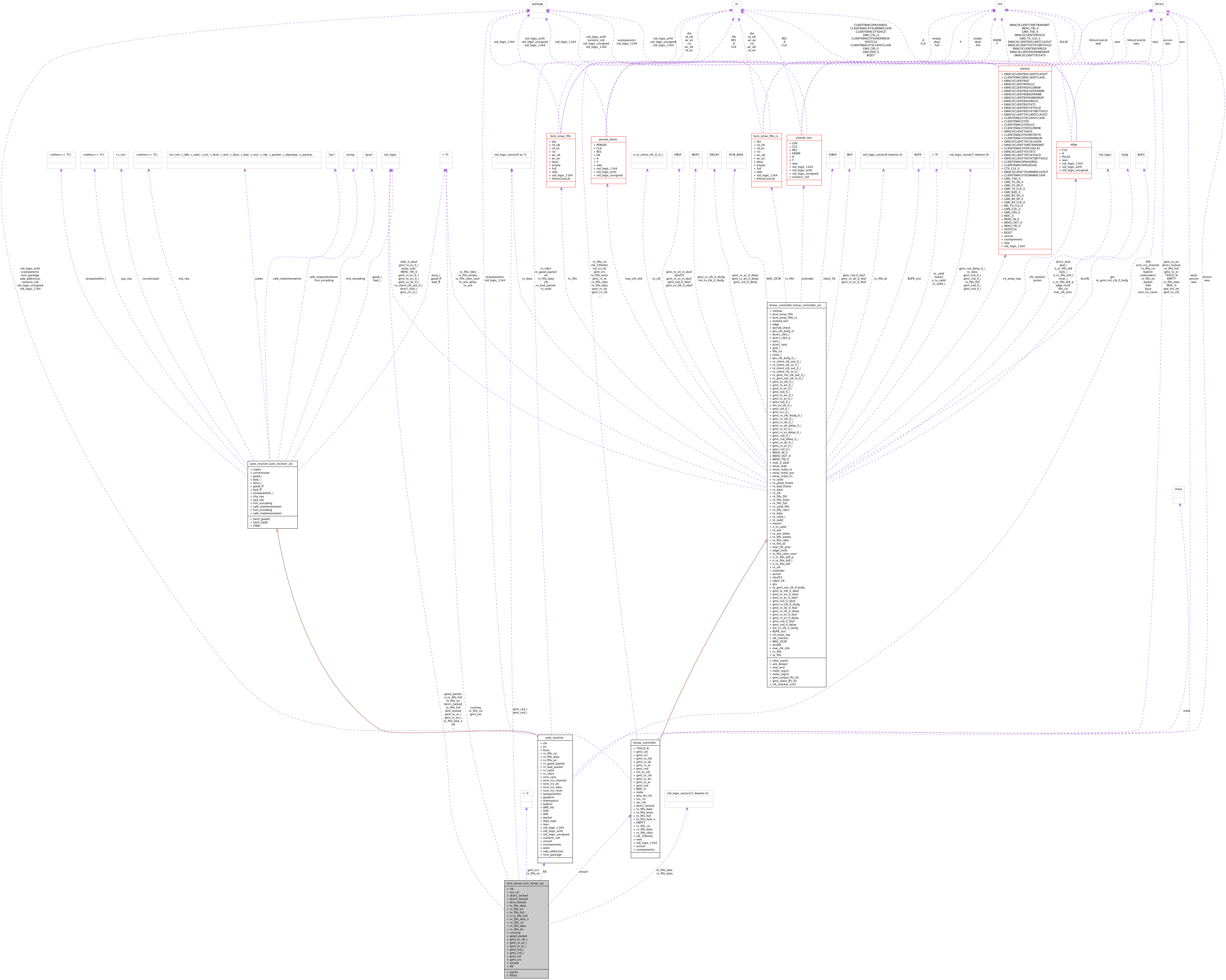

Collaboration diagram for ncm_temac.ncm_temac_arc:

Processes | |

| pack | ( clk ) |

| trigger readout from FIFO | |

| fillit | ( clk , sys_rst ) |

| encode TX data for FIFO and add EMAC control signals | |

Signals | |

| clk | std_logic |

| sys_rst | std_logic |

| dcm1_locked | std_logic |

| dcm2_locked | std_logic |

| dcm_locked | std_logic |

| tx_fifo_data | std_logic_vector ( 31 downto 0 ) |

| tx_fifo_en | std_logic |

| tx_fifo_full | std_logic |

| n_tx_fifo_full | std_logic |

| tx_fifo_lock_n | std_logic |

| rx_fifo_rst | std_logic := ' 0 ' |

| rx_fifo_data | std_logic_vector ( 31 downto 0 ) |

| rx_fifo_en | std_logic := ' 1 ' |

| running | std_logic := ' 0 ' |

| good_packet | std_logic |

| gmii_tx_clk_i | std_logic |

| gmii_tx_en_i | std_logic |

| gmii_tx_er_i | std_logic |

| gmii_txd_i | std_logic_vector ( 0 to 7 ) |

| gmii_rxd_i | std_logic_vector ( 0 to 7 ) |

| gmii_col | std_logic := ' 0 ' |

| gmii_crs | std_logic := ' 1 ' |

Component Instantiations | |

| emac0 | temac_controller <Entity temac_controller> |

| ethernet controller | |

| RX | auto_receiver <Entity auto_receiver> |

| RX data decoder. | |

Detailed Description

interface to HW MACPrepares control and data signals for HW MAC

Definition at line 75 of file ncm_temac.vhd.

Member Function Documentation

| fillit | ( clk , | |

| sys_rst ) |

encode TX data for FIFO and add EMAC control signals

Definition at line 218 of file ncm_temac.vhd.

00218 fillit : process(clk, sys_rst) 00219 begin 00220 if (sys_rst = '1') then 00221 running <= '0'; 00222 tx_fifo_data <= x"ffffffff"; 00223 elsif rising_edge(clk) then 00224 if EN = '1' then 00225 if EOF = '0' and running = '1' then 00226 running <= '0'; 00227 tx_fifo_data <= x"000000" & DATA_IN; 00228 elsif running = '1' then 00229 tx_fifo_data <= x"000001" & DATA_IN; 00230 elsif SOF = '0' then 00231 running <= '1'; 00232 tx_fifo_data <= x"000001ff"; 00233 else 00234 running <= '0'; 00235 tx_fifo_data <= x"ffffffff"; 00236 end if; 00237 else 00238 running <= '0'; 00239 tx_fifo_data <= x"ffffffff"; 00240 end if; 00241 end if; 00242 end process;

| pack | ( clk ) |

trigger readout from FIFO

Definition at line 163 of file ncm_temac.vhd.

00163 pack : process(clk) 00164 variable last_good : std_logic := '0'; 00165 variable cnt : integer range 0 to 1000 := 0; 00166 begin 00167 if (rising_edge(clk)) then 00168 00169 if (cnt = 0) then 00170 if (last_good = '0' and rx_fifo_data(22) = '1') then 00171 cnt := 999; 00172 good_packet <= '1'; 00173 else 00174 last_good := rx_fifo_data(22); 00175 good_packet <= '0'; 00176 end if; 00177 00178 else 00179 last_good := rx_fifo_data(22); 00180 cnt := cnt - 1; 00181 end if; 00182 00183 end if; 00184 end process;

Member Data Documentation

emac0 temac_controller [Component Instantiation] |

RX auto_receiver [Component Instantiation] |

The documentation for this class was generated from the following file: