ncm_temac Entity Reference

interface to HW MAC More...

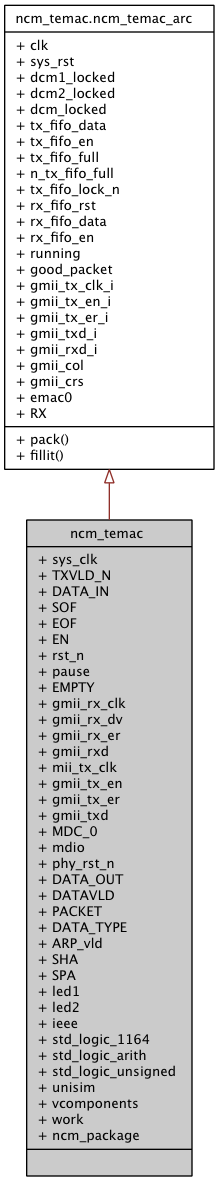

Inheritance diagram for ncm_temac:

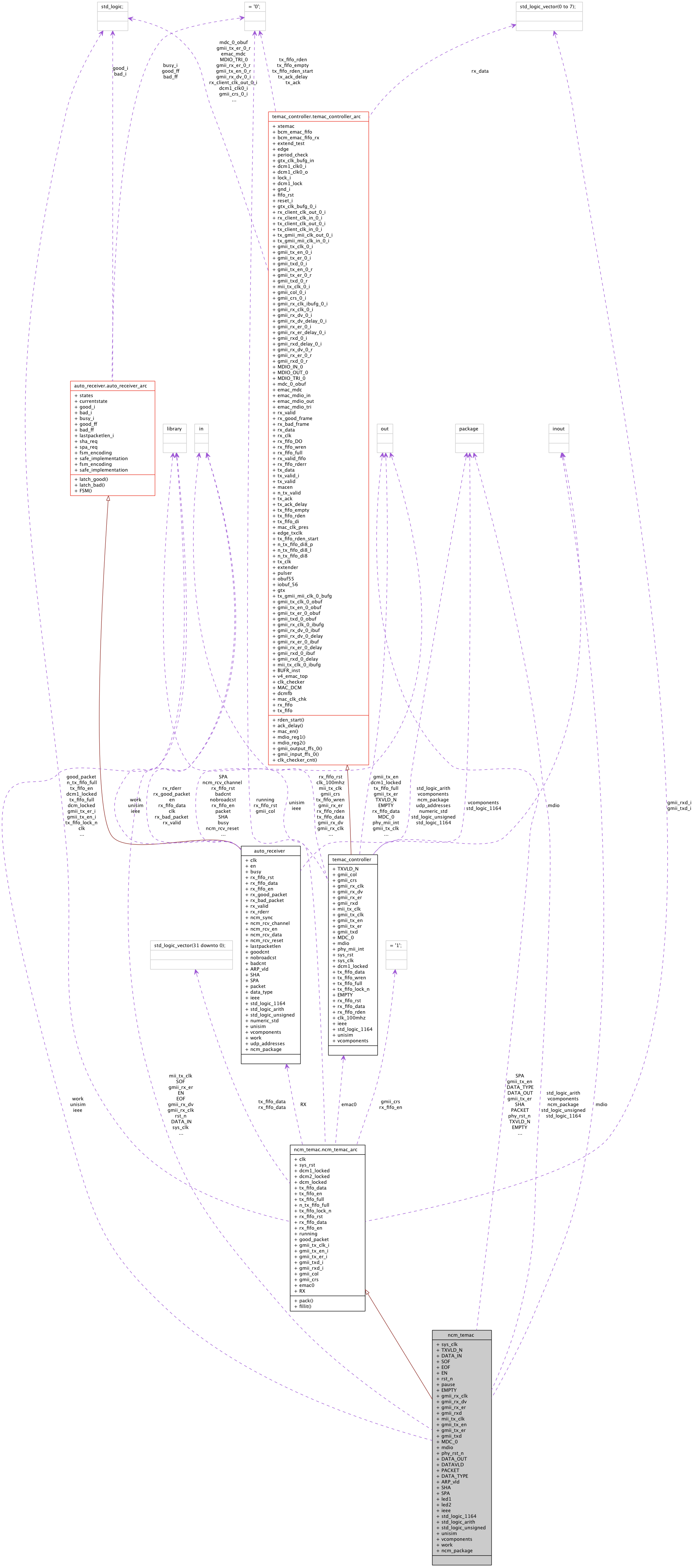

Collaboration diagram for ncm_temac:

Architectures | |

| ncm_temac_arc | Architecture |

| interface to HW MAC More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| unisim | |

| Library with Xilinx primitives. | |

| work | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

| vcomponents | |

| Header with Xilinx primitives. | |

| ncm_package | Package <ncm_package> |

Ports | |

| sys_clk | in std_logic |

| Clock. | |

| TXVLD_N | out std_logic |

| debug | |

| DATA_IN | in std_logic_vector ( 7 downto 0 ) |

| databyte to send | |

| SOF | in std_logic |

| Start of frame flag. | |

| EOF | in std_logic |

| End of frame flag. | |

| EN | in std_logic |

| Enable. | |

| rst_n | in std_logic |

| Reset, active low. | |

| pause | out std_logic |

| debug | |

| EMPTY | out std_logic |

| TX FIFO empty flag. | |

| gmii_rx_clk | in std_logic |

| GMII PHY. | |

| gmii_rx_dv | in std_logic |

| GMII PHY. | |

| gmii_rx_er | in std_logic |

| GMII PHY. | |

| gmii_rxd | in std_logic_vector ( 0 to 7 ) |

| GMII PHY. | |

| mii_tx_clk | in std_logic |

| GMII PHY. | |

| gmii_tx_en | out std_logic |

| GMII PHY. | |

| gmii_tx_er | out std_logic |

| GMII PHY. | |

| gmii_txd | out std_logic_vector ( 0 to 3 ) |

| GMII PHY. | |

| MDC_0 | out std_logic |

| GMII PHY. | |

| mdio | inout std_logic |

| GMII PHY. | |

| phy_rst_n | out std_logic |

| GMII PHY. | |

| DATA_OUT | out std_logic_vector ( 7 downto 0 ) |

| databyte received | |

| DATAVLD | out std_logic |

| RX data valid. | |

| PACKET | out std_logic_vector ( 19 downto 0 ) |

| RX packet-nr. | |

| DATA_TYPE | out std_logic_vector ( 11 downto 0 ) |

| RX packet-type. | |

| ARP_vld | out std_logic |

| ARP request flag. | |

| SHA | out std_logic_vector ( 47 downto 0 ) |

| ARP SHA. | |

| SPA | out std_logic_vector ( 31 downto 0 ) |

| ARP SPA. | |

| led1 | out std_logic |

| debug | |

| led2 | out std_logic |

| debug | |

Detailed Description

interface to HW MACPrepares control and data signals for HW MAC

Definition at line 40 of file ncm_temac.vhd.

Member Data Documentation

ARP_vld out std_logic [Port] |

DATA_IN in std_logic_vector ( 7 downto 0 ) [Port] |

DATA_OUT out std_logic_vector ( 7 downto 0 ) [Port] |

DATA_TYPE out std_logic_vector ( 11 downto 0 ) [Port] |

DATAVLD out std_logic [Port] |

EMPTY out std_logic [Port] |

EN in std_logic [Port] |

EOF in std_logic [Port] |

gmii_rx_clk in std_logic [Port] |

gmii_rx_dv in std_logic [Port] |

gmii_rx_er in std_logic [Port] |

gmii_rxd in std_logic_vector ( 0 to 7 ) [Port] |

gmii_tx_en out std_logic [Port] |

gmii_tx_er out std_logic [Port] |

gmii_txd out std_logic_vector ( 0 to 3 ) [Port] |

ieee library [Library] |

led1 out std_logic [Port] |

led2 out std_logic [Port] |

MDC_0 out std_logic [Port] |

mdio inout std_logic [Port] |

mii_tx_clk in std_logic [Port] |

PACKET out std_logic_vector ( 19 downto 0 ) [Port] |

pause out std_logic [Port] |

phy_rst_n out std_logic [Port] |

rst_n in std_logic [Port] |

SHA out std_logic_vector ( 47 downto 0 ) [Port] |

SOF in std_logic [Port] |

SPA out std_logic_vector ( 31 downto 0 ) [Port] |

std_logic_1164 package [Package] |

std_logic_arith package [Package] |

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 30 of file ncm_temac.vhd.

sys_clk in std_logic [Port] |

TXVLD_N out std_logic [Port] |

unisim library [Library] |

vcomponents package [Package] |

The documentation for this class was generated from the following file: