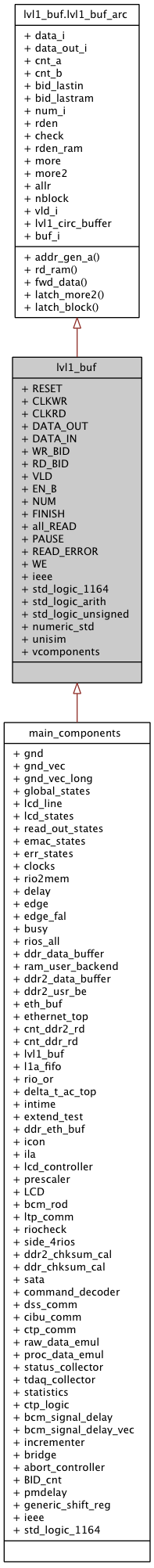

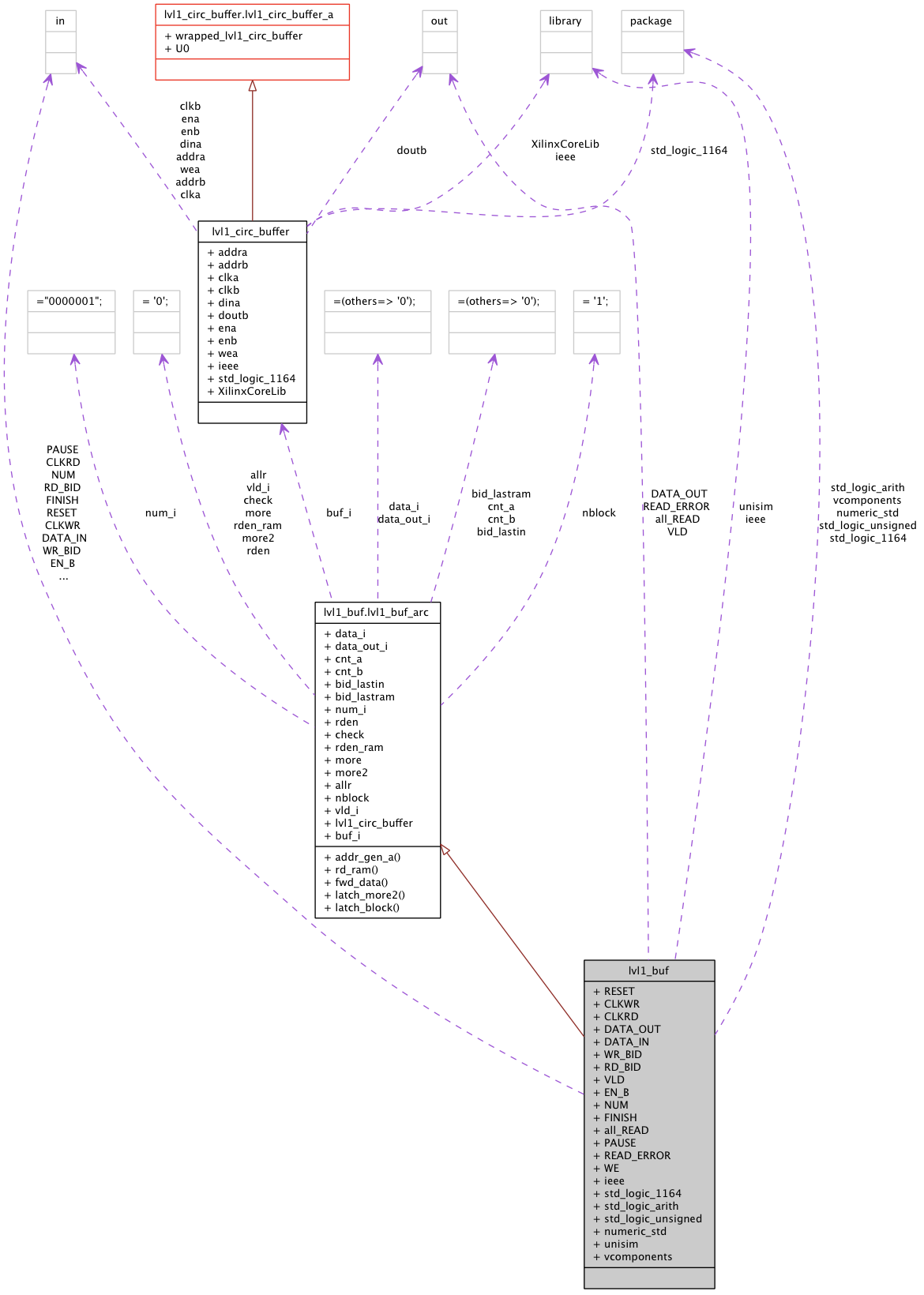

lvl1_buf Entity Reference

Buffer for Level-1 TDAQ data.

More...

List of all members.

|

Architectures |

| lvl1_buf_arc | Architecture |

| | Buffer for Level-1 TDAQ data. More...

|

Libraries |

| ieee | |

| | standard IEEE library

|

| unisim | |

| | Library with Xilinx primitives.

|

Packages |

| std_logic_1164 | |

| | std_logic definitions, see file

|

| std_logic_arith | |

| | arithmetic operations on std_logic datatypes, see file

|

| std_logic_unsigned | |

| | unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

|

| numeric_std | |

| | arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file

|

| vcomponents | |

| | Header with Xilinx primitives.

|

Ports |

| RESET | in |

| | Reset.

|

| CLKWR | in |

| | Clock for write, 40 MHz.

|

| CLKRD | in |

| | Clock for read, 40 MHz.

|

| DATA_OUT | out ( 191 downto 0 ) := ( others = > ' 0 ' ) |

| | Data out, including BID.

|

| DATA_IN | in ( 175 downto 0 ) |

| | Data in.

|

| WR_BID | in ( 11 downto 0 ) := " 000000000000 " |

| | BID of data to be written to buffer.

|

| RD_BID | in ( 11 downto 0 ) := " 000000000000 " |

| | BID to be fetched from buffer.

|

| VLD | out |

| | Valid for Data out; after EN_B goes high, no further rds will be accepted til VLD went high.

|

| EN_B | in |

| | enable read, keep high til VLD is asserted high

|

| NUM | in ( 6 downto 0 ) := " 0000001 " |

| | Number of bunches to be read per trigger.

|

| FINISH | in |

| | abort transmission

|

| all_READ | out |

| | flag signaling the specified number of bunches has been read

|

| PAUSE | in |

| | Pause read-out when ROD is busy.

|

| READ_ERROR | out |

| | Flag that an error has occurred.

|

| WE | in |

| | Write enable.

|

Detailed Description

Buffer for Level-1 TDAQ data.

This entity contains the circular buffer for the Level-1 TDAQ data. It is 500 bunch-crossings deep. Together with the data the current Bunch ID is also written to the buffer. For each read the ID of the bunch to be read needs to be provided so the buffer support logic can verify that the correct data has been read.

Definition at line 44 of file lvl1_buf.vhd.

Member Data Documentation

flag signaling the specified number of bunches has been read

Definition at line 56 of file lvl1_buf.vhd.

DATA_OUT out ( 191 downto 0 ) := ( others = > ' 0 ' ) [Port] |

enable read, keep high til VLD is asserted high

Definition at line 53 of file lvl1_buf.vhd.

NUM in ( 6 downto 0 ) := " 0000001 " [Port] |

Number of bunches to be read per trigger.

Definition at line 54 of file lvl1_buf.vhd.

arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file

Definition at line 32 of file lvl1_buf.vhd.

RD_BID in ( 11 downto 0 ) := " 000000000000 " [Port] |

BID to be fetched from buffer.

Definition at line 51 of file lvl1_buf.vhd.

Flag that an error has occurred.

Definition at line 58 of file lvl1_buf.vhd.

arithmetic operations on std_logic datatypes, see file

Definition at line 28 of file lvl1_buf.vhd.

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 30 of file lvl1_buf.vhd.

Library with Xilinx primitives.

Definition at line 34 of file lvl1_buf.vhd.

Header with Xilinx primitives.

Definition at line 36 of file lvl1_buf.vhd.

Valid for Data out; after EN_B goes high, no further rds will be accepted til VLD went high.

Definition at line 52 of file lvl1_buf.vhd.

WR_BID in ( 11 downto 0 ) := " 000000000000 " [Port] |

BID of data to be written to buffer.

Definition at line 50 of file lvl1_buf.vhd.

The documentation for this class was generated from the following file: