lvl1_buf.lvl1_buf_arc Architecture Reference

Buffer for Level-1 TDAQ data. More...

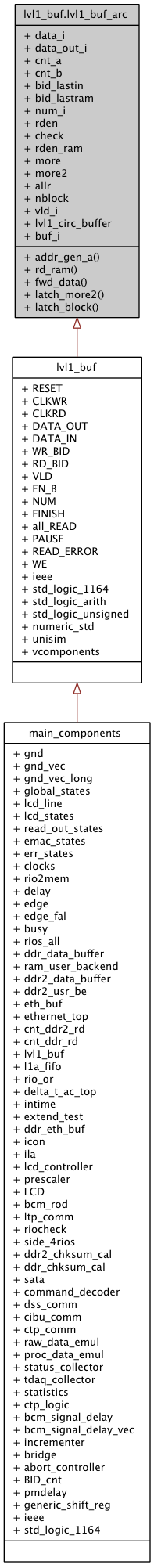

Inheritance diagram for lvl1_buf.lvl1_buf_arc:

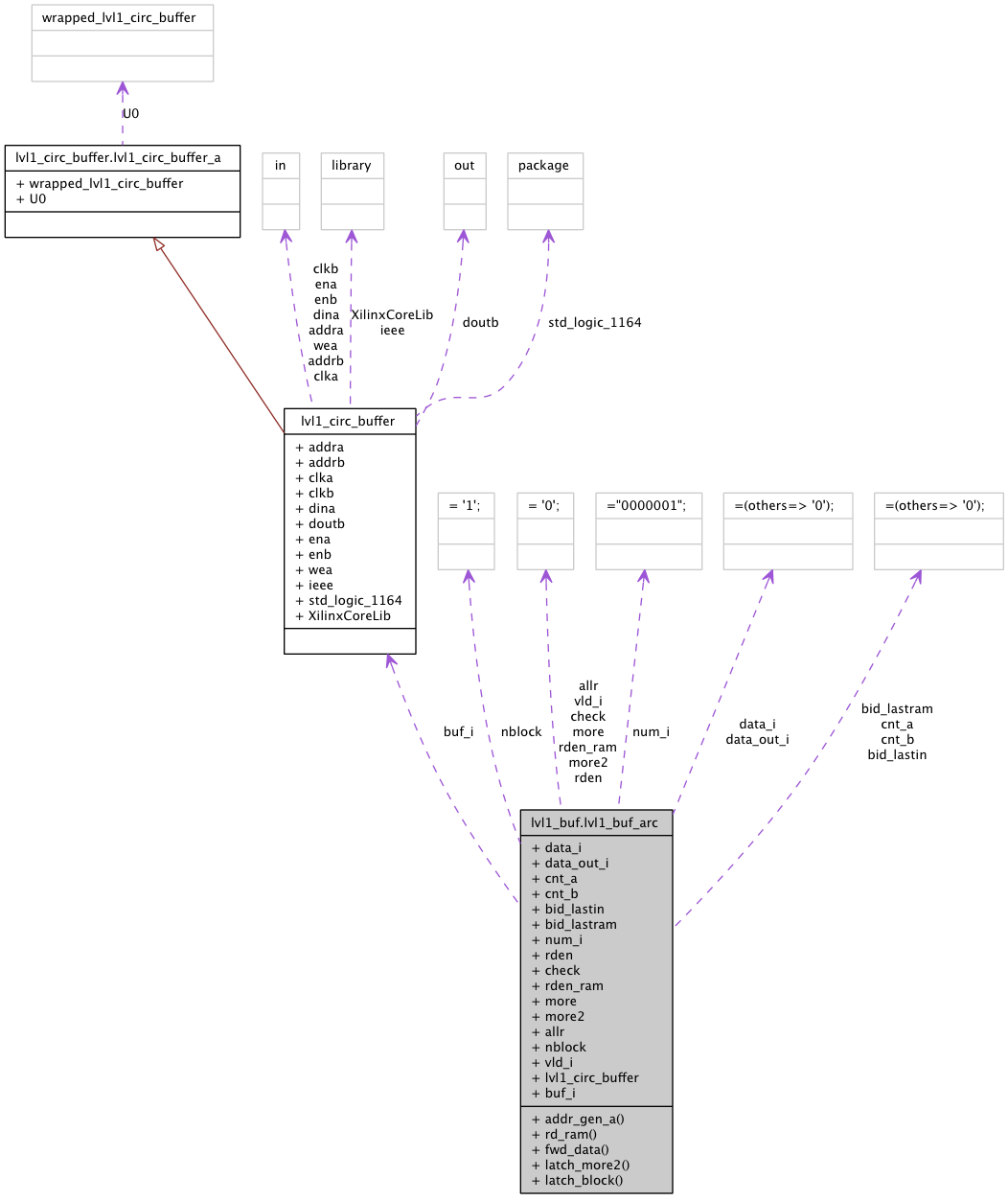

Collaboration diagram for lvl1_buf.lvl1_buf_arc:

Processes | |

| addr_gen_a | ( CLKWR ) |

| Cyclic addressing of write half. | |

| rd_ram | ( CLKRD ) |

| reading from ram | |

| fwd_data | ( CLKRD ) |

| forward data to outs | |

| latch_more2 | ( CLKRD , RESET ) |

| latch enable for more BCs | |

| latch_block | ( CLKRD , RESET ) |

| latch enable for more BCs | |

Components | |

| lvl1_circ_buffer | <Entity lvl1_circ_buffer> |

| Circular Buffer, DP-RAM as a BRAM Core. | |

Signals | |

| data_i | std_logic_vector ( 191 downto 0 ) := ( others = > ' 0 ' ) |

| data_out_i | std_logic_vector ( 191 downto 0 ) := ( others = > ' 0 ' ) |

| cnt_a | std_logic_vector ( 11 downto 0 ) := ( others = > ' 0 ' ) |

| cnt_b | std_logic_vector ( 11 downto 0 ) := ( others = > ' 0 ' ) |

| bid_lastin | std_logic_vector ( 11 downto 0 ) := ( others = > ' 0 ' ) |

| bid_lastram | std_logic_vector ( 11 downto 0 ) := ( others = > ' 0 ' ) |

| num_i | std_logic_vector ( 6 downto 0 ) := " 0000001 " |

| rden | std_logic := ' 0 ' |

| check | std_logic := ' 0 ' |

| rden_ram | std_logic := ' 0 ' |

| more | std_logic := ' 0 ' |

| more2 | std_logic := ' 0 ' |

| allr | std_logic := ' 0 ' |

| nblock | std_logic := ' 1 ' |

| vld_i | std_logic := ' 0 ' |

Component Instantiations | |

| buf_i | lvl1_circ_buffer <Entity lvl1_circ_buffer> |

| Circular Buffer, DP-RAM as a BRAM Core. | |

Detailed Description

Buffer for Level-1 TDAQ data.This entity contains the circular buffer for the Level-1 TDAQ data. It is 500 bunch-crossings deep. Together with the data the current Bunch ID is also written to the buffer. For each read the ID of the bunch to be read needs to be provided so the buffer support logic can verify that the correct data has been read.

Definition at line 69 of file lvl1_buf.vhd.

Member Function Documentation

| addr_gen_a | ( CLKWR ) |

Cyclic addressing of write half.

Definition at line 125 of file lvl1_buf.vhd.

00125 addr_gen_a : process(CLKWR) 00126 begin 00127 if CLKWR'event and CLKWR = '1' then 00128 if RESET = '1' then 00129 cnt_a <= (others => '0'); 00130 data_i <= (others => '0'); 00131 bid_lastram <= (others => '0'); 00132 bid_lastin <= (others => '0'); 00133 else 00134 if WE = '1' then 00135 cnt_a <= WR_BID; --* store last wr BID 00136 data_i <= WR_BID & DATA_IN & "0000"; 00137 bid_lastin <= WR_BID; 00138 if WR_BID = 0 then 00139 bid_lastram <= bid_lastin; 00140 else 00141 bid_lastram <= bid_lastram; 00142 end if; 00143 end if; 00144 end if; 00145 end if; 00146 end process addr_gen_a;

| fwd_data | ( CLKRD ) |

forward data to outs

Definition at line 196 of file lvl1_buf.vhd.

00196 fwd_data : process (CLKRD) 00197 begin -- process fwd_data 00198 if CLKRD'event and CLKRD = '1' then -- rising clock edge 00199 if RESET = '1' then 00200 allr <= '0'; 00201 vld_i <= '0'; 00202 DATA_OUT <= (others => '0'); 00203 else 00204 if PAUSE = '0' then 00205 00206 if check = '1' then 00207 DATA_OUT <= data_out_i; 00208 vld_i <= '1'; 00209 if more2 = '0' then 00210 allr <= '1'; 00211 else 00212 allr <= '0'; 00213 end if; 00214 00215 else 00216 allr <= '0'; 00217 vld_i <= '0'; 00218 DATA_OUT <= (others => '0'); 00219 end if; 00220 00221 else 00222 allr <= '0'; 00223 vld_i <= '0'; 00224 DATA_OUT <= (others => '0'); 00225 end if; 00226 00227 end if; 00228 end if; 00229 end process fwd_data;

| latch_block | ( CLKRD , | |

| RESET ) |

latch enable for more BCs

Definition at line 246 of file lvl1_buf.vhd.

00246 latch_block : process (CLKRD, RESET) 00247 begin -- process latch_more 00248 if RESET = '1' then -- asynchronous reset (active high) 00249 nblock <= '1'; 00250 elsif CLKRD'event and CLKRD = '1' then -- rising clock edge 00251 if vld_i = '1' then 00252 nblock <= '1'; 00253 elsif rden = '1' then 00254 nblock <= '0'; 00255 end if; 00256 end if; 00257 end process latch_block;

| latch_more2 | ( CLKRD , | |

| RESET ) |

latch enable for more BCs

Definition at line 232 of file lvl1_buf.vhd.

00232 latch_more2 : process (CLKRD, RESET) 00233 begin -- process latch_more 00234 if RESET = '1' then -- asynchronous reset (active high) 00235 more2 <= '0'; 00236 elsif CLKRD'event and CLKRD = '1' then -- rising clock edge 00237 if (num_i-1) = 0 or FINISH = '1' then 00238 more2 <= '0'; 00239 elsif more = '1' then 00240 more2 <= '1'; 00241 end if; 00242 end if; 00243 end process latch_more2;

| rd_ram | ( CLKRD ) |

reading from ram

Definition at line 149 of file lvl1_buf.vhd.

00149 rd_ram : process(CLKRD) 00150 begin 00151 if CLKRD'event and CLKRD = '1' then 00152 if RESET = '1' then 00153 cnt_b <= (others => '0'); 00154 rden_ram <= '0'; 00155 more <= '0'; 00156 else 00157 if PAUSE = '0' then 00158 00159 if EN_B = '1' then 00160 cnt_b <= RD_BID; 00161 rden_ram <= '1'; 00162 num_i <= NUM; 00163 00164 if NUM > 1 then 00165 more <= '1'; 00166 else 00167 more <= '0'; 00168 end if; 00169 00170 elsif (more2 and nblock and (not rden_ram)) = '1' then 00171 rden_ram <= '1'; 00172 num_i <= num_i - 1; 00173 cnt_b <= cnt_b + 1; 00174 if cnt_b = bid_lastram and bid_lastram > 0 then 00175 cnt_b <= (others => '0'); 00176 end if; 00177 00178 else 00179 cnt_b <= cnt_b; 00180 rden_ram <= '0'; 00181 more <= '0'; 00182 end if; 00183 00184 else 00185 cnt_b <= cnt_b; 00186 rden_ram <= '0'; 00187 end if; 00188 end if; 00189 end if; 00190 end process;

Member Data Documentation

buf_i lvl1_circ_buffer [Component Instantiation] |

lvl1_circ_buffer [Component] |

The documentation for this class was generated from the following file: