ctp_logic.ctp_logic_arc Architecture Reference

CTP logic. More...

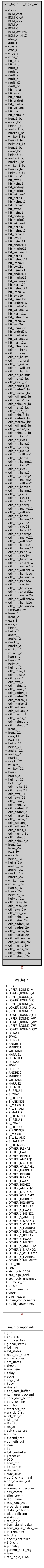

Inheritance diagram for ctp_logic.ctp_logic_arc:

Collaboration diagram for ctp_logic.ctp_logic_arc:

Components | |

| timewindow | <Entity timewindow> |

| time-window with 2 comparators | |

Signals | |

| BCM_AtoC | std_logic := ' 0 ' |

| BCM_CtoA | std_logic := ' 0 ' |

| BCM_wide | std_logic := ' 0 ' |

| BCM_A | std_logic_vector ( 1 downto 0 ) := " 00 " |

| BCM_C | std_logic_vector ( 1 downto 0 ) := " 00 " |

| BCM_AttHitA | std_logic := ' 0 ' |

| BCM_AttHitC | std_logic := ' 0 ' |

| atoc_a | std_logic := ' 0 ' |

| atoc_c | std_logic := ' 0 ' |

| ctoa_a | std_logic := ' 0 ' |

| ctoa_c | std_logic := ' 0 ' |

| wide_a | std_logic := ' 0 ' |

| wide_c | std_logic := ' 0 ' |

| hit_atta | std_logic := ' 0 ' |

| hit_attc | std_logic := ' 0 ' |

| mult_a | std_logic_vector ( 1 downto 0 ) := " 00 " |

| mult_c | std_logic_vector ( 1 downto 0 ) := " 00 " |

| mult_a1 | std_logic_vector ( 1 downto 0 ) := " 00 " |

| mult_c1 | std_logic_vector ( 1 downto 0 ) := " 00 " |

| mult_a2 | std_logic_vector ( 1 downto 0 ) := " 00 " |

| mult_c2 | std_logic_vector ( 1 downto 0 ) := " 00 " |

| hit_irena | std_logic_vector ( 1 downto 0 ) := " 00 " |

| hit_ewa | std_logic_vector ( 1 downto 0 ) := " 00 " |

| hit_heinz | std_logic_vector ( 1 downto 0 ) := " 00 " |

| hit_andrej | std_logic_vector ( 1 downto 0 ) := " 00 " |

| hit_marko | std_logic_vector ( 1 downto 0 ) := " 00 " |

| hit_william | std_logic_vector ( 1 downto 0 ) := " 00 " |

| hit_harris | std_logic_vector ( 1 downto 0 ) := " 00 " |

| hit_helmut | std_logic_vector ( 1 downto 0 ) := " 00 " |

| irena1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| ewa1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| heinz1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| andrej1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| marko1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| william1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| harris1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| helmut1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| irena2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| ewa2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| heinz2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| andrej2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| marko2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| william2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| harris2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| helmut2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| hit_irena1 | std_logic := ' 0 ' |

| hit_ewa1 | std_logic := ' 0 ' |

| hit_heinz1 | std_logic := ' 0 ' |

| hit_andrej1 | std_logic := ' 0 ' |

| hit_marko1 | std_logic := ' 0 ' |

| hit_william1 | std_logic := ' 0 ' |

| hit_harris1 | std_logic := ' 0 ' |

| hit_helmut1 | std_logic := ' 0 ' |

| hit_irena2 | std_logic := ' 0 ' |

| hit_ewa2 | std_logic := ' 0 ' |

| hit_heinz2 | std_logic := ' 0 ' |

| hit_andrej2 | std_logic := ' 0 ' |

| hit_marko2 | std_logic := ' 0 ' |

| hit_william2 | std_logic := ' 0 ' |

| hit_harris2 | std_logic := ' 0 ' |

| hit_helmut2 | std_logic := ' 0 ' |

| hit_irena11 | std_logic := ' 0 ' |

| hit_ewa11 | std_logic := ' 0 ' |

| hit_heinz11 | std_logic := ' 0 ' |

| hit_andrej11 | std_logic := ' 0 ' |

| hit_marko11 | std_logic := ' 0 ' |

| hit_william11 | std_logic := ' 0 ' |

| hit_harris11 | std_logic := ' 0 ' |

| hit_helmut11 | std_logic := ' 0 ' |

| hit_irena21 | std_logic := ' 0 ' |

| hit_ewa21 | std_logic := ' 0 ' |

| hit_heinz21 | std_logic := ' 0 ' |

| hit_andrej21 | std_logic := ' 0 ' |

| hit_marko21 | std_logic := ' 0 ' |

| hit_william21 | std_logic := ' 0 ' |

| hit_harris21 | std_logic := ' 0 ' |

| hit_helmut21 | std_logic := ' 0 ' |

| hit_irena1w | std_logic := ' 0 ' |

| hit_ewa1w | std_logic := ' 0 ' |

| hit_heinz1w | std_logic := ' 0 ' |

| hit_andrej1w | std_logic := ' 0 ' |

| hit_marko1w | std_logic := ' 0 ' |

| hit_william1w | std_logic := ' 0 ' |

| hit_harris1w | std_logic := ' 0 ' |

| hit_helmut1w | std_logic := ' 0 ' |

| hit_irena2w | std_logic := ' 0 ' |

| hit_ewa2w | std_logic := ' 0 ' |

| hit_heinz2w | std_logic := ' 0 ' |

| hit_andrej2w | std_logic := ' 0 ' |

| hit_marko2w | std_logic := ' 0 ' |

| hit_william2w | std_logic := ' 0 ' |

| hit_harris2w | std_logic := ' 0 ' |

| hit_helmut2w | std_logic := ' 0 ' |

| oth_hit_irena | std_logic_vector ( 1 downto 0 ) := " 00 " |

| oth_hit_ewa | std_logic_vector ( 1 downto 0 ) := " 00 " |

| oth_hit_heinz | std_logic_vector ( 1 downto 0 ) := " 00 " |

| oth_hit_andrej | std_logic_vector ( 1 downto 0 ) := " 00 " |

| oth_hit_marko | std_logic_vector ( 1 downto 0 ) := " 00 " |

| oth_hit_william | std_logic_vector ( 1 downto 0 ) := " 00 " |

| oth_hit_harris | std_logic_vector ( 1 downto 0 ) := " 00 " |

| oth_hit_helmut | std_logic_vector ( 1 downto 0 ) := " 00 " |

| oth_irena1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| oth_ewa1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| oth_heinz1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| oth_andrej1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| oth_marko1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| oth_william1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| oth_harris1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| oth_helmut1_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| oth_irena2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| oth_ewa2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| oth_heinz2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| oth_andrej2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| oth_marko2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| oth_william2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| oth_harris2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| oth_helmut2_bc | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| oth_hit_irena1 | std_logic := ' 0 ' |

| oth_hit_ewa1 | std_logic := ' 0 ' |

| oth_hit_heinz1 | std_logic := ' 0 ' |

| oth_hit_andrej1 | std_logic := ' 0 ' |

| oth_hit_marko1 | std_logic := ' 0 ' |

| oth_hit_william1 | std_logic := ' 0 ' |

| oth_hit_harris1 | std_logic := ' 0 ' |

| oth_hit_helmut1 | std_logic := ' 0 ' |

| oth_hit_irena2 | std_logic := ' 0 ' |

| oth_hit_ewa2 | std_logic := ' 0 ' |

| oth_hit_heinz2 | std_logic := ' 0 ' |

| oth_hit_andrej2 | std_logic := ' 0 ' |

| oth_hit_marko2 | std_logic := ' 0 ' |

| oth_hit_william2 | std_logic := ' 0 ' |

| oth_hit_harris2 | std_logic := ' 0 ' |

| oth_hit_helmut2 | std_logic := ' 0 ' |

| oth_hit_irena11 | std_logic := ' 0 ' |

| oth_hit_ewa11 | std_logic := ' 0 ' |

| oth_hit_heinz11 | std_logic := ' 0 ' |

| oth_hit_andrej11 | std_logic := ' 0 ' |

| oth_hit_marko11 | std_logic := ' 0 ' |

| oth_hit_william11 | std_logic := ' 0 ' |

| oth_hit_harris11 | std_logic := ' 0 ' |

| oth_hit_helmut11 | std_logic := ' 0 ' |

| oth_hit_irena21 | std_logic := ' 0 ' |

| oth_hit_ewa21 | std_logic := ' 0 ' |

| oth_hit_heinz21 | std_logic := ' 0 ' |

| oth_hit_andrej21 | std_logic := ' 0 ' |

| oth_hit_marko21 | std_logic := ' 0 ' |

| oth_hit_william21 | std_logic := ' 0 ' |

| oth_hit_harris21 | std_logic := ' 0 ' |

| oth_hit_helmut21 | std_logic := ' 0 ' |

| oth_hit_irena1w | std_logic := ' 0 ' |

| oth_hit_ewa1w | std_logic := ' 0 ' |

| oth_hit_heinz1w | std_logic := ' 0 ' |

| oth_hit_andrej1w | std_logic := ' 0 ' |

| oth_hit_marko1w | std_logic := ' 0 ' |

| oth_hit_william1w | std_logic := ' 0 ' |

| oth_hit_harris1w | std_logic := ' 0 ' |

| oth_hit_helmut1w | std_logic := ' 0 ' |

| oth_hit_irena2w | std_logic := ' 0 ' |

| oth_hit_ewa2w | std_logic := ' 0 ' |

| oth_hit_heinz2w | std_logic := ' 0 ' |

| oth_hit_andrej2w | std_logic := ' 0 ' |

| oth_hit_marko2w | std_logic := ' 0 ' |

| oth_hit_william2w | std_logic := ' 0 ' |

| oth_hit_harris2w | std_logic := ' 0 ' |

| oth_hit_helmut2w | std_logic := ' 0 ' |

Component Instantiations | |

| Irena_1 | timewindow <Entity timewindow> |

| Irena_2 | timewindow <Entity timewindow> |

| ewa_1 | timewindow <Entity timewindow> |

| ewa_2 | timewindow <Entity timewindow> |

| heinz_1 | timewindow <Entity timewindow> |

| heinz_2 | timewindow <Entity timewindow> |

| andrej_1 | timewindow <Entity timewindow> |

| andrej_2 | timewindow <Entity timewindow> |

| marko_1 | timewindow <Entity timewindow> |

| marko_2 | timewindow <Entity timewindow> |

| william_1 | timewindow <Entity timewindow> |

| william_2 | timewindow <Entity timewindow> |

| harris_1 | timewindow <Entity timewindow> |

| harris_2 | timewindow <Entity timewindow> |

| helmut_1 | timewindow <Entity timewindow> |

| helmut_2 | timewindow <Entity timewindow> |

| oth_Irena_1 | timewindow <Entity timewindow> |

| oth_Irena_2 | timewindow <Entity timewindow> |

| oth_ewa_1 | timewindow <Entity timewindow> |

| oth_ewa_2 | timewindow <Entity timewindow> |

| oth_heinz_1 | timewindow <Entity timewindow> |

| oth_heinz_2 | timewindow <Entity timewindow> |

| oth_andrej_1 | timewindow <Entity timewindow> |

| oth_andrej_2 | timewindow <Entity timewindow> |

| oth_marko_1 | timewindow <Entity timewindow> |

| oth_marko_2 | timewindow <Entity timewindow> |

| oth_william_1 | timewindow <Entity timewindow> |

| oth_william_2 | timewindow <Entity timewindow> |

| oth_harris_1 | timewindow <Entity timewindow> |

| oth_harris_2 | timewindow <Entity timewindow> |

| oth_helmut_1 | timewindow <Entity timewindow> |

| oth_helmut_2 | timewindow <Entity timewindow> |

| Irena_11 | timewindow <Entity timewindow> |

| Irena_21 | timewindow <Entity timewindow> |

| ewa_11 | timewindow <Entity timewindow> |

| ewa_21 | timewindow <Entity timewindow> |

| heinz_11 | timewindow <Entity timewindow> |

| heinz_21 | timewindow <Entity timewindow> |

| andrej_11 | timewindow <Entity timewindow> |

| andrej_21 | timewindow <Entity timewindow> |

| marko_11 | timewindow <Entity timewindow> |

| marko_21 | timewindow <Entity timewindow> |

| william_11 | timewindow <Entity timewindow> |

| william_21 | timewindow <Entity timewindow> |

| harris_11 | timewindow <Entity timewindow> |

| harris_21 | timewindow <Entity timewindow> |

| helmut_11 | timewindow <Entity timewindow> |

| helmut_21 | timewindow <Entity timewindow> |

| oth_Irena_11 | timewindow <Entity timewindow> |

| oth_Irena_21 | timewindow <Entity timewindow> |

| oth_ewa_11 | timewindow <Entity timewindow> |

| oth_ewa_21 | timewindow <Entity timewindow> |

| oth_heinz_11 | timewindow <Entity timewindow> |

| oth_heinz_21 | timewindow <Entity timewindow> |

| oth_andrej_11 | timewindow <Entity timewindow> |

| oth_andrej_21 | timewindow <Entity timewindow> |

| oth_marko_11 | timewindow <Entity timewindow> |

| oth_marko_21 | timewindow <Entity timewindow> |

| oth_william_11 | timewindow <Entity timewindow> |

| oth_william_21 | timewindow <Entity timewindow> |

| oth_harris_11 | timewindow <Entity timewindow> |

| oth_harris_21 | timewindow <Entity timewindow> |

| oth_helmut_11 | timewindow <Entity timewindow> |

| oth_helmut_21 | timewindow <Entity timewindow> |

| Irena_1w | timewindow <Entity timewindow> |

| Irena_2w | timewindow <Entity timewindow> |

| ewa_1w | timewindow <Entity timewindow> |

| ewa_2w | timewindow <Entity timewindow> |

| heinz_1w | timewindow <Entity timewindow> |

| heinz_2w | timewindow <Entity timewindow> |

| andrej_1w | timewindow <Entity timewindow> |

| andrej_2w | timewindow <Entity timewindow> |

| marko_1w | timewindow <Entity timewindow> |

| marko_2w | timewindow <Entity timewindow> |

| william_1w | timewindow <Entity timewindow> |

| william_2w | timewindow <Entity timewindow> |

| harris_1w | timewindow <Entity timewindow> |

| harris_2w | timewindow <Entity timewindow> |

| helmut_1w | timewindow <Entity timewindow> |

| helmut_2w | timewindow <Entity timewindow> |

| oth_Irena_1w | timewindow <Entity timewindow> |

| oth_Irena_2w | timewindow <Entity timewindow> |

| oth_ewa_1w | timewindow <Entity timewindow> |

| oth_ewa_2w | timewindow <Entity timewindow> |

| oth_heinz_1w | timewindow <Entity timewindow> |

| oth_heinz_2w | timewindow <Entity timewindow> |

| oth_andrej_1w | timewindow <Entity timewindow> |

| oth_andrej_2w | timewindow <Entity timewindow> |

| oth_marko_1w | timewindow <Entity timewindow> |

| oth_marko_2w | timewindow <Entity timewindow> |

| oth_william_1w | timewindow <Entity timewindow> |

| oth_william_2w | timewindow <Entity timewindow> |

| oth_harris_1w | timewindow <Entity timewindow> |

| oth_harris_2w | timewindow <Entity timewindow> |

| oth_helmut_1w | timewindow <Entity timewindow> |

| oth_helmut_2w | timewindow <Entity timewindow> |

Aliases | |

| clk5x | CLK |

Detailed Description

CTP logic.

The logic consists of applying seperate time windows to modules on side A and side C to capture particles travelling from one side to the other (particularly useful for early single-beam running) as well as multiplicity information per side. The time-window logic based on delta_t_ac_top.one_to_one, the rest is simple counting.

It is intended to be run at the nominal bunch clock frequency of 40 MHz but could be sped up if needed to decrease absolute latency (= ? clock cycles). Cut boundaries are settable at compile-time via generics.

Definition at line 146 of file ctp_logic.vhd.

Member Data Documentation

timewindow [Component] |

The documentation for this class was generated from the following file: