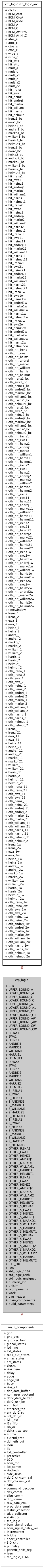

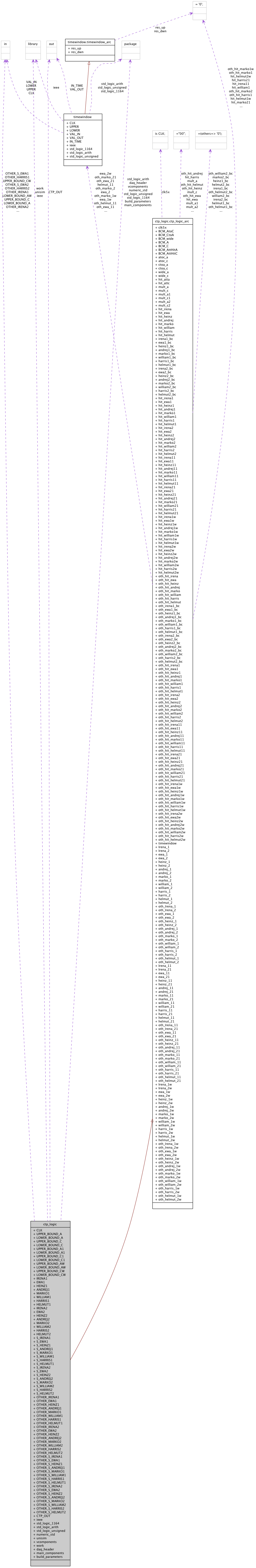

ctp_logic Entity Reference

Top module of logic for CTP bits. More...

Architectures | |

| ctp_logic_arc | Architecture |

| CTP logic. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| unisim | |

| Library with Xilinx primitives. | |

| work | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

| numeric_std | |

| arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file | |

| vcomponents | |

| Header with Xilinx primitives. | |

| daq_header | Package <daq_header> |

| main_components | Package <main_components> |

| build_parameters | Package <build_parameters> |

Ports | |

| CLK | in std_logic |

| Clock. | |

| UPPER_BOUND_A | in std_logic_vector ( 5 downto 0 ) := " 101110 " |

| Time win upper side A, A to C. | |

| LOWER_BOUND_A | in std_logic_vector ( 5 downto 0 ) := " 010000 " |

| Time win lower side A, A to C. | |

| UPPER_BOUND_C | in std_logic_vector ( 5 downto 0 ) := " 101110 " |

| Time win upper side C, A to C. | |

| LOWER_BOUND_C | in std_logic_vector ( 5 downto 0 ) := " 010000 " |

| Time win lower side C, A to C. | |

| UPPER_BOUND_A1 | in std_logic_vector ( 5 downto 0 ) := " 101110 " |

| Time win upper side A, C to A. | |

| LOWER_BOUND_A1 | in std_logic_vector ( 5 downto 0 ) := " 010000 " |

| Time win lower side A, C to A. | |

| UPPER_BOUND_C1 | in std_logic_vector ( 5 downto 0 ) := " 101110 " |

| Time win upper side C, C to A. | |

| LOWER_BOUND_C1 | in std_logic_vector ( 5 downto 0 ) := " 010000 " |

| Time win lower side C, C to A. | |

| UPPER_BOUND_AW | in std_logic_vector ( 5 downto 0 ) := " 111111 " |

| Time win upper side A, wide. | |

| LOWER_BOUND_AW | in std_logic_vector ( 5 downto 0 ) := " 000001 " |

| Time win lower side A, wide. | |

| UPPER_BOUND_CW | in std_logic_vector ( 5 downto 0 ) := " 111111 " |

| Time win upper side C, wide. | |

| LOWER_BOUND_CW | in std_logic_vector ( 5 downto 0 ) := " 000001 " |

| Time win lower side C, wide. | |

| IRENA1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| EWA1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| HEINZ1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| ANDREJ1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| MARKO1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| WILLIAM1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| HARRIS1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| HELMUT1 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| IRENA2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| EWA2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| HEINZ2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| ANDREJ2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| MARKO2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| WILLIAM2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| HARRIS2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| HELMUT2 | in std_logic_vector ( 7 downto 0 ) |

| 1 CH data | |

| S_IRENA1 | in std_logic |

| 1 CH status bit | |

| S_EWA1 | in std_logic |

| 1 CH status bit | |

| S_HEINZ1 | in std_logic |

| 1 CH status bit | |

| S_ANDREJ1 | in std_logic |

| 1 CH status bit | |

| S_MARKO1 | in std_logic |

| 1 CH status bit | |

| S_WILLIAM1 | in std_logic |

| 1 CH status bit | |

| S_HARRIS1 | in std_logic |

| 1 CH status bit | |

| S_HELMUT1 | in std_logic |

| 1 CH status bit | |

| S_IRENA2 | in std_logic |

| 1 CH status bit | |

| S_EWA2 | in std_logic |

| 1 CH status bit | |

| S_HEINZ2 | in std_logic |

| 1 CH status bit | |

| S_ANDREJ2 | in std_logic |

| 1 CH status bit | |

| S_MARKO2 | in std_logic |

| 1 CH status bit | |

| S_WILLIAM2 | in std_logic |

| 1 CH status bit | |

| S_HARRIS2 | in std_logic |

| 1 CH status bit | |

| S_HELMUT2 | in std_logic |

| 1 CH status bit | |

| OTHER_IRENA1 | in std_logic_vector ( 7 downto 0 ) := " 00000000 " |

| 1 CH data from other ROD | |

| OTHER_EWA1 | in std_logic_vector ( 7 downto 0 ) := " 00000000 " |

| 1 CH data from other ROD | |

| OTHER_HEINZ1 | in std_logic_vector ( 7 downto 0 ) := " 00000000 " |

| 1 CH data from other ROD | |

| OTHER_ANDREJ1 | in std_logic_vector ( 7 downto 0 ) := " 00000000 " |

| 1 CH data from other ROD | |

| OTHER_MARKO1 | in std_logic_vector ( 7 downto 0 ) := " 00000000 " |

| 1 CH data from other ROD | |

| OTHER_WILLIAM1 | in std_logic_vector ( 7 downto 0 ) := " 00000000 " |

| 1 CH data from other ROD | |

| OTHER_HARRIS1 | in std_logic_vector ( 7 downto 0 ) := " 00000000 " |

| 1 CH data from other ROD | |

| OTHER_HELMUT1 | in std_logic_vector ( 7 downto 0 ) := " 00000000 " |

| 1 CH data from other ROD | |

| OTHER_IRENA2 | in std_logic_vector ( 7 downto 0 ) := " 00000000 " |

| 1 CH data from other ROD | |

| OTHER_EWA2 | in std_logic_vector ( 7 downto 0 ) := " 00000000 " |

| 1 CH data from other ROD | |

| OTHER_HEINZ2 | in std_logic_vector ( 7 downto 0 ) := " 00000000 " |

| 1 CH data from other ROD | |

| OTHER_ANDREJ2 | in std_logic_vector ( 7 downto 0 ) := " 00000000 " |

| 1 CH data from other ROD | |

| OTHER_MARKO2 | in std_logic_vector ( 7 downto 0 ) := " 00000000 " |

| 1 CH data from other ROD | |

| OTHER_WILLIAM2 | in std_logic_vector ( 7 downto 0 ) := " 00000000 " |

| 1 CH data from other ROD | |

| OTHER_HARRIS2 | in std_logic_vector ( 7 downto 0 ) := " 00000000 " |

| 1 CH data from other ROD | |

| OTHER_HELMUT2 | in std_logic_vector ( 7 downto 0 ) := " 00000000 " |

| 1 CH data from other ROD | |

| OTHER_S_IRENA1 | in std_logic := ' 0 ' |

| 1 CH status bit from other ROD | |

| OTHER_S_EWA1 | in std_logic := ' 0 ' |

| 1 CH status bit from other ROD | |

| OTHER_S_HEINZ1 | in std_logic := ' 0 ' |

| 1 CH status bit from other ROD | |

| OTHER_S_ANDREJ1 | in std_logic := ' 0 ' |

| 1 CH status bit from other ROD | |

| OTHER_S_MARKO1 | in std_logic := ' 0 ' |

| 1 CH status bit from other ROD | |

| OTHER_S_WILLIAM1 | in std_logic := ' 0 ' |

| 1 CH status bit from other ROD | |

| OTHER_S_HARRIS1 | in std_logic := ' 0 ' |

| 1 CH status bit from other ROD | |

| OTHER_S_HELMUT1 | in std_logic := ' 0 ' |

| 1 CH status bit from other ROD | |

| OTHER_S_IRENA2 | in std_logic := ' 0 ' |

| 1 CH status bit from other ROD | |

| OTHER_S_EWA2 | in std_logic := ' 0 ' |

| 1 CH status bit from other ROD | |

| OTHER_S_HEINZ2 | in std_logic := ' 0 ' |

| 1 CH status bit from other ROD | |

| OTHER_S_ANDREJ2 | in std_logic := ' 0 ' |

| 1 CH status bit from other ROD | |

| OTHER_S_MARKO2 | in std_logic := ' 0 ' |

| 1 CH status bit from other ROD | |

| OTHER_S_WILLIAM2 | in std_logic := ' 0 ' |

| 1 CH status bit from other ROD | |

| OTHER_S_HARRIS2 | in std_logic := ' 0 ' |

| 1 CH status bit from other ROD | |

| OTHER_S_HELMUT2 | in std_logic := ' 0 ' |

| 1 CH status bit from other ROD | |

| CTP_OUT | out std_logic_vector ( 9 downto 1 ) |

| CTP Output Bits. | |

Detailed Description

Top module of logic for CTP bits.

This entity produces 9 bits output for the ATLAS Central Trigger Processor (CTP) which forms an decision on wether to accept or rejcect a particular bunch crossing for further data processing and analysis.

The specification of the 9 bits can be found at: BcmTriggerWiki

It is intended to be run at the nominal bunch clock frequency of 40 MHz but could be sped up if needed to decrease absolute latency (= 2 clock cycles). Cut boundaries are settable at compile-time via generics.

Definition at line 53 of file ctp_logic.vhd.

Member Data Documentation

ANDREJ1 in std_logic_vector ( 7 downto 0 ) [Port] |

ANDREJ2 in std_logic_vector ( 7 downto 0 ) [Port] |

CLK in std_logic [Port] |

CTP_OUT out std_logic_vector ( 9 downto 1 ) [Port] |

EWA1 in std_logic_vector ( 7 downto 0 ) [Port] |

EWA2 in std_logic_vector ( 7 downto 0 ) [Port] |

HARRIS1 in std_logic_vector ( 7 downto 0 ) [Port] |

HARRIS2 in std_logic_vector ( 7 downto 0 ) [Port] |

HEINZ1 in std_logic_vector ( 7 downto 0 ) [Port] |

HEINZ2 in std_logic_vector ( 7 downto 0 ) [Port] |

HELMUT1 in std_logic_vector ( 7 downto 0 ) [Port] |

HELMUT2 in std_logic_vector ( 7 downto 0 ) [Port] |

ieee library [Library] |

standard IEEE library

Reimplemented in main_components.

Definition at line 25 of file ctp_logic.vhd.

IRENA1 in std_logic_vector ( 7 downto 0 ) [Port] |

IRENA2 in std_logic_vector ( 7 downto 0 ) [Port] |

LOWER_BOUND_A in std_logic_vector ( 5 downto 0 ) := " 010000 " [Port] |

LOWER_BOUND_A1 in std_logic_vector ( 5 downto 0 ) := " 010000 " [Port] |

LOWER_BOUND_AW in std_logic_vector ( 5 downto 0 ) := " 000001 " [Port] |

LOWER_BOUND_C in std_logic_vector ( 5 downto 0 ) := " 010000 " [Port] |

LOWER_BOUND_C1 in std_logic_vector ( 5 downto 0 ) := " 010000 " [Port] |

LOWER_BOUND_CW in std_logic_vector ( 5 downto 0 ) := " 000001 " [Port] |

MARKO1 in std_logic_vector ( 7 downto 0 ) [Port] |

MARKO2 in std_logic_vector ( 7 downto 0 ) [Port] |

numeric_std package [Package] |

arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file

Definition at line 33 of file ctp_logic.vhd.

OTHER_ANDREJ1 in std_logic_vector ( 7 downto 0 ) := " 00000000 " [Port] |

OTHER_ANDREJ2 in std_logic_vector ( 7 downto 0 ) := " 00000000 " [Port] |

OTHER_EWA1 in std_logic_vector ( 7 downto 0 ) := " 00000000 " [Port] |

OTHER_EWA2 in std_logic_vector ( 7 downto 0 ) := " 00000000 " [Port] |

OTHER_HARRIS1 in std_logic_vector ( 7 downto 0 ) := " 00000000 " [Port] |

OTHER_HARRIS2 in std_logic_vector ( 7 downto 0 ) := " 00000000 " [Port] |

OTHER_HEINZ1 in std_logic_vector ( 7 downto 0 ) := " 00000000 " [Port] |

OTHER_HEINZ2 in std_logic_vector ( 7 downto 0 ) := " 00000000 " [Port] |

OTHER_HELMUT1 in std_logic_vector ( 7 downto 0 ) := " 00000000 " [Port] |

OTHER_HELMUT2 in std_logic_vector ( 7 downto 0 ) := " 00000000 " [Port] |

OTHER_IRENA1 in std_logic_vector ( 7 downto 0 ) := " 00000000 " [Port] |

OTHER_IRENA2 in std_logic_vector ( 7 downto 0 ) := " 00000000 " [Port] |

OTHER_MARKO1 in std_logic_vector ( 7 downto 0 ) := " 00000000 " [Port] |

OTHER_MARKO2 in std_logic_vector ( 7 downto 0 ) := " 00000000 " [Port] |

OTHER_S_ANDREJ1 in std_logic := ' 0 ' [Port] |

OTHER_S_ANDREJ2 in std_logic := ' 0 ' [Port] |

OTHER_S_EWA1 in std_logic := ' 0 ' [Port] |

OTHER_S_EWA2 in std_logic := ' 0 ' [Port] |

OTHER_S_HARRIS1 in std_logic := ' 0 ' [Port] |

OTHER_S_HARRIS2 in std_logic := ' 0 ' [Port] |

OTHER_S_HEINZ1 in std_logic := ' 0 ' [Port] |

OTHER_S_HEINZ2 in std_logic := ' 0 ' [Port] |

OTHER_S_HELMUT1 in std_logic := ' 0 ' [Port] |

OTHER_S_HELMUT2 in std_logic := ' 0 ' [Port] |

OTHER_S_IRENA1 in std_logic := ' 0 ' [Port] |

OTHER_S_IRENA2 in std_logic := ' 0 ' [Port] |

OTHER_S_MARKO1 in std_logic := ' 0 ' [Port] |

OTHER_S_MARKO2 in std_logic := ' 0 ' [Port] |

OTHER_S_WILLIAM1 in std_logic := ' 0 ' [Port] |

OTHER_S_WILLIAM2 in std_logic := ' 0 ' [Port] |

OTHER_WILLIAM1 in std_logic_vector ( 7 downto 0 ) := " 00000000 " [Port] |

OTHER_WILLIAM2 in std_logic_vector ( 7 downto 0 ) := " 00000000 " [Port] |

S_ANDREJ1 in std_logic [Port] |

S_ANDREJ2 in std_logic [Port] |

S_EWA1 in std_logic [Port] |

S_EWA2 in std_logic [Port] |

S_HARRIS1 in std_logic [Port] |

S_HARRIS2 in std_logic [Port] |

S_HEINZ1 in std_logic [Port] |

S_HEINZ2 in std_logic [Port] |

S_HELMUT1 in std_logic [Port] |

S_HELMUT2 in std_logic [Port] |

S_IRENA1 in std_logic [Port] |

S_IRENA2 in std_logic [Port] |

S_MARKO1 in std_logic [Port] |

S_MARKO2 in std_logic [Port] |

S_WILLIAM1 in std_logic [Port] |

S_WILLIAM2 in std_logic [Port] |

std_logic_1164 package [Package] |

std_logic definitions, see file

Reimplemented in main_components.

Definition at line 27 of file ctp_logic.vhd.

std_logic_arith package [Package] |

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 31 of file ctp_logic.vhd.

unisim library [Library] |

UPPER_BOUND_A in std_logic_vector ( 5 downto 0 ) := " 101110 " [Port] |

UPPER_BOUND_A1 in std_logic_vector ( 5 downto 0 ) := " 101110 " [Port] |

UPPER_BOUND_AW in std_logic_vector ( 5 downto 0 ) := " 111111 " [Port] |

UPPER_BOUND_C in std_logic_vector ( 5 downto 0 ) := " 101110 " [Port] |

UPPER_BOUND_C1 in std_logic_vector ( 5 downto 0 ) := " 101110 " [Port] |

UPPER_BOUND_CW in std_logic_vector ( 5 downto 0 ) := " 111111 " [Port] |

vcomponents package [Package] |

WILLIAM1 in std_logic_vector ( 7 downto 0 ) [Port] |

WILLIAM2 in std_logic_vector ( 7 downto 0 ) [Port] |

The documentation for this class was generated from the following file: