timewindow Entity Reference

Apply time window to 1 channel. More...

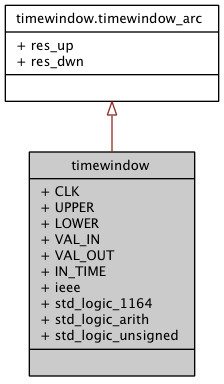

Inheritance diagram for timewindow:

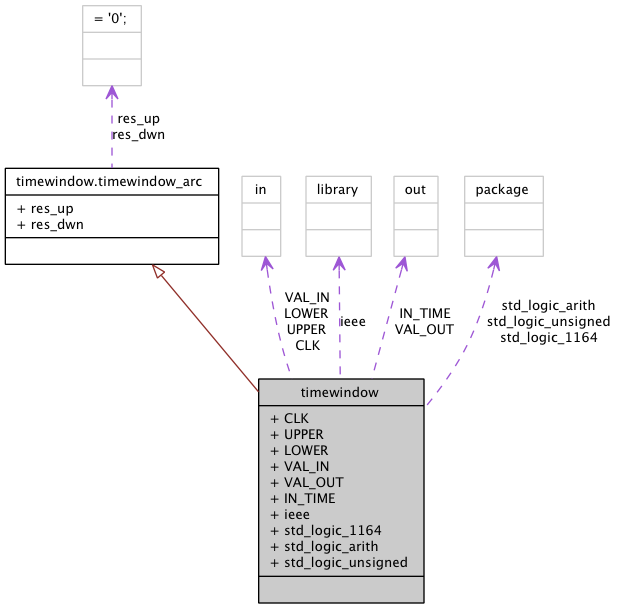

Collaboration diagram for timewindow:

Architectures | |

| timewindow_arc | Architecture |

| Apply time window to 1 channel. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

Ports | |

| CLK | in std_logic |

| clock | |

| UPPER | in std_logic_vector ( 5 downto 0 ) := " 101110 " |

| Upper boundary. | |

| LOWER | in std_logic_vector ( 5 downto 0 ) := " 010000 " |

| Lower boundary. | |

| VAL_IN | in std_logic_vector ( 5 downto 0 ) |

| input | |

| VAL_OUT | out std_logic_vector ( 5 downto 0 ) |

| feedthrough input | |

| IN_TIME | out std_logic |

| in-time flag | |

Detailed Description

Apply time window to 1 channel.

Applies a time window (boundaries inherited from parent entity) to the leading edge data of 1 channel. Passes on the input value and sets the IN_TIME bit high if the input lies within the time window.

Definition at line 37 of file timewindow.vhd.

Member Data Documentation

CLK in std_logic [Port] |

ieee library [Library] |

IN_TIME out std_logic [Port] |

LOWER in std_logic_vector ( 5 downto 0 ) := " 010000 " [Port] |

std_logic_1164 package [Package] |

std_logic_arith package [Package] |

arithmetic operations on std_logic datatypes, see file

Definition at line 28 of file timewindow.vhd.

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 30 of file timewindow.vhd.

UPPER in std_logic_vector ( 5 downto 0 ) := " 101110 " [Port] |

VAL_IN in std_logic_vector ( 5 downto 0 ) [Port] |

VAL_OUT out std_logic_vector ( 5 downto 0 ) [Port] |

The documentation for this class was generated from the following file: