cal.cal_arc Architecture Reference

Calculate pulse widths. More...

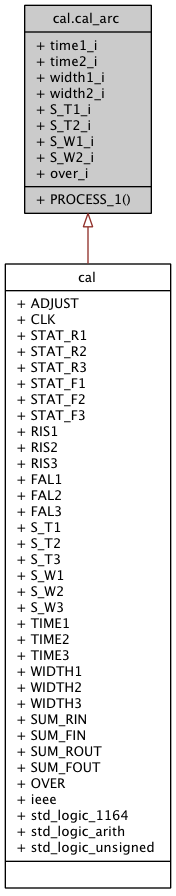

Inheritance diagram for cal.cal_arc:

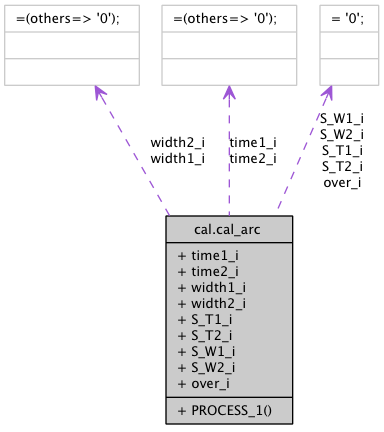

Collaboration diagram for cal.cal_arc:

Processes | |

| PROCESS_1 | ( CLK ) |

| calculation | |

Signals | |

| time1_i | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| time2_i | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

| width1_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| width2_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| S_T1_i | std_logic := ' 0 ' |

| S_T2_i | std_logic := ' 0 ' |

| S_W1_i | std_logic := ' 0 ' |

| S_W2_i | std_logic := ' 0 ' |

| over_i | std_logic := ' 0 ' |

Detailed Description

Calculate pulse widths.Definition at line 73 of file cal.vhd.

Member Function Documentation

| PROCESS_1 | ( CLK ) |

calculation

Definition at line 107 of file cal.vhd.

00107 process (CLK) 00108 begin 00109 00110 if CLK'event and CLK = '1' then 00111 00112 SUM_ROUT <= SUM_RIN; 00113 SUM_FOUT <= SUM_FIN; 00114 00115 over_i <= '0'; 00116 00117 if STAT_R1 = '1' then 00118 time1_i <= RIS1; 00119 S_T1_i <= '1'; 00120 else 00121 time1_i <= (others => '0'); 00122 S_T1_i <= '0'; 00123 end if; 00124 if (STAT_F1 and STAT_R1) = '1' then 00125 if FAL1 < RIS1 then 00126 if RIS1 <= 32 then 00127 width1_i <= "00" & (32 - RIS1 + FAL1); 00128 else 00129 width1_i <= "00" & (64 - RIS1 + FAL1); 00130 end if; 00131 else 00132 width1_i <= "00" & FAL1 - RIS1; 00133 end if; 00134 S_W1_i <= '1'; 00135 else 00136 if STAT_R1 = '1' then 00137 width1_i <= "00" & (64 - RIS1); 00138 S_W1_i <= '1'; 00139 over_i <= '1'; 00140 else 00141 width1_i <= (others => '0'); 00142 S_W1_i <= '0'; 00143 end if; 00144 end if; 00145 00146 if STAT_R2 = '1' then 00147 time2_i <= RIS2; 00148 S_T2_i <= '1'; 00149 else 00150 time2_i <= (others => '0'); 00151 S_T2_i <= '0'; 00152 end if; 00153 if (STAT_F2 and STAT_R2) = '1' then 00154 if FAL2 < RIS2 then 00155 if RIS2 <= 32 then 00156 width2_i <= "00" & (32 - RIS2 + FAL2); 00157 else 00158 width2_i <= "00" & (64 - RIS2 + FAL2); 00159 end if; 00160 else 00161 width2_i <= "00" & FAL2 - RIS2; 00162 end if; 00163 S_W2_i <= '1'; 00164 else 00165 if STAT_R2 = '1' then 00166 width2_i <= "00" & (64 - RIS2); 00167 S_W2_i <= '1'; 00168 over_i <= '1'; 00169 else 00170 width2_i <= (others => '0'); 00171 S_W2_i <= '0'; 00172 end if; 00173 end if; 00174 00175 -- if STAT_R3 = '1' then 00176 -- time3_i <= ("00" & RIS3); 00177 -- S_T3_i <= '1'; 00178 -- else 00179 -- time3_i <= (others => '0'); 00180 -- S_T3_i <= '0'; 00181 -- end if; 00182 -- if STAT_F3 = '1' then 00183 -- if FAL3 < RIS3 then 00184 -- width3_i <= "00" & (32 - RIS3 + FAL3); 00185 -- else 00186 -- width3_i <= "00" & FAL3 - RIS3; 00187 -- end if; 00188 -- S_W3_i <= '1'; 00189 -- else 00190 -- if STAT_R3 = '1' then 00191 -- width3_i <= "00" & (64 - RIS3); 00192 -- S_W3_i <= '1'; 00193 -- over_i <= '1'; 00194 -- else 00195 -- width3_i <= (others => '0'); 00196 -- S_W3_i <= '0'; 00197 -- end if; 00198 -- end if; 00199 00200 end if; 00201 end process;

The documentation for this class was generated from the following file: