bcm_rod Entity Reference

ROD formatter top module. More...

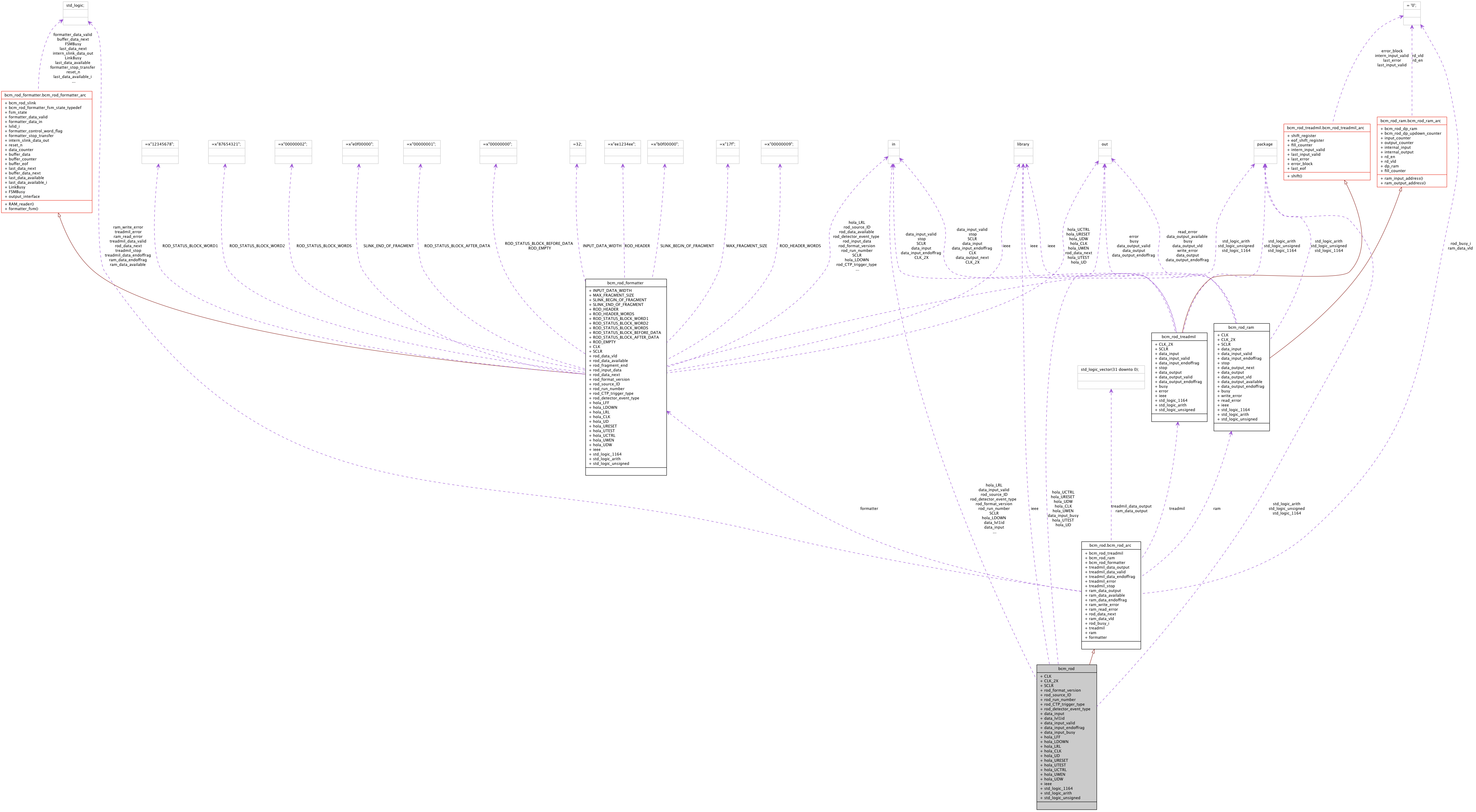

Inheritance diagram for bcm_rod:

Collaboration diagram for bcm_rod:

Architectures | |

| bcm_rod_arc | Architecture |

| structural description of ROD formatter More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

Ports | |

| CLK | in std_logic |

| 40 MHz clock | |

| CLK_2X | in std_logic |

| 80 MHz clock | |

| SCLR | in std_logic |

| synchronous clear (reset) signal | |

| rod_format_version | in std_logic_vector ( 31 downto 0 ) := x " 03010001 " |

| ROD format version. | |

| rod_source_ID | in std_logic_vector ( 31 downto 0 ) := x " 00810000 " |

| source ID | |

| rod_run_number | in std_logic_vector ( 31 downto 0 ) := x " 7fffffff " |

| run number | |

| rod_CTP_trigger_type | in std_logic_vector ( 31 downto 0 ) := x " 00000011 " |

| Level-1 trigger type. | |

| rod_detector_event_type | in std_logic_vector ( 31 downto 0 ) := x " 000000dd " |

| detector event type | |

| data_input | in std_logic_vector ( 191 downto 0 ) |

| input data, full pkt | |

| data_lvl1id | in std_logic_vector ( 31 downto 0 ) |

| Level-1 ID. | |

| data_input_valid | in std_logic |

| data valid flag | |

| data_input_endoffrag | in std_logic |

| end of fragment flag | |

| data_input_busy | out std_logic |

| ROD formatter busy flag. | |

| hola_LFF | in std_logic |

| SLINK full flag (LFF) !!! ACTIVE LOW !!! | |

| hola_LDOWN | in std_logic |

| SLINK down (LDOWN) !!! ACTIVE LOW !!! | |

| hola_LRL | in std_logic_vector ( 3 downto 0 ) |

| SLINK return data lines (LRL) !!! NOT USED !!! | |

| hola_CLK | out std_logic |

| SLINK clock (UCLK). | |

| hola_UD | out std_logic_vector ( 31 downto 0 ) |

| SLINK data output (UD). | |

| hola_URESET | out std_logic |

| SLINK reset link (URESET) !!! ACTIVE LOW !!! | |

| hola_UTEST | out std_logic |

| SLINK test line (UTEST) !!! ACTIVE LOW !!! | |

| hola_UCTRL | out std_logic |

| SLINK control word flag (UCTRL) !!! ACTIVE LOW !!! | |

| hola_UWEN | out std_logic |

| SLINK write enable (UWEN) !!! ACTIVE LOW !!! | |

| hola_UDW | out std_logic_vector ( 1 downto 0 ) := " 00 " |

| SLINK data width (UDW) "00"=32-bit, "01"=16-bit, "10"=8-bit, "11"=reserved. | |

Detailed Description

ROD formatter top module.

This entity is the top module of the ROD formatter. All submodules are connected here.

Detailed description of the ROD formatter is available here.

Definition at line 37 of file bcm_rod.vhd.

Member Data Documentation

CLK in std_logic [Port] |

CLK_2X in std_logic [Port] |

data_input in std_logic_vector ( 191 downto 0 ) [Port] |

data_input_busy out std_logic [Port] |

data_input_endoffrag in std_logic [Port] |

data_input_valid in std_logic [Port] |

data_lvl1id in std_logic_vector ( 31 downto 0 ) [Port] |

hola_CLK out std_logic [Port] |

hola_LDOWN in std_logic [Port] |

hola_LFF in std_logic [Port] |

hola_LRL in std_logic_vector ( 3 downto 0 ) [Port] |

hola_UCTRL out std_logic [Port] |

hola_UD out std_logic_vector ( 31 downto 0 ) [Port] |

hola_UDW out std_logic_vector ( 1 downto 0 ) := " 00 " [Port] |

SLINK data width (UDW) "00"=32-bit, "01"=16-bit, "10"=8-bit, "11"=reserved.

Definition at line 65 of file bcm_rod.vhd.

hola_URESET out std_logic [Port] |

hola_UTEST out std_logic [Port] |

hola_UWEN out std_logic [Port] |

ieee library [Library] |

rod_CTP_trigger_type in std_logic_vector ( 31 downto 0 ) := x " 00000011 " [Port] |

rod_detector_event_type in std_logic_vector ( 31 downto 0 ) := x " 000000dd " [Port] |

rod_format_version in std_logic_vector ( 31 downto 0 ) := x " 03010001 " [Port] |

rod_run_number in std_logic_vector ( 31 downto 0 ) := x " 7fffffff " [Port] |

rod_source_ID in std_logic_vector ( 31 downto 0 ) := x " 00810000 " [Port] |

SCLR in std_logic [Port] |

std_logic_1164 package [Package] |

std_logic definitions, see file

Reimplemented in main_components.

Definition at line 26 of file bcm_rod.vhd.

std_logic_arith package [Package] |

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 30 of file bcm_rod.vhd.

The documentation for this class was generated from the following file: