statistics.statistics_arc Architecture Reference

Determines minimum, maximum and average of a series of input values. More...

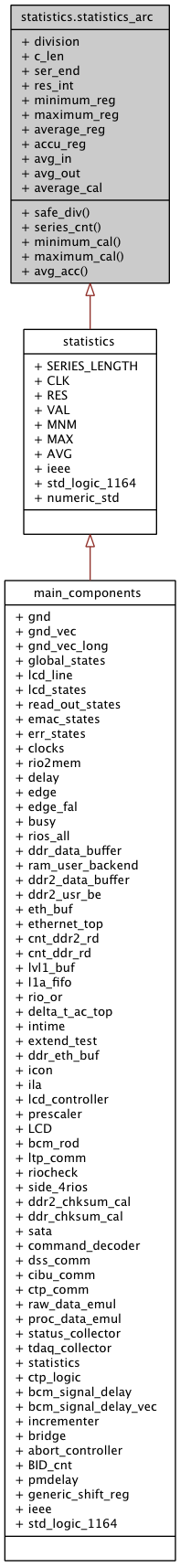

Inheritance diagram for statistics.statistics_arc:

Collaboration diagram for statistics.statistics_arc:

Functions | |

| integer | safe_div ( A: in integer ) |

| make sure divisor is a power of two | |

Processes | |

| series_cnt | ( CLK ) |

| count length of input series | |

| minimum_cal | ( CLK ) |

| determine minimum of series | |

| maximum_cal | ( CLK ) |

| determine maximum of series | |

| avg_acc | ( CLK ) |

Components | |

| division | <Entity division> |

| Division. | |

Constants | |

| c_len | integer := safe_div ( SERIES_LENGTH ) |

| divisor | |

Signals | |

| ser_end | std_logic := ' 0 ' |

| res_int | std_logic := ' 0 ' |

| minimum_reg | unsigned ( 15 downto 0 ) := ( others = > ' 0 ' ) |

| maximum_reg | unsigned ( 15 downto 0 ) := ( others = > ' 0 ' ) |

| average_reg | unsigned ( 15 downto 0 ) := ( others = > ' 0 ' ) |

| accu_reg | unsigned ( 15 downto 0 ) := ( others = > ' 0 ' ) |

| avg_in | unsigned ( 15 downto 0 ) := ( others = > ' 0 ' ) |

| avg_out | unsigned ( 15 downto 0 ) := ( others = > ' 0 ' ) |

Component Instantiations | |

| average_cal | division <Entity division> |

Detailed Description

Determines minimum, maximum and average of a series of input values.This entity determines the minimum & maximum value as well as the average of a series of input values. The series length is specified via a generic that needs to be a power of two. A function makes sure this is garantueed.

Definition at line 54 of file statistics.vhd.

Member Function Documentation

| maximum_cal | ( CLK ) |

determine maximum of series

Definition at line 143 of file statistics.vhd.

00143 maximum_cal : process (CLK) 00144 begin -- process minimum 00145 if CLK'event and CLK = '1' then -- rising clock edge 00146 if res_int = '1' then 00147 maximum_reg <= unsigned(VAL); 00148 elsif unsigned(VAL) > maximum_reg then 00149 maximum_reg <= unsigned(VAL); 00150 else 00151 maximum_reg <= maximum_reg; 00152 end if; 00153 end if; 00154 end process maximum_cal;

| minimum_cal | ( CLK ) |

determine minimum of series

Definition at line 127 of file statistics.vhd.

00127 minimum_cal : process (CLK) 00128 begin -- process minimum 00129 if CLK'event and CLK = '1' then -- rising clock edge 00130 if res_int = '1' then 00131 minimum_reg <= unsigned(VAL); 00132 elsif unsigned(VAL) <= minimum_reg then 00133 minimum_reg <= unsigned(VAL); 00134 else 00135 minimum_reg <= minimum_reg; 00136 end if; 00137 end if; 00138 end process minimum_cal;

| integer safe_div | ( A in integer ) |

make sure divisor is a power of two

Definition at line 68 of file statistics.vhd.

00068 function safe_div ( 00069 A : integer) 00070 return integer is 00071 variable Ai : integer; 00072 variable ret : integer := 2; 00073 begin -- safe_div 00074 Ai := A; 00075 while 0 < 1 loop 00076 if Ai < 2 then 00077 ret := 2; 00078 exit; 00079 else 00080 if Ai mod 2 /= 0 then 00081 Ai := Ai - 1; 00082 else 00083 ret := Ai; 00084 exit; 00085 end if; 00086 end if; 00087 end loop; 00088 return ret; 00089 end safe_div;

| series_cnt | ( CLK ) |

count length of input series

Definition at line 108 of file statistics.vhd.

00108 series_cnt : process (CLK) 00109 variable cnt : integer := 0; 00110 begin -- process series_cnt 00111 if CLK'event and CLK = '1' then -- rising clock edge 00112 if RES = '1' then 00113 cnt := 0; 00114 ser_end <= '0'; 00115 else 00116 ser_end <= '0'; 00117 cnt := cnt + 1; 00118 if cnt = c_len then 00119 ser_end <= '1'; 00120 cnt := 0; 00121 end if; 00122 end if; 00123 end if; 00124 end process series_cnt;

Member Data Documentation

average_cal division [Component Instantiation] |

Division for average

Definition at line 177 of file statistics.vhd.

division [Component] |

The documentation for this class was generated from the following file: