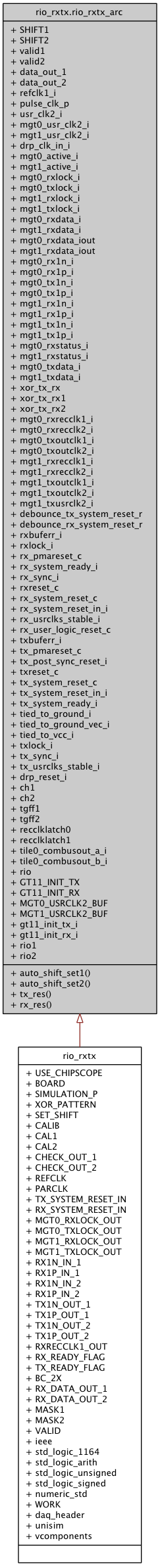

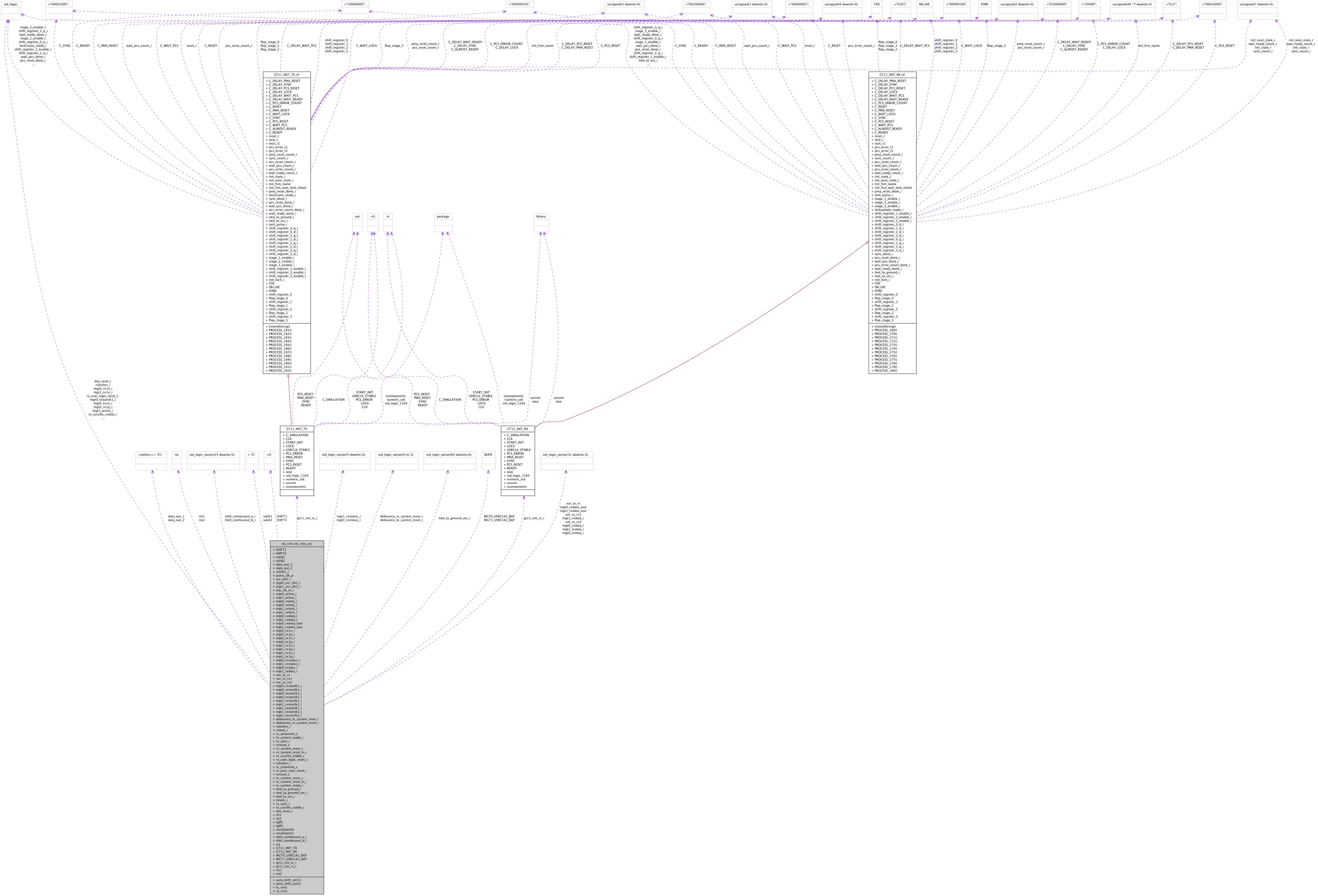

rio_rxtx.rio_rxtx_arc Architecture Reference

DAQ-RocketIO wrapper and support logic. More...

Processes | |

| auto_shift_set1 | ( mgt0_usr_clk2_i ) |

| XOR pattern reco. | |

| auto_shift_set2 | ( mgt1_usr_clk2_i ) |

| XOR pattern reco. | |

| tx_res | ( drp_clk_in_i ) |

| Extend the TX_SYSTEM_RESET_IN signal using the DRP_CLK. | |

| rx_res | ( drp_clk_in_i ) |

| Extend the RX_SYSTEM_RESET_IN signal using the DRP_CLK. | |

Components | |

| rio | |

| RocketIO wrapper. | |

| GT11_INIT_TX | <Entity GT11_INIT_TX> |

| Init logic for TX. | |

| GT11_INIT_RX | <Entity GT11_INIT_RX> |

| Init logic for RX. | |

Signals | |

| SHIFT1 | integer range 0 to 7 := 0 |

| SHIFT2 | integer range 0 to 7 := 0 |

| valid1 | std_logic := ' 0 ' |

| valid2 | std_logic := ' 0 ' |

| data_out_1 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| data_out_2 | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| refclk1_i | std_logic |

| pulse_clk_p | std_logic |

| usr_clk2_i | std_logic |

| mgt0_usr_clk2_i | std_logic |

| mgt1_usr_clk2_i | std_logic |

| drp_clk_in_i | std_logic |

| mgt0_active_i | std_logic |

| mgt1_active_i | std_logic |

| mgt0_rxlock_i | std_logic |

| mgt0_txlock_i | std_logic |

| mgt1_rxlock_i | std_logic |

| mgt1_txlock_i | std_logic |

| mgt0_rxdata_i | std_logic_vector ( 31 downto 0 ) |

| mgt1_rxdata_i | std_logic_vector ( 31 downto 0 ) |

| mgt0_rxdata_iout | std_logic_vector ( 31 downto 0 ) |

| mgt1_rxdata_iout | std_logic_vector ( 31 downto 0 ) |

| mgt0_rx1n_i | std_logic |

| mgt0_rx1p_i | std_logic |

| mgt0_tx1n_i | std_logic |

| mgt0_tx1p_i | std_logic |

| mgt1_rx1n_i | std_logic |

| mgt1_rx1p_i | std_logic |

| mgt1_tx1n_i | std_logic |

| mgt1_tx1p_i | std_logic |

| mgt0_rxstatus_i | std_logic_vector ( 5 downto 0 ) |

| mgt1_rxstatus_i | std_logic_vector ( 5 downto 0 ) |

| mgt0_txdata_i | std_logic_vector ( 31 downto 0 ) |

| mgt1_txdata_i | std_logic_vector ( 31 downto 0 ) |

| xor_tx_rx | std_logic_vector ( 31 downto 0 ) |

| xor_tx_rx1 | std_logic_vector ( 31 downto 0 ) |

| xor_tx_rx2 | std_logic_vector ( 31 downto 0 ) |

| mgt0_rxrecclk1_i | std_logic |

| mgt0_rxrecclk2_i | std_logic |

| mgt0_txoutclk1_i | std_logic |

| mgt0_txoutclk2_i | std_logic |

| mgt1_rxrecclk1_i | std_logic |

| mgt1_rxrecclk2_i | std_logic |

| mgt1_txoutclk1_i | std_logic |

| mgt1_txoutclk2_i | std_logic |

| mgt1_txusrclk2_i | std_logic |

| debounce_tx_system_reset_r | std_logic_vector ( 0 to 3 ) |

| debounce_rx_system_reset_r | std_logic_vector ( 0 to 3 ) |

| rxbuferr_i | std_logic |

| rxlock_i | std_logic |

| rx_pmareset_c | std_logic |

| rx_system_ready_i | std_logic |

| rx_sync_i | std_logic |

| rxreset_c | std_logic |

| rx_system_reset_c | std_logic |

| rx_system_reset_in_i | std_logic |

| rx_usrclks_stable_i | std_logic |

| rx_user_logic_reset_c | std_logic |

| txbuferr_i | std_logic |

| tx_pmareset_c | std_logic |

| tx_post_sync_reset_i | std_logic |

| txreset_c | std_logic |

| tx_system_reset_c | std_logic |

| tx_system_reset_in_i | std_logic |

| tx_system_ready_i | std_logic |

| tied_to_ground_i | std_logic |

| tied_to_ground_vec_i | std_logic_vector ( 63 downto 0 ) |

| tied_to_vcc_i | std_logic |

| txlock_i | std_logic |

| tx_sync_i | std_logic |

| tx_usrclks_stable_i | std_logic |

| drp_reset_i | std_logic |

| ch1 | std_logic |

| ch2 | std_logic |

| tgff1 | std_logic |

| tgff2 | std_logic |

| recclklatch0 | std_logic |

| recclklatch1 | std_logic |

| tile0_combusout_a_i | std_logic_vector ( 15 downto 0 ) |

| tile0_combusout_b_i | std_logic_vector ( 15 downto 0 ) |

Component Instantiations | |

| MGT0_USRCLK2_BUF | BUFR |

| buffer clock for support logic | |

| MGT1_USRCLK2_BUF | BUFR |

| buffer clock for support logic | |

| gt11_init_tx_i | GT11_INIT_TX <Entity GT11_INIT_TX> |

| gt11_init_rx_i | GT11_INIT_RX <Entity GT11_INIT_RX> |

| rio1 | rio |

| RocketIO 1. | |

| rio2 | rio |

| RocketIO 2. | |

Detailed Description

DAQ-RocketIO wrapper and support logic.This architecture instantiates the RocketIO primitive wrapper and its support blocks for proper initialization. Furthermore it aligns the RX data and takes care of the needed reset and clocking schemes. As the RocketIOs need a large amount of transitions in the incoming datastream for the RX-PLL to lock, a fixed pattern is sent out with the TX and XORed with the actual data externally. Inside the FPGA it is XORed in parallel after the RocketIOs again with the same pattern for full data reconstruction. This procedure is performed after booting the FPGA with the detector data masked while the procedure is running.

Definition at line 100 of file rio_rxtx.vhd.

Member Function Documentation

| auto_shift_set1 | ( mgt0_usr_clk2_i ) |

XOR pattern reco.

Definition at line 385 of file rio_rxtx.vhd.

00385 auto_shift_set1 : process(mgt0_usr_clk2_i) 00386 begin 00387 if mgt0_usr_clk2_i'event and mgt0_usr_clk2_i = '1' then 00388 if (TX_SYSTEM_RESET_IN or RX_SYSTEM_RESET_IN) = '1' then 00389 valid1 <= '0'; 00390 SHIFT1 <= 0; 00391 tgff1 <= '0'; 00392 MASK1 <= '0'; 00393 xor_tx_rx1 <= mgt0_txdata_i; 00394 else 00395 if (CALIB or CAL1) = '1' then 00396 if valid1 = '0' then 00397 if ch1 = '1' then 00398 if tgff1 = '0' then 00399 tgff1 <= '1'; 00400 xor_tx_rx1 <= xor_tx_rx1(30 downto 0) & xor_tx_rx1(31); 00401 --SHIFT1 <= SHIFT1 + 1; 00402 else 00403 tgff1 <= '0'; 00404 end if; 00405 else 00406 --SHIFT1 <= SHIFT1; 00407 valid1 <= '1'; 00408 MASK1 <= '1'; 00409 end if; 00410 end if; 00411 end if; 00412 end if; 00413 end if; 00414 end process auto_shift_set1;

| auto_shift_set2 | ( mgt1_usr_clk2_i ) |

XOR pattern reco.

Definition at line 417 of file rio_rxtx.vhd.

00417 auto_shift_set2 : process(mgt1_usr_clk2_i) 00418 begin 00419 if mgt1_usr_clk2_i'event and mgt1_usr_clk2_i = '1' then 00420 if (TX_SYSTEM_RESET_IN or RX_SYSTEM_RESET_IN) = '1' then 00421 valid2 <= '0'; 00422 SHIFT2 <= 0; 00423 tgff2 <= '0'; 00424 MASK2 <= '0'; 00425 xor_tx_rx2 <= mgt1_txdata_i; 00426 else 00427 if (CALIB or CAL2) = '1' then 00428 if valid2 = '0' then 00429 if ch2 = '1' then 00430 if tgff2 = '0' then 00431 tgff2 <= '1'; 00432 xor_tx_rx2 <= xor_tx_rx2(30 downto 0) & xor_tx_rx2(31); 00433 --SHIFT2 <= SHIFT2 + 1; 00434 else 00435 tgff2 <= '0'; 00436 end if; 00437 else 00438 --SHIFT2 <= SHIFT2; 00439 valid2 <= '1'; 00440 MASK2 <= '1'; 00441 end if; 00442 end if; 00443 end if; 00444 end if; 00445 end if; 00446 end process auto_shift_set2;

| rx_res | ( drp_clk_in_i ) |

Extend the RX_SYSTEM_RESET_IN signal using the DRP_CLK.

Definition at line 526 of file rio_rxtx.vhd.

00526 rx_res : process(drp_clk_in_i) 00527 begin 00528 if(drp_clk_in_i'event and drp_clk_in_i = '1') then 00529 debounce_rx_system_reset_r <= rx_system_reset_in_i & debounce_rx_system_reset_r(0 to 2); 00530 end if; 00531 end process rx_res;

| tx_res | ( drp_clk_in_i ) |

Extend the TX_SYSTEM_RESET_IN signal using the DRP_CLK.

Definition at line 513 of file rio_rxtx.vhd.

00513 tx_res : process(drp_clk_in_i) 00514 begin 00515 if(drp_clk_in_i'event and drp_clk_in_i = '1') then 00516 debounce_tx_system_reset_r <= tx_system_reset_in_i & debounce_tx_system_reset_r(0 to 2); 00517 end if; 00518 end process tx_res;

Member Data Documentation

GT11_INIT_RX [Component] |

gt11_init_rx_i GT11_INIT_RX [Component Instantiation] |

This module is responsible for performing the correct reset and lock procedure as recommended in the user guide

Definition at line 579 of file rio_rxtx.vhd.

GT11_INIT_TX [Component] |

gt11_init_tx_i GT11_INIT_TX [Component Instantiation] |

This module is responsible for performing the correct reset and lock procedure as recommended in the user guide

Definition at line 559 of file rio_rxtx.vhd.

MGT0_USRCLK2_BUF BUFR [Component Instantiation] |

MGT1_USRCLK2_BUF BUFR [Component Instantiation] |

rio [Component] |

The documentation for this class was generated from the following file: