raw_data_emul Entity Reference

Pattern generator to fill raw data buffers. More...

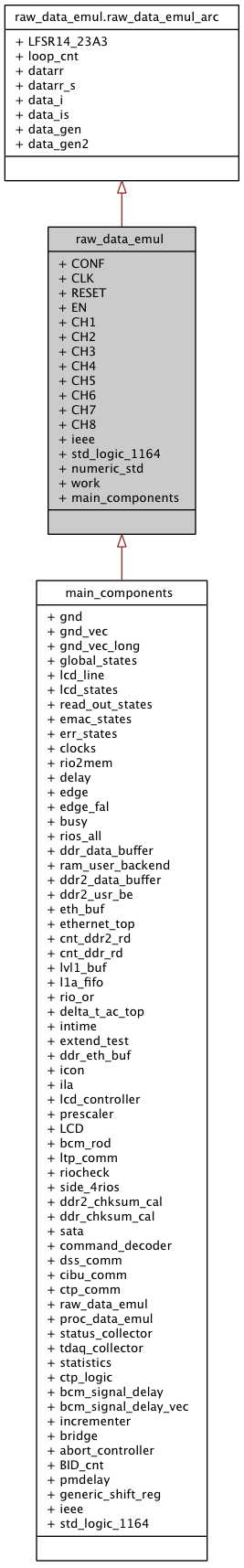

Inheritance diagram for raw_data_emul:

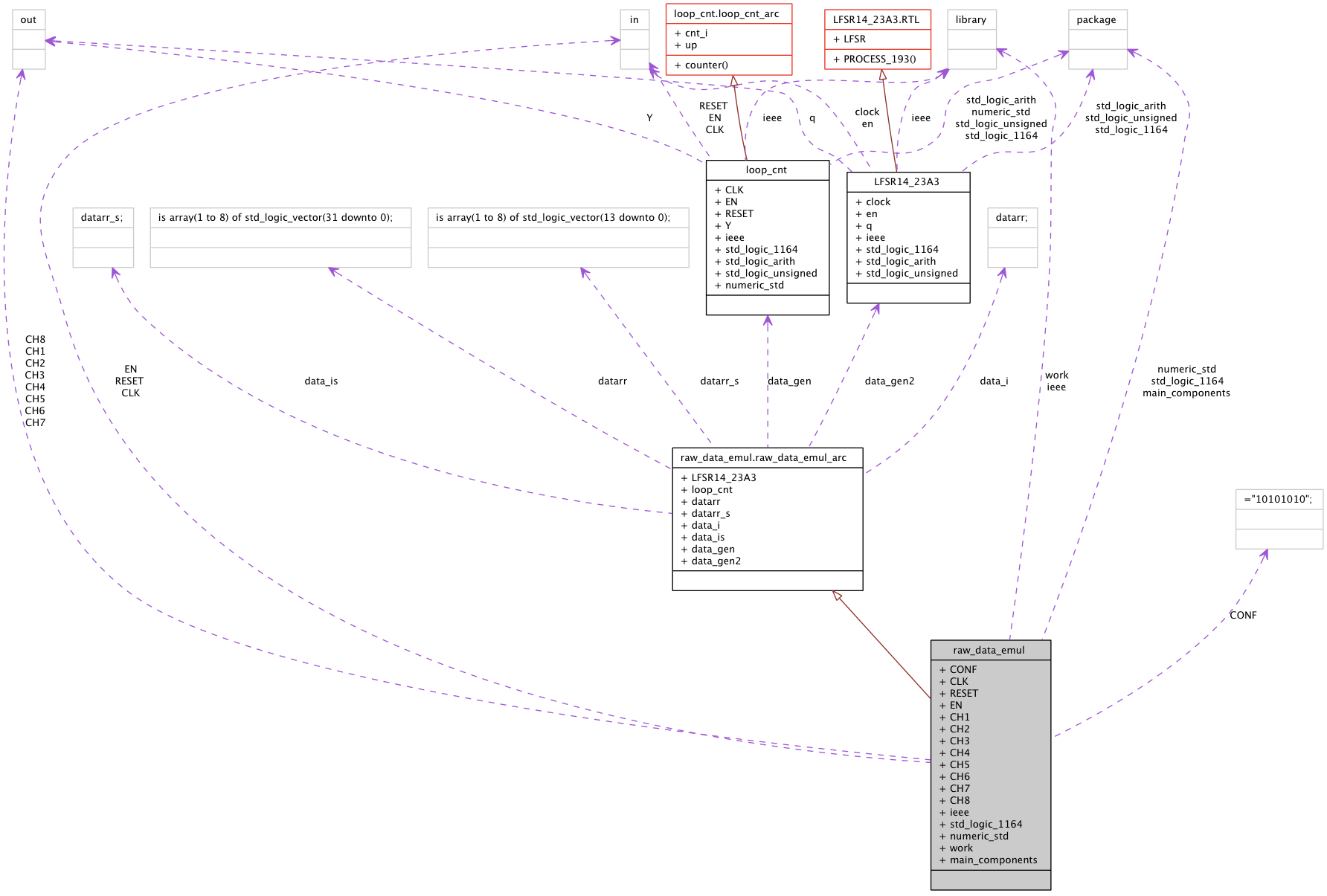

Collaboration diagram for raw_data_emul:

Architectures | |

| raw_data_emul_arc | Architecture |

| Pattern generator to fill raw data buffers. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| work | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| numeric_std | |

| arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file | |

| main_components | Package <main_components> |

Generics | |

| CONF | bit_vector ( 1 to 8 ) := " 10101010 " |

| select pattern, 1 = counter, 0 = LFSR | |

Ports | |

| CLK | in std_logic |

| Clock. | |

| RESET | in std_logic |

| Reset. | |

| EN | in std_logic |

| Enable. | |

| CH1 | out std_logic_vector ( 31 downto 0 ) |

| Pattern 1 Ch. | |

| CH2 | out std_logic_vector ( 31 downto 0 ) |

| Pattern 1 Ch. | |

| CH3 | out std_logic_vector ( 31 downto 0 ) |

| Pattern 1 Ch. | |

| CH4 | out std_logic_vector ( 31 downto 0 ) |

| Pattern 1 Ch. | |

| CH5 | out std_logic_vector ( 31 downto 0 ) |

| Pattern 1 Ch. | |

| CH6 | out std_logic_vector ( 31 downto 0 ) |

| Pattern 1 Ch. | |

| CH7 | out std_logic_vector ( 31 downto 0 ) |

| Pattern 1 Ch. | |

| CH8 | out std_logic_vector ( 31 downto 0 ) |

| Pattern 1 Ch. | |

Detailed Description

Pattern generator to fill raw data buffers.Fill raw data buffers with fixed patterns, generated with LFSRs and continously looping counters. Can be selected per channel via generic

Definition at line 37 of file raw_data_emul.vhd.

Member Data Documentation

CH1 out std_logic_vector ( 31 downto 0 ) [Port] |

CH2 out std_logic_vector ( 31 downto 0 ) [Port] |

CH3 out std_logic_vector ( 31 downto 0 ) [Port] |

CH4 out std_logic_vector ( 31 downto 0 ) [Port] |

CH5 out std_logic_vector ( 31 downto 0 ) [Port] |

CH6 out std_logic_vector ( 31 downto 0 ) [Port] |

CH7 out std_logic_vector ( 31 downto 0 ) [Port] |

CH8 out std_logic_vector ( 31 downto 0 ) [Port] |

CLK in std_logic [Port] |

CONF bit_vector ( 1 to 8 ) := " 10101010 " [Generic] |

EN in std_logic [Port] |

ieee library [Library] |

standard IEEE library

Reimplemented in main_components.

Definition at line 25 of file raw_data_emul.vhd.

numeric_std package [Package] |

arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file

Definition at line 29 of file raw_data_emul.vhd.

RESET in std_logic [Port] |

std_logic_1164 package [Package] |

std_logic definitions, see file

Reimplemented in main_components.

Definition at line 27 of file raw_data_emul.vhd.

The documentation for this class was generated from the following file: