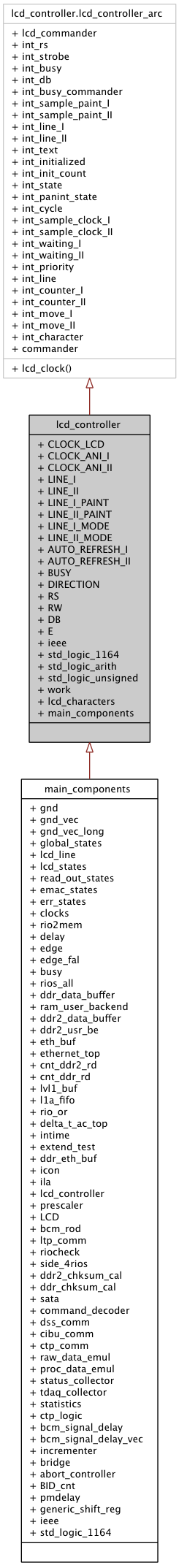

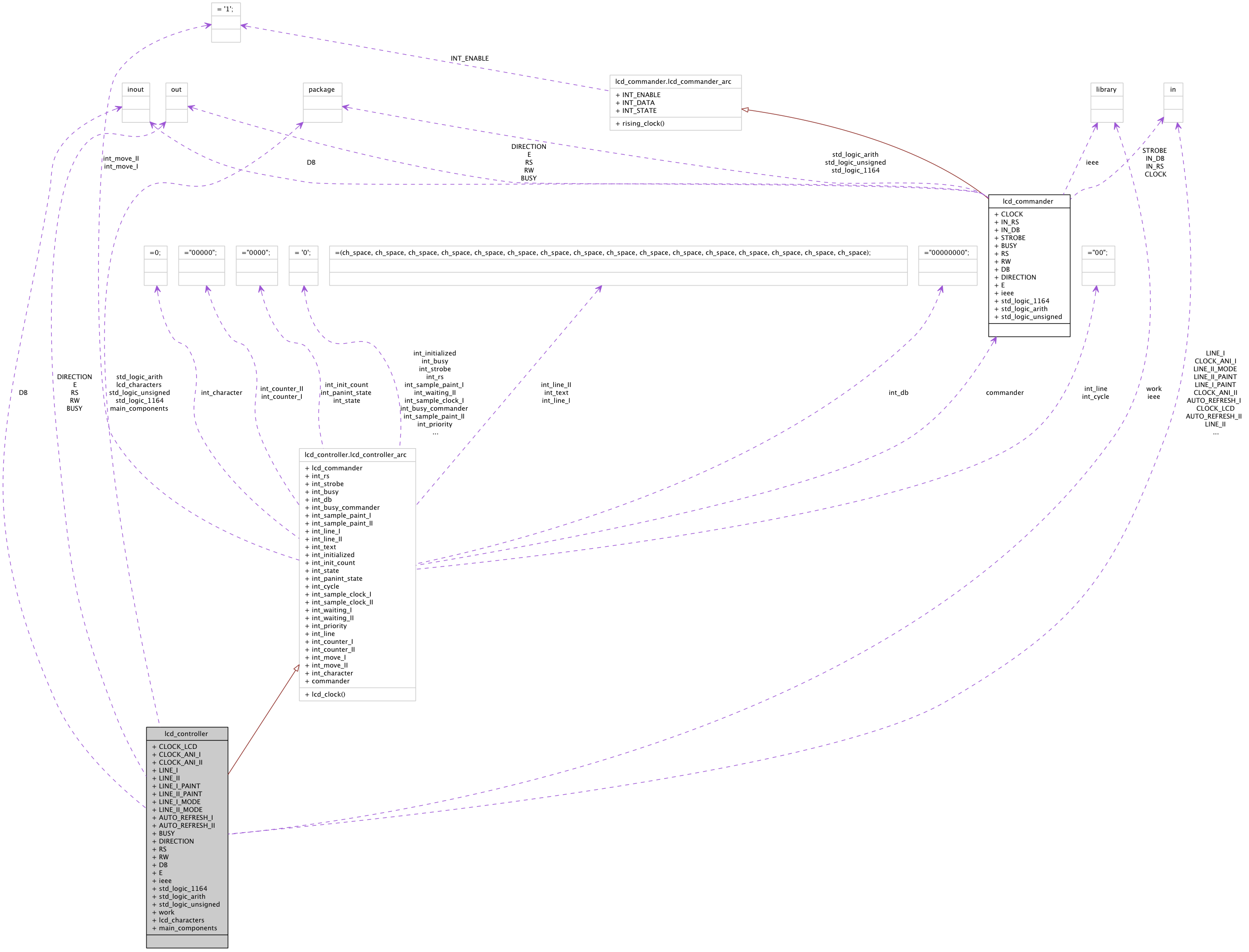

lcd_controller Entity Reference

LCD controller. More...

Architectures | |

| lcd_controller_arc | Architecture |

Libraries | |

| ieee | |

| standard IEEE library | |

| work | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

| lcd_characters | Package <lcd_characters> |

| main_components | Package <main_components> |

Ports | |

| CLOCK_LCD | in std_logic |

| basic clock, it has to be slower than 2 MHz | |

| CLOCK_ANI_I | in std_logic |

| on rising edge the line 2 is displayed (next frame when animated) | |

| CLOCK_ANI_II | in std_logic |

| on rising edge the line 2 is displayed (next frame when animated) | |

| LINE_I | in lcd_line |

| input line 1 text | |

| LINE_II | in lcd_line |

| input line 2 text | |

| LINE_I_PAINT | in std_logic |

| on rising edge LINE_I gets in the internal buffer | |

| LINE_II_PAINT | in std_logic |

| on rising edge LINE_II gets in the internal buffer | |

| LINE_I_MODE | in std_logic_vector ( 1 downto 0 ) |

| | 00 static text 10 moving <- | |

| LINE_II_MODE | in std_logic_vector ( 1 downto 0 ) |

| | 01 moving -> 11 flashing | |

| AUTO_REFRESH_I | in std_logic |

| triggers display on paint signal on line 1 | |

| AUTO_REFRESH_II | in std_logic |

| triggers display on paint signal on line 1 | |

| BUSY | out std_logic |

| while this is '1' the lcd is initializing | |

| DIRECTION | out std_logic |

| interface to pins | |

| RS | out std_logic |

| interface to pins | |

| RW | out std_logic |

| interface to pins | |

| DB | inout std_logic_vector ( 7 downto 0 ) |

| interface to pins | |

| E | out std_logic |

| interface to pins | |

Detailed Description

LCD controller.this entity manipulates with LCD, according to the input data (characters and modes)

Definition at line 39 of file lcd_controller.vhd.

Member Data Documentation

AUTO_REFRESH_I in std_logic [Port] |

AUTO_REFRESH_II in std_logic [Port] |

BUSY out std_logic [Port] |

CLOCK_ANI_I in std_logic [Port] |

on rising edge the line 2 is displayed (next frame when animated)

Definition at line 42 of file lcd_controller.vhd.

CLOCK_ANI_II in std_logic [Port] |

on rising edge the line 2 is displayed (next frame when animated)

Definition at line 43 of file lcd_controller.vhd.

CLOCK_LCD in std_logic [Port] |

DB inout std_logic_vector ( 7 downto 0 ) [Port] |

DIRECTION out std_logic [Port] |

E out std_logic [Port] |

ieee library [Library] |

standard IEEE library

Reimplemented in main_components.

Definition at line 25 of file lcd_controller.vhd.

LINE_I in lcd_line [Port] |

LINE_I_MODE in std_logic_vector ( 1 downto 0 ) [Port] |

LINE_I_PAINT in std_logic [Port] |

LINE_II in lcd_line [Port] |

LINE_II_MODE in std_logic_vector ( 1 downto 0 ) [Port] |

LINE_II_PAINT in std_logic [Port] |

on rising edge LINE_II gets in the internal buffer

Definition at line 47 of file lcd_controller.vhd.

RS out std_logic [Port] |

RW out std_logic [Port] |

std_logic_1164 package [Package] |

std_logic definitions, see file

Reimplemented in main_components.

Definition at line 27 of file lcd_controller.vhd.

std_logic_arith package [Package] |

arithmetic operations on std_logic datatypes, see file

Definition at line 29 of file lcd_controller.vhd.

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 31 of file lcd_controller.vhd.

The documentation for this class was generated from the following file: