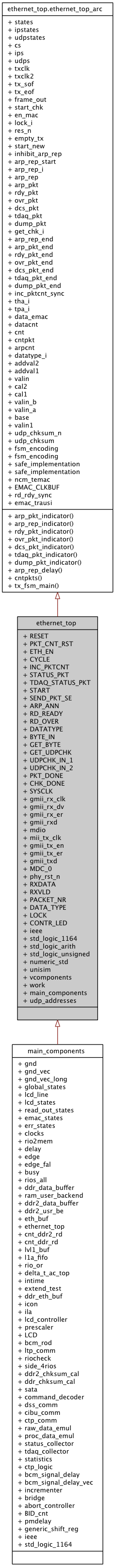

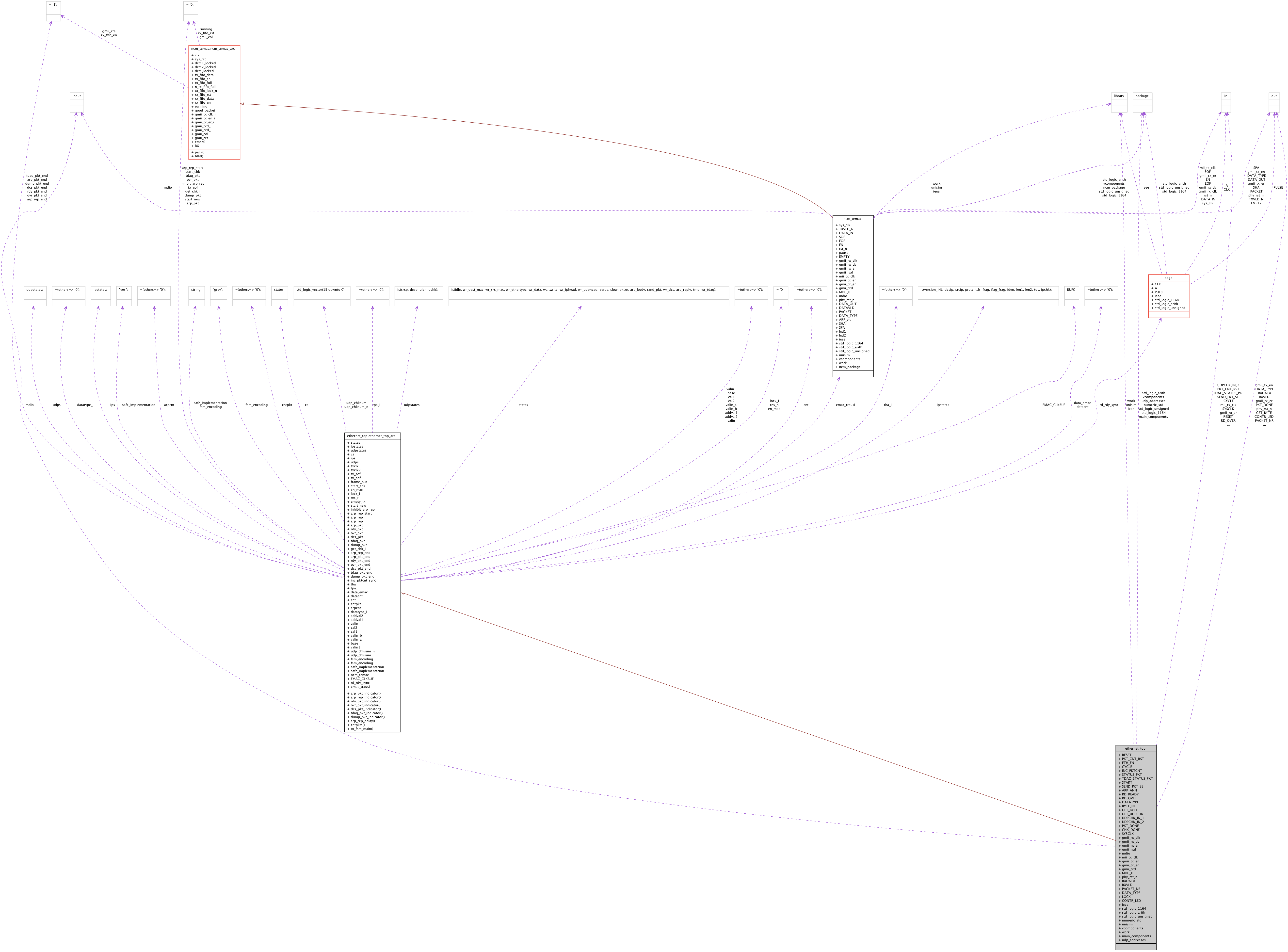

ethernet_top Entity Reference

Top module of Ethernet design part, both RX & TX. More...

Architectures | |

| ethernet_top_arc | Architecture |

| main logic for sending data & interfacing between EMAC & memories More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| unisim | |

| work | |

| Library with project specific headers. | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_arith | |

| arithmetic operations on std_logic datatypes, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

| numeric_std | |

| arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file | |

| vcomponents | |

| main_components | Package <main_components> |

| Header with declarations of main design components. | |

| udp_addresses | Package <udp_addresses> |

| Header with Ethernet constants & functions. | |

Ports | |

| RESET | in std_logic |

| global reset | |

| PKT_CNT_RST | in std_logic |

| reset for packet count | |

| ETH_EN | in std_logic |

| enable for TX | |

| CYCLE | in std_logic |

| continous sending enable | |

| INC_PKTCNT | in std_logic |

| increment packet number | |

| STATUS_PKT | in std_logic |

| send DCS status pkt, needs to be high for full duration of pkt | |

| TDAQ_STATUS_PKT | in std_logic |

| send TDAQ status pkt, needs to be high for full duration of pkt | |

| START | in std_logic |

| start sending of next packet (use only for buffer dumps) | |

| SEND_PKT_SE | in std_logic |

| start/end sending of a single packet, complete ethernet pkt must be provided | |

| ARP_ANN | in std_logic |

| send gratuitous ARP | |

| RD_READY | in std_logic |

| send read-out ready packet | |

| RD_OVER | in std_logic |

| send read-out done packet | |

| DATATYPE | in std_logic |

| flag to indentify data | |

| BYTE_IN | in std_logic_vector ( 7 downto 0 ) |

| data to be sent | |

| GET_BYTE | out std_logic |

| fetch next databyte from buffers | |

| GET_UDPCHK | out std_logic |

| fetch checksum for next packet | |

| UDPCHK_IN_1 | in std_logic_vector ( 15 downto 0 ) |

| UDP checksum in 1. | |

| UDPCHK_IN_2 | in std_logic_vector ( 15 downto 0 ) |

| UDP checksum in 2. | |

| PKT_DONE | out std_logic |

| transmission of one packet is finished | |

| CHK_DONE | out std_logic |

| checksum calculation finished, not in use | |

| SYSCLK | in std_logic |

| 100 MHz clock in | |

| gmii_rx_clk | in std_logic |

| EMAC PHY RX clk. | |

| gmii_rx_dv | in std_logic |

| EMAC PHY RX valid. | |

| gmii_rx_er | in std_logic |

| EMAC PHY RX error. | |

| gmii_rxd | in std_logic_vector ( 0 to 7 ) |

| EMAC PHY RX data. | |

| mdio | inout std_logic |

| MDIO. | |

| mii_tx_clk | in std_logic |

| EMAC PHY TX clk. | |

| gmii_tx_en | out std_logic |

| EMAC PHY TX enable. | |

| gmii_tx_er | out std_logic |

| EMAC PHY TX error. | |

| gmii_txd | out std_logic_vector ( 0 to 3 ) |

| EMAC PHY TX data. | |

| MDC_0 | out std_logic |

| MDIO. | |

| phy_rst_n | out std_logic |

| EMAC PHY reset. | |

| RXDATA | out std_logic_vector ( 7 downto 0 ) |

| RX data byte out. | |

| RXVLD | out std_logic |

| RX data valid flag. | |

| PACKET_NR | out std_logic_vector ( 19 downto 0 ) |

| RX packet number. | |

| DATA_TYPE | out std_logic_vector ( 11 downto 0 ) |

| RX data type identifier. | |

| LOCK | out std_logic |

| EMAC clocks ready. | |

| CONTR_LED | out std_logic |

| debug led | |

Detailed Description

Top module of Ethernet design part, both RX & TX.This Entity is the uppermost module of the Ethernet design part. It provides an interface to the rest of the FPGA in both RX & TX direction.

Definition at line 49 of file ethernet_top.vhd.

Member Data Documentation

ARP_ANN in std_logic [Port] |

BYTE_IN in std_logic_vector ( 7 downto 0 ) [Port] |

CHK_DONE out std_logic [Port] |

CONTR_LED out std_logic [Port] |

CYCLE in std_logic [Port] |

DATA_TYPE out std_logic_vector ( 11 downto 0 ) [Port] |

DATATYPE in std_logic [Port] |

ETH_EN in std_logic [Port] |

GET_BYTE out std_logic [Port] |

GET_UDPCHK out std_logic [Port] |

gmii_rx_clk in std_logic [Port] |

gmii_rx_dv in std_logic [Port] |

gmii_rx_er in std_logic [Port] |

gmii_rxd in std_logic_vector ( 0 to 7 ) [Port] |

gmii_tx_en out std_logic [Port] |

gmii_tx_er out std_logic [Port] |

gmii_txd out std_logic_vector ( 0 to 3 ) [Port] |

ieee library [Library] |

standard IEEE library

Reimplemented in main_components.

Definition at line 24 of file ethernet_top.vhd.

INC_PKTCNT in std_logic [Port] |

LOCK out std_logic [Port] |

main_components package [Package] |

MDC_0 out std_logic [Port] |

mdio inout std_logic [Port] |

mii_tx_clk in std_logic [Port] |

numeric_std package [Package] |

arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file

Definition at line 32 of file ethernet_top.vhd.

PACKET_NR out std_logic_vector ( 19 downto 0 ) [Port] |

phy_rst_n out std_logic [Port] |

PKT_CNT_RST in std_logic [Port] |

PKT_DONE out std_logic [Port] |

RD_OVER in std_logic [Port] |

RD_READY in std_logic [Port] |

RESET in std_logic [Port] |

RXDATA out std_logic_vector ( 7 downto 0 ) [Port] |

RXVLD out std_logic [Port] |

SEND_PKT_SE in std_logic [Port] |

start/end sending of a single packet, complete ethernet pkt must be provided

Definition at line 59 of file ethernet_top.vhd.

START in std_logic [Port] |

start sending of next packet (use only for buffer dumps)

Definition at line 58 of file ethernet_top.vhd.

STATUS_PKT in std_logic [Port] |

send DCS status pkt, needs to be high for full duration of pkt

Definition at line 56 of file ethernet_top.vhd.

std_logic_1164 package [Package] |

std_logic definitions, see file

Reimplemented in main_components.

Definition at line 26 of file ethernet_top.vhd.

std_logic_arith package [Package] |

arithmetic operations on std_logic datatypes, see file

Definition at line 28 of file ethernet_top.vhd.

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 30 of file ethernet_top.vhd.

SYSCLK in std_logic [Port] |

TDAQ_STATUS_PKT in std_logic [Port] |

send TDAQ status pkt, needs to be high for full duration of pkt

Definition at line 57 of file ethernet_top.vhd.

udp_addresses package [Package] |

UDPCHK_IN_1 in std_logic_vector ( 15 downto 0 ) [Port] |

UDPCHK_IN_2 in std_logic_vector ( 15 downto 0 ) [Port] |

unisim library [Library] |

Library with Xilinx primitives Library with Xilinx primitives

Definition at line 35 of file ethernet_top.vhd.

vcomponents package [Package] |

Header with Xilinx primitives Header with Xilinx primitives

Definition at line 38 of file ethernet_top.vhd.

work library [Library] |

The documentation for this class was generated from the following file: