delay_adj.delay_adj_arc Architecture Reference

Fine delay for 2 RocketIO channels. More...

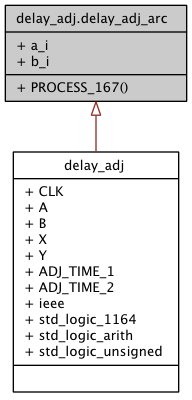

Inheritance diagram for delay_adj.delay_adj_arc:

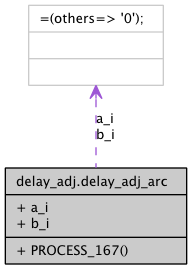

Collaboration diagram for delay_adj.delay_adj_arc:

Processes | |

| PROCESS_167 | ( CLK ) |

| 64-bit wide shift register with parallel read/write | |

Signals | |

| a_i | std_logic_vector ( 63 downto 0 ) := ( others = > ' 0 ' ) |

| b_i | std_logic_vector ( 63 downto 0 ) := ( others = > ' 0 ' ) |

Detailed Description

Fine delay for 2 RocketIO channels.Data can be shifted by taps, latency is 1 clock cycle. Delay value can be set at runtime.

Definition at line 50 of file delay_adj.vhd.

Member Function Documentation

| PROCESS_167 | ( CLK ) |

64-bit wide shift register with parallel read/write

Definition at line 58 of file delay_adj.vhd.

00058 process(CLK) 00059 begin 00060 if CLK'event and CLK = '1' then 00061 a_i <= A & a_i(63 downto 32); 00062 b_i <= B & b_i(63 downto 32); 00063 X <= a_i(63-ADJ_TIME_1 downto 32-ADJ_TIME_1); 00064 Y <= b_i(63-ADJ_TIME_2 downto 32-ADJ_TIME_2); 00065 end if; 00066 end process;

The documentation for this class was generated from the following file: