ddr2_mem_user_interface_0 Entity Reference

DDR2 controller user interface. More...

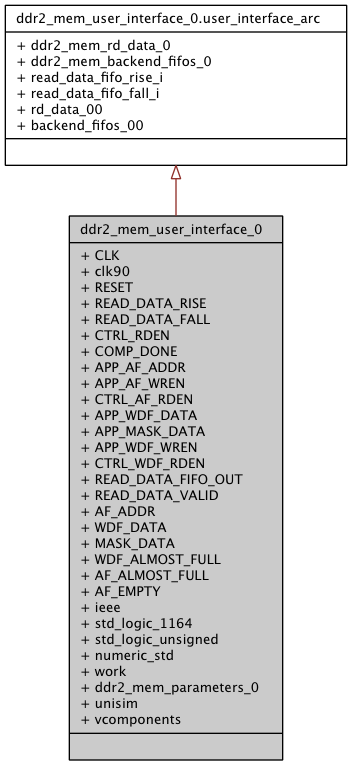

Inheritance diagram for ddr2_mem_user_interface_0:

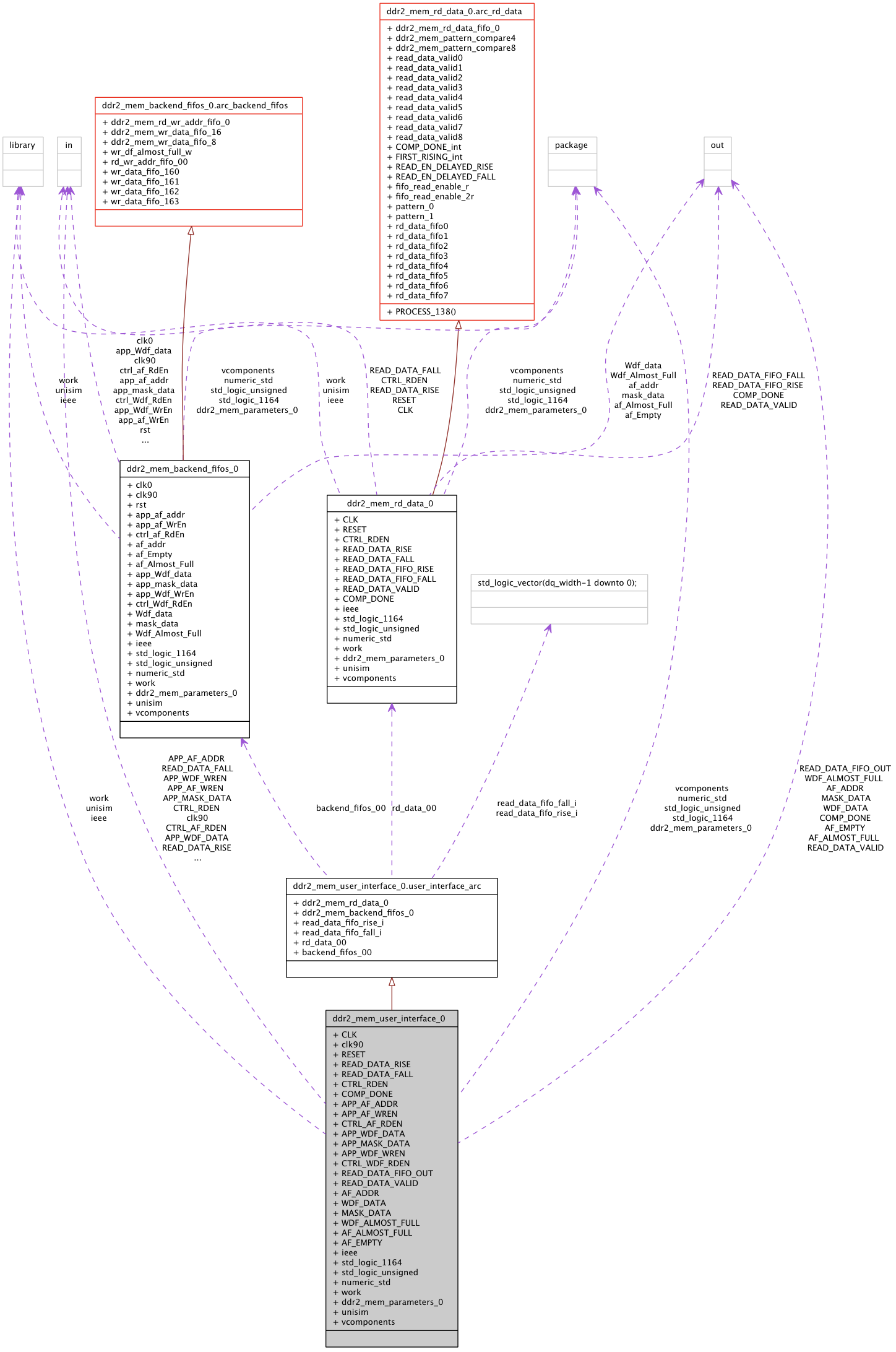

Collaboration diagram for ddr2_mem_user_interface_0:

Architectures | |

| user_interface_arc | Architecture |

| DDR2 controller user interface. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| work | |

| unisim | |

| Library with Xilinx primitives. | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

| numeric_std | |

| arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file | |

| ddr2_mem_parameters_0 | Package <ddr2_mem_parameters_0> |

| vcomponents | |

| Header with Xilinx primitives. | |

Ports | |

| CLK | in std_logic |

| clock | |

| clk90 | in std_logic |

clock, shifted by  | |

| RESET | in std_logic |

| reset | |

| READ_DATA_RISE | in std_logic_vector ( data_width-1 downto 0 ) |

| rising edge data read | |

| READ_DATA_FALL | in std_logic_vector ( data_width-1 downto 0 ) |

| falling edge data read | |

| CTRL_RDEN | in std_logic |

| control read enable | |

| COMP_DONE | out std_logic |

| pattern compare done flag | |

| APP_AF_ADDR | in std_logic_vector ( 35 downto 0 ) |

| address in | |

| APP_AF_WREN | in std_logic |

| address write enable | |

| CTRL_AF_RDEN | in std_logic |

| address read enable | |

| APP_WDF_DATA | in std_logic_vector ( dq_width *2-1 downto 0 ) |

| data in | |

| APP_MASK_DATA | in std_logic_vector ( dm_width *2-1 downto 0 ) |

| data mask in | |

| APP_WDF_WREN | in std_logic |

| data write enable | |

| CTRL_WDF_RDEN | in std_logic |

| data read enable | |

| READ_DATA_FIFO_OUT | out std_logic_vector ( dq_width *2-1 downto 0 ) |

| read data out | |

| READ_DATA_VALID | out std_logic |

| data valid | |

| AF_ADDR | out std_logic_vector ( 35 downto 0 ) |

| address out | |

| WDF_DATA | out std_logic_vector ( dq_width *2-1 downto 0 ) |

| data out | |

| MASK_DATA | out std_logic_vector ( dm_width *2-1 downto 0 ) |

| data mask out | |

| WDF_ALMOST_FULL | out std_logic |

| data FIFO full flag | |

| AF_ALMOST_FULL | out std_logic |

| address FIFO full flag | |

| AF_EMPTY | out std_logic |

| address FIFO empty flag | |

Detailed Description

DDR2 controller user interface.This module interfaces with the user. The user should provide the data and various commands.

Definition at line 59 of file ddr2_mem_user_interface_0.vhd.

Member Data Documentation

AF_ADDR out std_logic_vector ( 35 downto 0 ) [Port] |

AF_ALMOST_FULL out std_logic [Port] |

AF_EMPTY out std_logic [Port] |

APP_AF_ADDR in std_logic_vector ( 35 downto 0 ) [Port] |

APP_AF_WREN in std_logic [Port] |

APP_MASK_DATA in std_logic_vector ( dm_width *2-1 downto 0 ) [Port] |

APP_WDF_DATA in std_logic_vector ( dq_width *2-1 downto 0 ) [Port] |

APP_WDF_WREN in std_logic [Port] |

CLK in std_logic [Port] |

clk90 in std_logic [Port] |

COMP_DONE out std_logic [Port] |

CTRL_AF_RDEN in std_logic [Port] |

CTRL_RDEN in std_logic [Port] |

CTRL_WDF_RDEN in std_logic [Port] |

ieee library [Library] |

MASK_DATA out std_logic_vector ( dm_width *2-1 downto 0 ) [Port] |

numeric_std package [Package] |

arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file

Definition at line 48 of file ddr2_mem_user_interface_0.vhd.

READ_DATA_FALL in std_logic_vector ( data_width-1 downto 0 ) [Port] |

READ_DATA_FIFO_OUT out std_logic_vector ( dq_width *2-1 downto 0 ) [Port] |

READ_DATA_RISE in std_logic_vector ( data_width-1 downto 0 ) [Port] |

READ_DATA_VALID out std_logic [Port] |

RESET in std_logic [Port] |

std_logic_1164 package [Package] |

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 46 of file ddr2_mem_user_interface_0.vhd.

unisim library [Library] |

vcomponents package [Package] |

WDF_ALMOST_FULL out std_logic [Port] |

WDF_DATA out std_logic_vector ( dq_width *2-1 downto 0 ) [Port] |

The documentation for this class was generated from the following file: