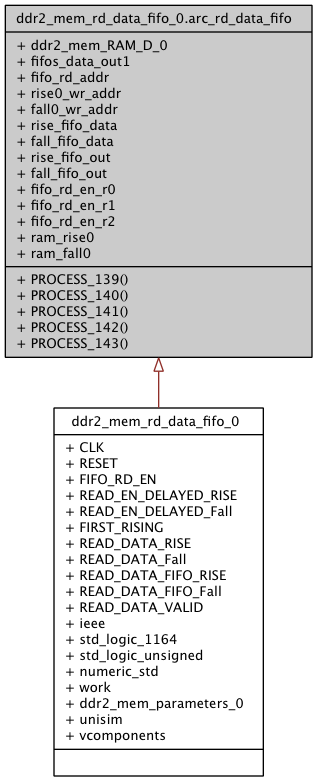

ddr2_mem_rd_data_fifo_0.arc_rd_data_fifo Architecture Reference

DistRAM for read data. More...

Processes | |

| PROCESS_139 | ( CLK ) |

| Read Enable generation for fifos based on the empty flags. | |

| PROCESS_140 | ( CLK ) |

| Write Pointer increment for FIFOs. | |

| PROCESS_141 | ( CLK ) |

| Write Pointer increment for FIFOs. | |

| PROCESS_142 | ( CLK ) |

| FIFO Data Output Sequencing. | |

| PROCESS_143 | ( CLK ) |

| FIFO Data Output Sequencing. | |

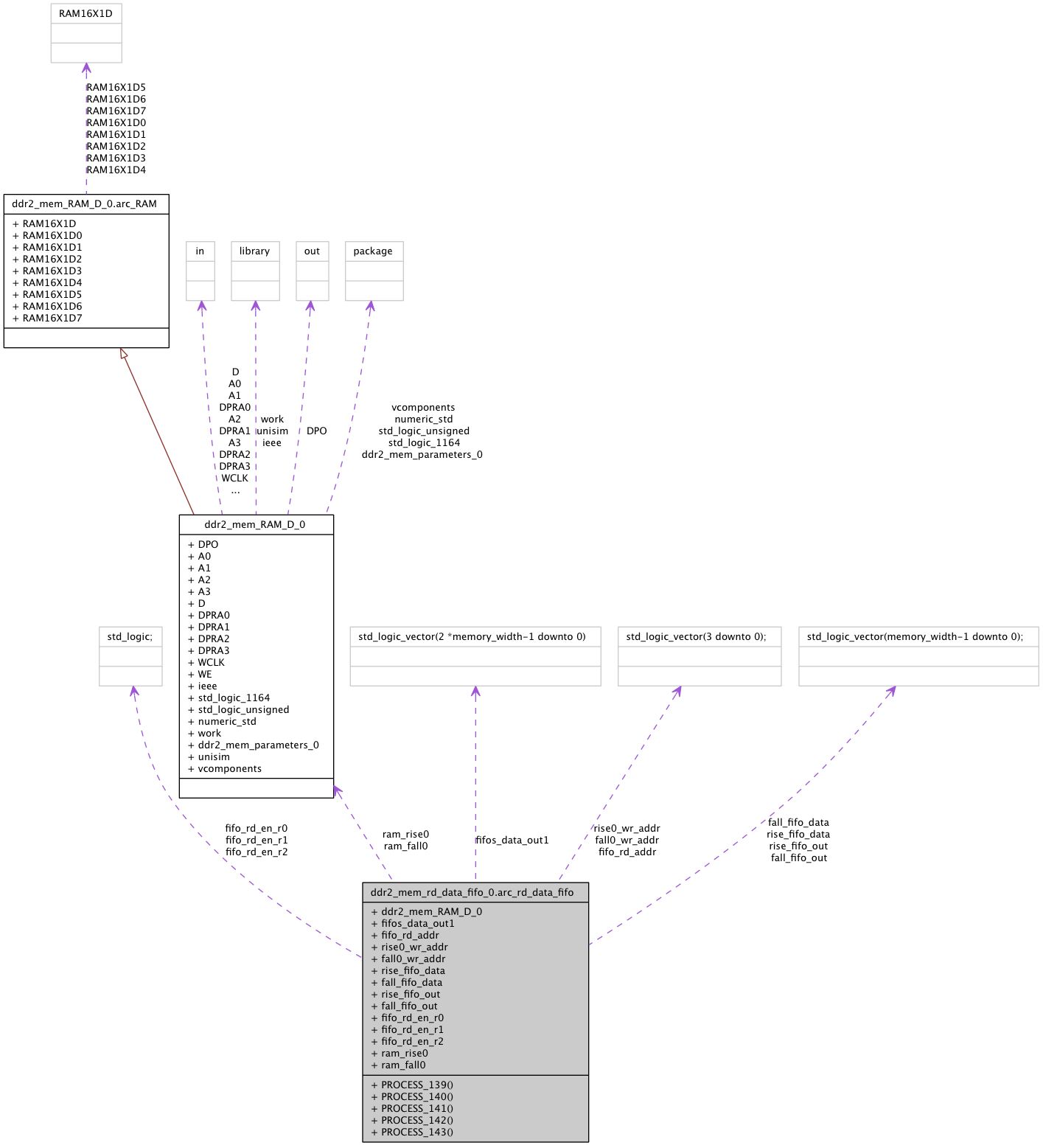

Components | |

| ddr2_mem_RAM_D_0 | <Entity ddr2_mem_RAM_D_0> |

| RAM primitive. | |

Signals | |

| fifos_data_out1 | std_logic_vector ( 2 *memory_width-1 downto 0 ) |

| fifo_rd_addr | std_logic_vector ( 3 downto 0 ) |

| rise0_wr_addr | std_logic_vector ( 3 downto 0 ) |

| fall0_wr_addr | std_logic_vector ( 3 downto 0 ) |

| rise_fifo_data | std_logic_vector ( memory_width-1 downto 0 ) |

| fall_fifo_data | std_logic_vector ( memory_width-1 downto 0 ) |

| rise_fifo_out | std_logic_vector ( memory_width-1 downto 0 ) |

| fall_fifo_out | std_logic_vector ( memory_width-1 downto 0 ) |

| fifo_rd_en_r0 | std_logic |

| fifo_rd_en_r1 | std_logic |

| fifo_rd_en_r2 | std_logic |

Component Instantiations | |

| ram_rise0 | ddr2_mem_RAM_D_0 <Entity ddr2_mem_RAM_D_0> |

| ram_fall0 | ddr2_mem_RAM_D_0 <Entity ddr2_mem_RAM_D_0> |

Detailed Description

DistRAM for read data.This module instantiates the distributed RAM which stores the read data from the memory.

Definition at line 80 of file ddr2_mem_rd_data_fifo_0.vhd.

Member Function Documentation

| PROCESS_139 | ( CLK ) |

Read Enable generation for fifos based on the empty flags.

Definition at line 119 of file ddr2_mem_rd_data_fifo_0.vhd.

00119 process(CLK) 00120 begin 00121 if CLK'event and CLK = '1' then 00122 if (RESET = '1') then 00123 fifo_rd_en_r0 <= '0'; 00124 fifo_rd_en_r1 <= '0'; 00125 fifo_rd_en_r2 <= '0'; 00126 else 00127 00128 fifo_rd_en_r0 <= FIFO_RD_EN; 00129 fifo_rd_en_r1 <= fifo_rd_en_r0; 00130 fifo_rd_en_r2 <= fifo_rd_en_r1; 00131 end if; 00132 end if; 00133 end process;

| PROCESS_140 | ( CLK ) |

Write Pointer increment for FIFOs.

Definition at line 136 of file ddr2_mem_rd_data_fifo_0.vhd.

00136 process(CLK) 00137 begin 00138 if CLK'event and CLK = '1' then 00139 if (RESET = '1') then 00140 rise0_wr_addr(3 downto 0) <= X"0"; 00141 elsif (READ_EN_DELAYED_RISE = '1') then 00142 rise0_wr_addr(3 downto 0) <= rise0_wr_addr(3 downto 0) + "0001"; 00143 end if; 00144 end if; 00145 end process;

| PROCESS_141 | ( CLK ) |

Write Pointer increment for FIFOs.

Definition at line 148 of file ddr2_mem_rd_data_fifo_0.vhd.

00148 process(CLK) 00149 begin 00150 if CLK'event and CLK = '1' then 00151 if (RESET = '1') then 00152 fall0_wr_addr(3 downto 0) <= X"0"; 00153 elsif (READ_EN_DELAYED_Fall = '1') then 00154 fall0_wr_addr(3 downto 0) <= fall0_wr_addr(3 downto 0) + "0001"; 00155 end if; 00156 end if; 00157 end process;

| PROCESS_142 | ( CLK ) |

FIFO Data Output Sequencing.

Definition at line 160 of file ddr2_mem_rd_data_fifo_0.vhd.

00160 process(CLK) 00161 begin 00162 if CLK'event and CLK = '1' then 00163 if (RESET = '1') then 00164 rise_fifo_data(memory_width-1 downto 0) <= (others => '0'); 00165 fall_fifo_data(memory_width-1 downto 0) <= (others => '0'); 00166 fifo_rd_addr(3 downto 0) <= X"0"; 00167 elsif (fifo_rd_en_r0 = '1') then 00168 rise_fifo_data(memory_width-1 downto 0) <= rise_fifo_out(memory_width-1 downto 0); 00169 fall_fifo_data(memory_width-1 downto 0) <= fall_fifo_out(memory_width-1 downto 0); 00170 fifo_rd_addr(3 downto 0) <= fifo_rd_addr(3 downto 0) + "0001"; 00171 end if; 00172 end if; 00173 end process;

| PROCESS_143 | ( CLK ) |

FIFO Data Output Sequencing.

Definition at line 176 of file ddr2_mem_rd_data_fifo_0.vhd.

00176 process(CLK) 00177 begin 00178 if CLK'event and CLK = '1' then 00179 if (RESET = '1') then 00180 fifos_data_out1(2*memory_width-1 downto 0) <= (others => '0'); 00181 elsif (fifo_rd_en_r1 = '1') then 00182 if (FIRST_RISING = '1') then 00183 fifos_data_out1(2*memory_width-1 downto 0) <= fall_fifo_data(memory_width-1 downto 0) & rise_fifo_data(memory_width-1 downto 0); 00184 else 00185 fifos_data_out1(2*memory_width-1 downto 0) <= rise_fifo_data(memory_width-1 downto 0) & fall_fifo_data(memory_width-1 downto 0); 00186 end if; 00187 end if; 00188 end if; 00189 end process;

Member Data Documentation

ddr2_mem_RAM_D_0 [Component] |

ram_fall0 ddr2_mem_RAM_D_0 [Component Instantiation] |

Distributed RAM 4 bit wide FIFO instantiations (2 FIFOs per strobe, rising edge data fifo and falling edge data fifo) FIFOs associated with DQS(0)

Definition at line 211 of file ddr2_mem_rd_data_fifo_0.vhd.

ram_rise0 ddr2_mem_RAM_D_0 [Component Instantiation] |

Distributed RAM 4 bit wide FIFO instantiations (2 FIFOs per strobe, rising edge data fifo and falling edge data fifo) FIFOs associated with DQS(0)

Definition at line 193 of file ddr2_mem_rd_data_fifo_0.vhd.

The documentation for this class was generated from the following file: