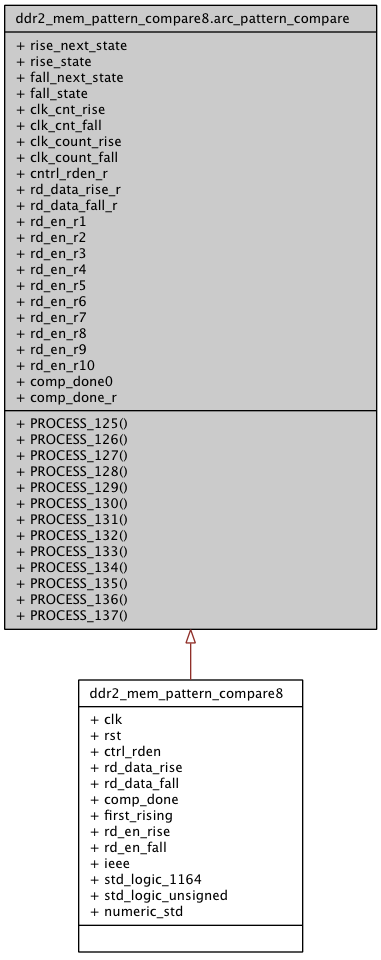

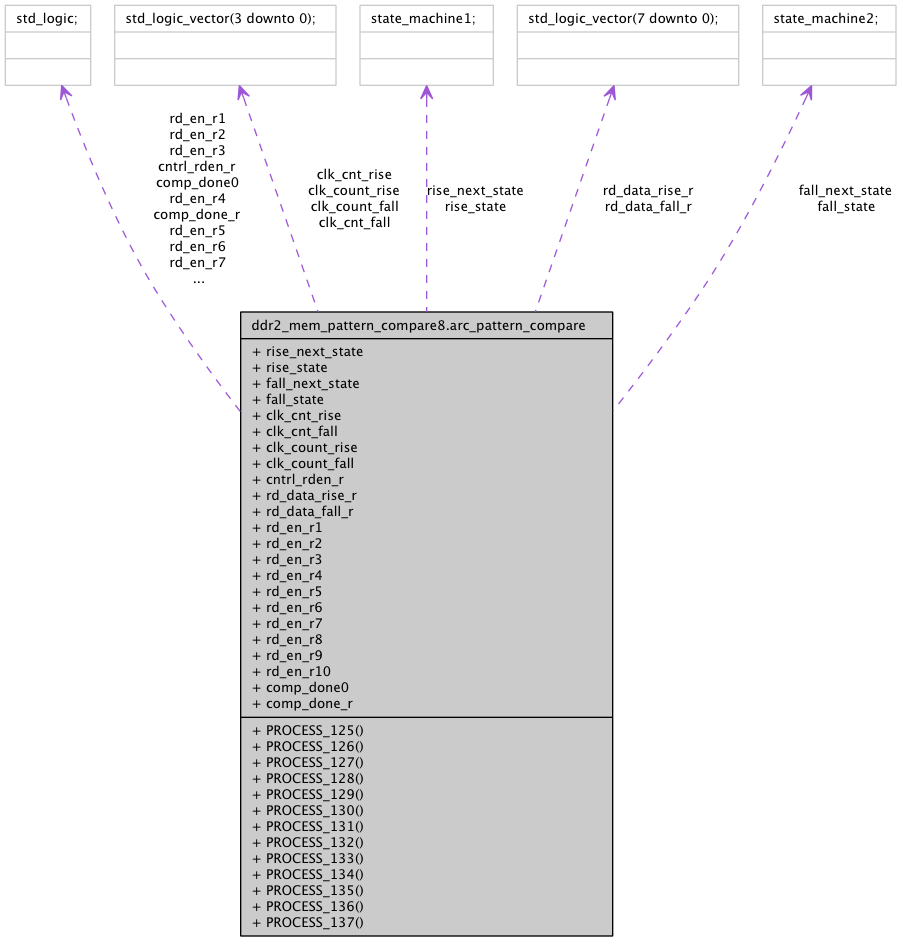

ddr2_mem_pattern_compare8.arc_pattern_compare Architecture Reference

DDR2 pattern compare. More...

Processes | |

| PROCESS_125 | ( clk ) |

| read enable shift | |

| PROCESS_126 | ( clk ) |

| done flag FF | |

| PROCESS_127 | ( clk ) |

| read enable rising edge data MUX | |

| PROCESS_128 | ( clk ) |

| read enable falling edge data MUX | |

| PROCESS_129 | ( clk ) |

| data FFs | |

| PROCESS_130 | ( clk ) |

| read enable FF | |

| PROCESS_131 | ( clk ) |

| first flag FF | |

| PROCESS_132 | ( clk ) |

| rise data | |

| PROCESS_133 | ( clk ) |

| FSM state transitions. | |

| PROCESS_134 | ( cntrl_rden_r , rise_state , rd_data_rise_r , rst ) |

| FSM. | |

| PROCESS_135 | ( clk ) |

| fall data | |

| PROCESS_136 | ( clk ) |

| FSM state transitions. | |

| PROCESS_137 | ( cntrl_rden_r , fall_state , rd_data_fall_r , rst ) |

| FSM. | |

Signals | |

| rise_next_state | state_machine1 |

| rise_state | state_machine1 |

| fall_next_state | state_machine2 |

| fall_state | state_machine2 |

| clk_cnt_rise | std_logic_vector ( 3 downto 0 ) |

| clk_cnt_fall | std_logic_vector ( 3 downto 0 ) |

| clk_count_rise | std_logic_vector ( 3 downto 0 ) |

| clk_count_fall | std_logic_vector ( 3 downto 0 ) |

| cntrl_rden_r | std_logic |

| rd_data_rise_r | std_logic_vector ( 7 downto 0 ) |

| rd_data_fall_r | std_logic_vector ( 7 downto 0 ) |

| rd_en_r1 | std_logic |

| rd_en_r2 | std_logic |

| rd_en_r3 | std_logic |

| rd_en_r4 | std_logic |

| rd_en_r5 | std_logic |

| rd_en_r6 | std_logic |

| rd_en_r7 | std_logic |

| rd_en_r8 | std_logic |

| rd_en_r9 | std_logic |

| rd_en_r10 | std_logic |

| comp_done0 | std_logic |

| comp_done_r | std_logic |

Detailed Description

DDR2 pattern compare.Compares the IOB output 8 bit data of one bank that is read data during the intilaization to get the delay for the data with respect to the command issued.

Definition at line 71 of file ddr2_mem_pattern_compare8.vhd.

Member Function Documentation

| PROCESS_125 | ( clk ) |

read enable shift

Definition at line 100 of file ddr2_mem_pattern_compare8.vhd.

00100 process(clk) 00101 begin 00102 if (clk = '1' and clk'event) then 00103 if (rst = '1') then 00104 rd_en_r1 <= '0'; 00105 rd_en_r2 <= '0'; 00106 rd_en_r3 <= '0'; 00107 rd_en_r4 <= '0'; 00108 rd_en_r5 <= '0'; 00109 rd_en_r6 <= '0'; 00110 rd_en_r7 <= '0'; 00111 rd_en_r8 <= '0'; 00112 rd_en_r9 <= '0'; 00113 rd_en_r10 <= '0'; 00114 else 00115 rd_en_r1 <= ctrl_rden; 00116 rd_en_r2 <= rd_en_r1; 00117 rd_en_r3 <= rd_en_r2; 00118 rd_en_r4 <= rd_en_r3; 00119 rd_en_r5 <= rd_en_r4; 00120 rd_en_r6 <= rd_en_r5; 00121 rd_en_r7 <= rd_en_r6; 00122 rd_en_r8 <= rd_en_r7; 00123 rd_en_r9 <= rd_en_r8; 00124 rd_en_r10 <= rd_en_r9; 00125 end if; 00126 end if; 00127 end process;

| PROCESS_126 | ( clk ) |

| PROCESS_127 | ( clk ) |

read enable rising edge data MUX

Definition at line 142 of file ddr2_mem_pattern_compare8.vhd.

00142 process(clk) 00143 begin 00144 if (clk = '1' and clk'event) then 00145 if (rst = '1') then 00146 rd_en_rise <= '0'; 00147 elsif(comp_done_r = '1') then 00148 case clk_count_rise is 00149 when "0011" => rd_en_rise <= rd_en_r2; 00150 when "0100" => rd_en_rise <= rd_en_r3; 00151 when "0101" => rd_en_rise <= rd_en_r4; 00152 when "0110" => rd_en_rise <= rd_en_r5; 00153 when "0111" => rd_en_rise <= rd_en_r6; 00154 when "1000" => rd_en_rise <= rd_en_r7; 00155 when "1001" => rd_en_rise <= rd_en_r8; 00156 when others => rd_en_rise <= '0'; 00157 end case; 00158 end if; 00159 end if; 00160 end process;

| PROCESS_128 | ( clk ) |

read enable falling edge data MUX

Definition at line 163 of file ddr2_mem_pattern_compare8.vhd.

00163 process(clk) 00164 begin 00165 if (clk = '1' and clk'event) then 00166 if (rst = '1') then 00167 rd_en_fall <= '0'; 00168 elsif(comp_done_r = '1') then 00169 case (clk_count_fall) is 00170 when "0011" => rd_en_fall <= rd_en_r2; 00171 when "0100" => rd_en_fall <= rd_en_r3; 00172 when "0101" => rd_en_fall <= rd_en_r4; 00173 when "0110" => rd_en_fall <= rd_en_r5; 00174 when "0111" => rd_en_fall <= rd_en_r6; 00175 when "1000" => rd_en_fall <= rd_en_r7; 00176 when "1001" => rd_en_fall <= rd_en_r8; 00177 when others => rd_en_fall <= '0'; 00178 end case; 00179 end if; 00180 end if; 00181 end process;

| PROCESS_129 | ( clk ) |

data FFs

Definition at line 186 of file ddr2_mem_pattern_compare8.vhd.

00186 process(clk) 00187 begin 00188 if (clk = '1' and clk'event) then 00189 if (rst = '1') then 00190 rd_data_rise_r <= (others => '0'); 00191 rd_data_fall_r <= (others => '0'); 00192 else 00193 rd_data_rise_r <= rd_data_rise; 00194 rd_data_fall_r <= rd_data_fall; 00195 end if; 00196 end if; 00197 end process;

| PROCESS_130 | ( clk ) |

| PROCESS_131 | ( clk ) |

first flag FF

Definition at line 212 of file ddr2_mem_pattern_compare8.vhd.

00212 process(clk) 00213 begin 00214 if (clk = '1' and clk'event) then 00215 if (rst = '1') then 00216 first_rising <= '0'; 00217 elsif(rise_state = rise_first_data and rd_data_rise_r = X"55") then 00218 first_rising <= '1'; 00219 end if; 00220 end if; 00221 end process;

| PROCESS_132 | ( clk ) |

rise data

Definition at line 226 of file ddr2_mem_pattern_compare8.vhd.

00226 process(clk) 00227 begin 00228 if (clk = '1' and clk'event) then 00229 if (rst = '1') then 00230 clk_cnt_rise <= (others => '0'); 00231 elsif(rise_state = rise_first_data) then 00232 clk_cnt_rise <= clk_cnt_rise + "0001"; 00233 else 00234 clk_cnt_rise <= clk_cnt_rise; 00235 end if; 00236 end if; 00237 end process;

| PROCESS_133 | ( clk ) |

FSM state transitions.

Definition at line 240 of file ddr2_mem_pattern_compare8.vhd.

00240 process(clk) 00241 begin 00242 if (clk = '1' and clk'event) then 00243 if (rst = '1') then 00244 rise_state <= rise_idle; 00245 else 00246 rise_state <= rise_next_state; 00247 end if; 00248 end if; 00249 end process;

| PROCESS_134 | ( cntrl_rden_r , | |

| rise_state , | ||

| rd_data_rise_r , | ||

| rst ) |

FSM.

Definition at line 252 of file ddr2_mem_pattern_compare8.vhd.

00252 process(cntrl_rden_r, rise_state, rd_data_rise_r, rst) 00253 begin 00254 if (rst = '1') then 00255 rise_next_state <= rise_idle; 00256 else 00257 case (rise_state) is 00258 when rise_idle => 00259 if(cntrl_rden_r = '1') then 00260 rise_next_state <= rise_first_data; 00261 else 00262 rise_next_state <= rise_idle; 00263 end if; 00264 00265 when rise_first_data => 00266 if((rd_data_rise_r = X"AA") or (rd_data_rise_r = X"55")) then 00267 rise_next_state <= rise_comp_over; --second_data 00268 else 00269 rise_next_state <= rise_first_data; 00270 end if; 00271 00272 when rise_second_data => 00273 if((rd_data_rise_r = X"99") or (rd_data_rise_r = X"66")) then 00274 rise_next_state <= rise_comp_over; 00275 else 00276 rise_next_state <= rise_first_data; 00277 end if; 00278 00279 when rise_comp_over => 00280 rise_next_state <= rise_comp_over; 00281 00282 when others => 00283 rise_next_state <= rise_idle; 00284 00285 end case; 00286 end if; 00287 end process;

| PROCESS_135 | ( clk ) |

fall data

Definition at line 292 of file ddr2_mem_pattern_compare8.vhd.

00292 process(clk) 00293 begin 00294 if (clk = '1' and clk'event) then 00295 if (rst = '1') then 00296 clk_cnt_fall <= "0000"; 00297 elsif(fall_state = fall_first_data) then 00298 clk_cnt_fall <= clk_cnt_fall + "0001"; 00299 else 00300 clk_cnt_fall <= clk_cnt_fall; 00301 end if; 00302 end if; 00303 end process;

| PROCESS_136 | ( clk ) |

FSM state transitions.

Definition at line 306 of file ddr2_mem_pattern_compare8.vhd.

00306 process(clk) 00307 begin 00308 if (clk = '1' and clk'event) then 00309 if (rst = '1') then 00310 fall_state <= fall_idle; 00311 else 00312 fall_state <= fall_next_state; 00313 end if; 00314 end if; 00315 end process;

| PROCESS_137 | ( cntrl_rden_r , | |

| fall_state , | ||

| rd_data_fall_r , | ||

| rst ) |

FSM.

Definition at line 318 of file ddr2_mem_pattern_compare8.vhd.

00318 process(cntrl_rden_r, fall_state, rd_data_fall_r, rst) 00319 begin 00320 if(rst = '1') then 00321 fall_next_state <= fall_idle; 00322 else 00323 case (fall_state) is 00324 when fall_idle => 00325 if(cntrl_rden_r = '1') then 00326 fall_next_state <= fall_first_data; 00327 else 00328 fall_next_state <= fall_idle; 00329 end if; 00330 00331 00332 when fall_first_data => 00333 if((rd_data_fall_r = X"55") or (rd_data_fall_r = X"AA")) then 00334 fall_next_state <= fall_comp_over; --second_data 00335 else 00336 fall_next_state <= fall_first_data; 00337 end if; 00338 00339 when fall_second_data => 00340 if((rd_data_fall_r = X"66") or (rd_data_fall_r = X"99")) then 00341 fall_next_state <= fall_comp_over; 00342 else 00343 fall_next_state <= fall_first_data; 00344 end if; 00345 00346 when fall_comp_over => 00347 fall_next_state <= fall_comp_over; 00348 00349 when others => 00350 fall_next_state <= fall_idle; 00351 00352 end case; 00353 end if; 00354 end process;

The documentation for this class was generated from the following file: