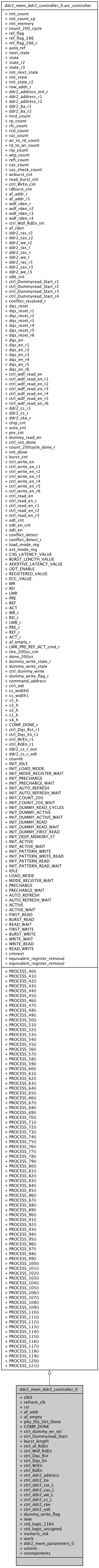

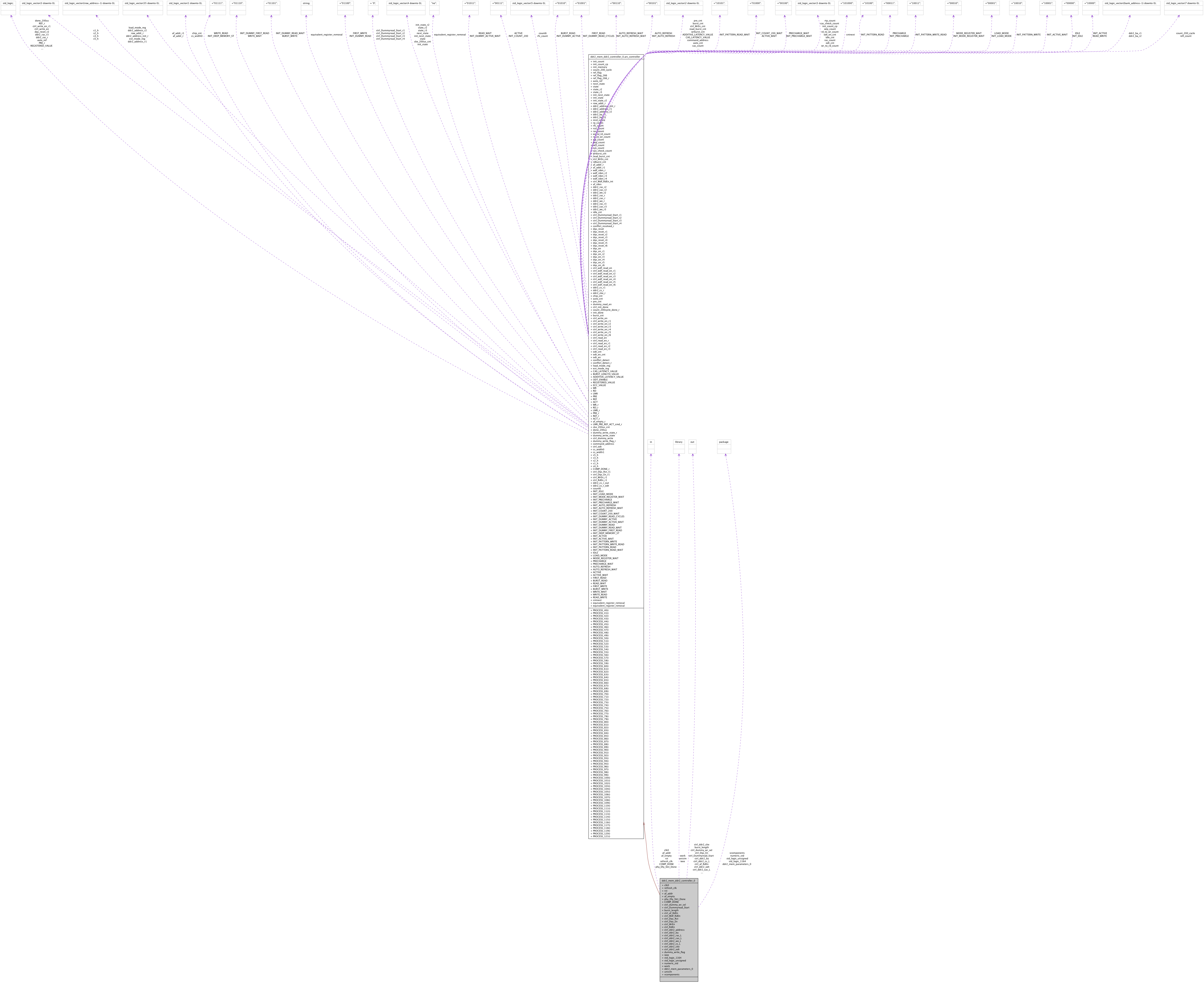

ddr2_mem_ddr2_controller_0 Entity Reference

Main RAM controller module. More...

Architectures | |

| arc_controller | Architecture |

| Main RAM controller module. More... | |

Libraries | |

| ieee | |

| standard IEEE library | |

| work | |

| unisim | |

| Library with Xilinx primitives. | |

Packages | |

| std_logic_1164 | |

| std_logic definitions, see file | |

| std_logic_unsigned | |

| unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file | |

| numeric_std | |

| arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file | |

| ddr2_mem_parameters_0 | Package <ddr2_mem_parameters_0> |

| vcomponents | |

| Header with Xilinx primitives. | |

Ports | |

| clk0 | in std_logic |

| Clock. | |

| refresh_clk | in std_logic |

| Refresh clock. | |

| rst | in std_logic |

| Reset. | |

| af_addr | in std_logic_vector ( 35 downto 0 ) |

| Address FIFO. | |

| af_empty | in std_logic |

| Addr FIFO empty flag. | |

| phy_Dly_Slct_Done | in std_logic |

| Input signal for the Dummy Reads. | |

| COMP_DONE | in std_logic |

| Input signal for the Dummy Reads. | |

| ctrl_dummy_wr_sel | out std_logic |

| Output signal for the Dummy Reads. | |

| ctrl_Dummyread_Start | out std_logic |

| Output signal for the Dummy Reads. | |

| burst_length | out std_logic_vector ( 2 downto 0 ) |

| Burst Length. | |

| ctrl_af_RdEn | out std_logic |

| FIFO read enable signals. | |

| ctrl_Wdf_RdEn | out std_logic |

| FIFO read enable signals. | |

| ctrl_Dqs_Rst | out std_logic |

| Rst and Enable signals for DQS logic. | |

| ctrl_Dqs_En | out std_logic |

| Rst and Enable signals for DQS logic. | |

| ctrl_WrEn | out std_logic |

| Read and Write Enable signals to the phy interface. | |

| ctrl_RdEn | out std_logic |

| Read and Write Enable signals to the phy interface. | |

| ctrl_ddr2_address | out std_logic_vector ( ( row_address-1 ) downto 0 ) |

| Memory address. | |

| ctrl_ddr2_ba | out std_logic_vector ( ( bank_address-1 ) downto 0 ) |

| Bank address. | |

| ctrl_ddr2_ras_L | out std_logic |

| RAS. | |

| ctrl_ddr2_cas_L | out std_logic |

| CAS. | |

| ctrl_ddr2_we_L | out std_logic |

| Write enable. | |

| ctrl_ddr2_cs_L | out std_logic |

| Chip select. | |

| ctrl_ddr2_cke | out std_logic |

| Clock enable. | |

| ctrl_ddr2_odt | out std_logic |

| On-Die termination. | |

| dummy_write_flag | out std_logic |

| Output signal for the Dummy Writes. | |

Detailed Description

Main RAM controller module.This module is the main control logic of the memory interface. All commands are issued from here acoording to the burst, CAS Latency and the user commands.

Definition at line 60 of file ddr2_mem_ddr2_controller.vhd.

Member Data Documentation

af_addr in std_logic_vector ( 35 downto 0 ) [Port] |

af_empty in std_logic [Port] |

burst_length out std_logic_vector ( 2 downto 0 ) [Port] |

clk0 in std_logic [Port] |

COMP_DONE in std_logic [Port] |

ctrl_af_RdEn out std_logic [Port] |

ctrl_ddr2_address out std_logic_vector ( ( row_address-1 ) downto 0 ) [Port] |

ctrl_ddr2_ba out std_logic_vector ( ( bank_address-1 ) downto 0 ) [Port] |

ctrl_ddr2_cas_L out std_logic [Port] |

ctrl_ddr2_cke out std_logic [Port] |

ctrl_ddr2_cs_L out std_logic [Port] |

ctrl_ddr2_odt out std_logic [Port] |

ctrl_ddr2_ras_L out std_logic [Port] |

ctrl_ddr2_we_L out std_logic [Port] |

ctrl_Dqs_En out std_logic [Port] |

ctrl_Dqs_Rst out std_logic [Port] |

ctrl_dummy_wr_sel out std_logic [Port] |

ctrl_Dummyread_Start out std_logic [Port] |

ctrl_RdEn out std_logic [Port] |

Read and Write Enable signals to the phy interface.

Definition at line 77 of file ddr2_mem_ddr2_controller.vhd.

ctrl_Wdf_RdEn out std_logic [Port] |

ctrl_WrEn out std_logic [Port] |

Read and Write Enable signals to the phy interface.

Definition at line 76 of file ddr2_mem_ddr2_controller.vhd.

dummy_write_flag out std_logic [Port] |

ieee library [Library] |

numeric_std package [Package] |

arithmetic functions use ieee.numeric_std.all; operators for signed use ieee.numeric_std.all; unsigned datatypes, see file

Definition at line 48 of file ddr2_mem_ddr2_controller.vhd.

phy_Dly_Slct_Done in std_logic [Port] |

refresh_clk in std_logic [Port] |

rst in std_logic [Port] |

std_logic_1164 package [Package] |

std_logic_unsigned package [Package] |

unsigned functions use ieee.std_logic_unsigned.all; operators for std_logic_vector type, see file

Definition at line 46 of file ddr2_mem_ddr2_controller.vhd.

unisim library [Library] |

vcomponents package [Package] |

The documentation for this class was generated from the following file: