ddr2_data_buffer.ddr2_data_buffer_arc Architecture Reference

Interface between DAQ & DDR2, buffer with circular addressing. More...

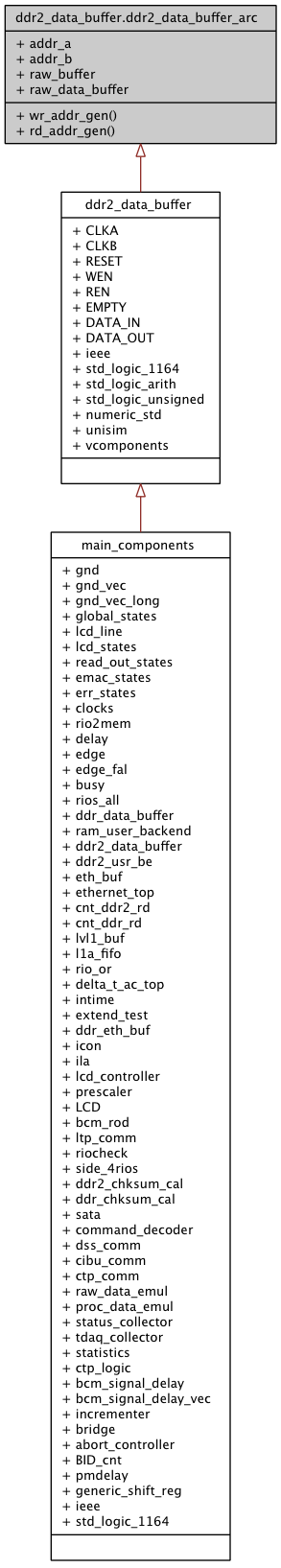

Inheritance diagram for ddr2_data_buffer.ddr2_data_buffer_arc:

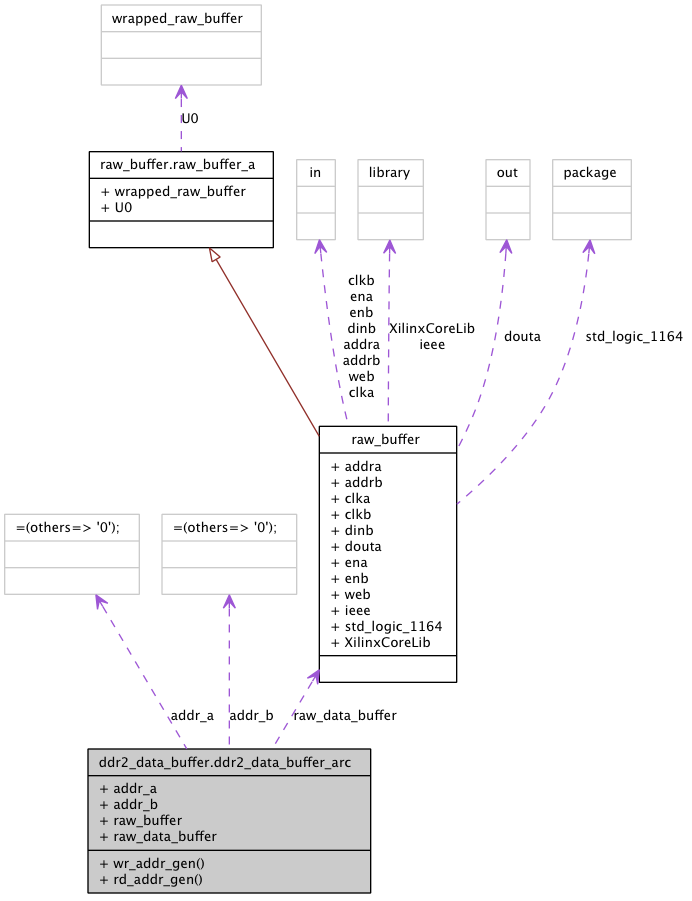

Collaboration diagram for ddr2_data_buffer.ddr2_data_buffer_arc:

Processes | |

| wr_addr_gen | ( CLKB ) |

| write address generation | |

| rd_addr_gen | ( CLKA ) |

Components | |

| raw_buffer | <Entity raw_buffer> |

| DPBRAM wrapper. | |

Signals | |

| addr_a | std_logic_vector ( 6 downto 0 ) := ( others = > ' 0 ' ) |

| addr_b | std_logic_vector ( 5 downto 0 ) := ( others = > ' 0 ' ) |

Component Instantiations | |

| raw_data_buffer | raw_buffer <Entity raw_buffer> |

| wrapped DPBRAM | |

Detailed Description

Interface between DAQ & DDR2, buffer with circular addressing.Definition at line 53 of file ddr2_data_buffer.vhd.

Member Function Documentation

| rd_addr_gen | ( CLKA ) |

read address generation uses the difference betw. read & write pointers to calculate fill-level

Definition at line 107 of file ddr2_data_buffer.vhd.

00107 rd_addr_gen : process(CLKA) 00108 variable diff_stack_point : integer := 0; 00109 begin 00110 if CLKA'event and CLKA = '1' then 00111 if RESET = '1' then 00112 addr_a <= (others => '0'); 00113 elsif REN = '1' then 00114 addr_a <= addr_a + 1; 00115 else 00116 addr_a <= addr_a; 00117 if addr_b >= addr_a then 00118 diff_stack_point := conv_integer(addr_b - addr_a); 00119 if diff_stack_point > 10 then 00120 EMPTY <= '0'; 00121 else 00122 EMPTY <= '1'; 00123 end if; 00124 else 00125 EMPTY <= '0'; 00126 end if; 00127 end if; 00128 end if; 00129 end process rd_addr_gen;

| wr_addr_gen | ( CLKB ) |

write address generation

Definition at line 91 of file ddr2_data_buffer.vhd.

00091 wr_addr_gen : process(CLKB) 00092 begin 00093 if CLKB'event and CLKB = '1' then 00094 if RESET = '1' then 00095 addr_b <= (others => '0'); 00096 elsif WEN = '1' then 00097 addr_b <= addr_b + 1; 00098 else 00099 addr_b <= addr_b; 00100 end if; 00101 end if; 00102 end process wr_addr_gen;

Member Data Documentation

raw_buffer [Component] |

raw_data_buffer raw_buffer [Component Instantiation] |

The documentation for this class was generated from the following file: